在所有低頻振蕩器配置中,維也納電橋是最容易使用的。它可靠,使用標準元件,提供良好的正弦波,并且相當不受設計所圍繞的運算放大器類型的影響。然而,維也納橋可能會被誤解和過度簡化,導致設計師感到沮喪。本文介紹了使用維恩橋振蕩器的理論和實用性,以及如何使電路更穩定,更靈活。

維也納橋振蕩器電路

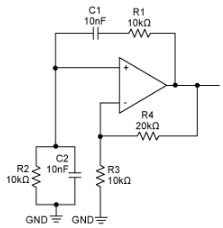

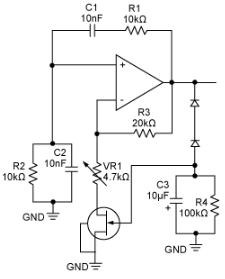

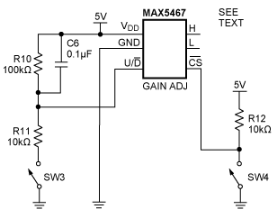

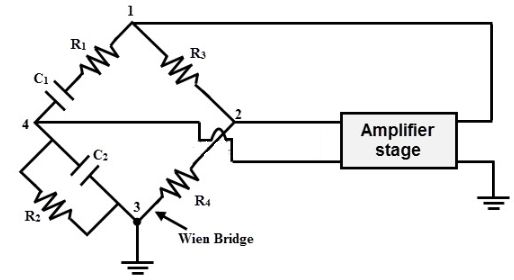

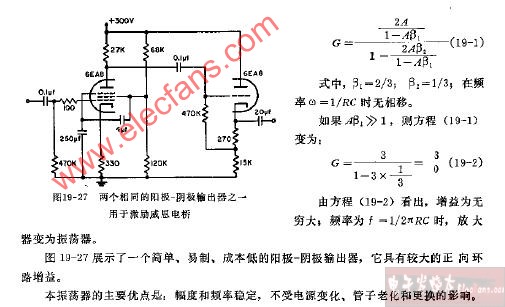

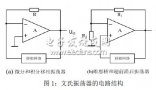

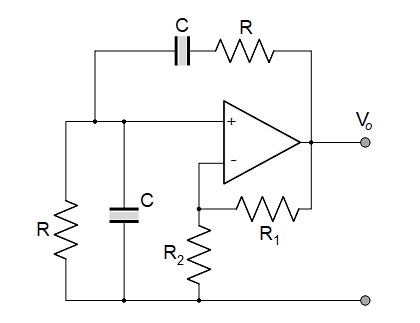

標準維恩橋振蕩器的電路如圖1所示。

圖1.標準維恩橋振蕩器電路。

當振蕩頻率處的環路增益為單位,并且振蕩頻率處反饋信號的相移為零或2π的倍數時,電路保持振蕩。

首先,需要考慮相移。在圖1中,R1和C1相對于輸出電壓產生正相移電流。當該移相電流與R2和C2相遇時,后一種成分會產生負相移電壓。在特定頻率下,R1和C1引起的相移被R2和C2引起的相移抵消,因此凈相移為零。發生這種情況時,電路有振蕩的危險。

接下來,我們考慮由 R1、C1、R2 和 C2 組成的網絡的傳遞函數。由于運算放大器的輸出阻抗較低,且兩個輸入端的阻抗都非常高,因此確定Wien網絡的傳遞函數(即,由頂部的R1和C1組成,底部由R2和C2組成的電阻分壓器)相對簡單。因此,傳遞函數為:

傳遞函數為:

其中 j 表示傳遞函數中的 90 度相移(正或負)。其他(非“j”)項表示傳遞函數中的零相移。隨著項的大小變化,由此產生的相移也會發生變化。等式1顯示分母中的“非j”項等于零,分子和分母中僅剩j項。

將分子和分母除以 JW 不會留下 j 項,因此不會產生相移。因此,公式2計算了給定頻率下零相移的條件。

接下來,必須考慮收益。一旦解析了公式1中的項并確定了諧振頻率,傳遞函數為:

為了簡化這一點,明智的做法是將 R1 等同于 R2,將 C1 等同于 C2。由此可見,在諧振時,從輸出到輸入的傳遞函數為:

為了滿足振蕩要求(即零相移和單位增益),運算放大器電路需要具有3的增益,以克服Wien橋網絡引起的衰減。從另一個角度來看,為了使兩個運算放大器輸入保持相同的電壓,從輸出到反相輸入的電阻網絡需要提供3的衰減,以匹配Wien網絡的衰減。

從理論上講,這種技術非常方便,但不實用。低容差電阻可輕松包含在設計中。然而,找到精確的電容器更加困難,并且包括精度大于20%的電容器可能成本高昂。因此,明智的做法是考慮不同電容值對電路性能的影響。

圖2顯示了一個簡單的電子表格,說明了Wien橋網絡的值及其對增益的影響。單元格B7是公式3中表示的傳遞函數,單元格B12由公式2確定(答案以kHz為單位),單元格B9是單元格B7的倒數。如果C1 = C2 = 10nF且R1 = R2 = 10kΩ,則電路振蕩頻率為1.59kHz,運算放大器增益等于3。該電路的實際測量支持這種計算。

圖2.維也納橋組件值示例。

然而,上述結果是在容限為±10%的電容器上實現的。快速檢查元件目錄會發現,設計用于去耦的電容器非常相似,其容差為 -20%/+80%。在這種情況下,當C1 = 8nF (10nF -20%)和C2 = 18nF (10nF + 80%)時,電路需要4.25的增益。將這些元件插入設計會導致電路增益不足(僅提供3的增益)。因此,電路不會振蕩。或者,如果C1為高電平,C2為低電平,則電路增益過大并振蕩,但失真顯著。此外,一旦電路振蕩,由于電容值的容差很寬,頻率就會不正確。理想的電路是偏置到振蕩點的電路。增益越小,電路就會停止振蕩;任何更多的收益,它開始扭曲。

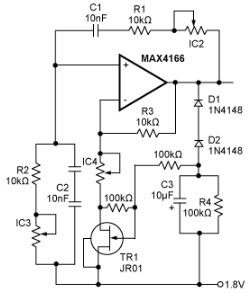

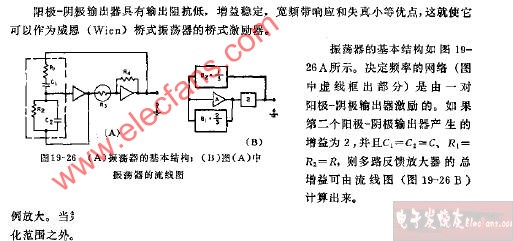

如圖3所示,反饋網絡中的JFET解決了這個問題。使用JFET時,增益可以在很小的范圍內變化,以確保一致的振蕩。啟動時,JFET 柵極電壓為零;因此,漏源阻抗非常低。這種設計產生的增益大于3(以使電路正常工作)。一旦振蕩累積,輸出的整流負轉換將為JFET的柵極提供關斷電壓。這會降低增益,電路穩定下來穩定振蕩。輸出幅度取決于兩個二極管兩端的壓降,以及JFET的關斷電壓。遺憾的是,JFET的柵極關斷電壓變化很大,這導致電路的輸出電壓因批次而異。之所以選擇TR1,是因為它的柵極關斷電壓變化非常小,從而保證了電路之間輸出電壓的微小變化。但該TR1電路通常不會產生失真最低的振蕩器。事實上,電路振蕩,但失真明顯;無論失真如何,JFET 都能保持這種振蕩。因此,JFET只能用作保持電路運行的輔助工具,而不是補償不良的電路設計。

圖3.在反饋網絡中帶有結柵場效應晶體管(JFET)的維也納橋振蕩器。

除非可以容忍復雜的電路設計,否則確保電路啟動并繼續振蕩而不會失真(由于增益過大)的最簡單方法是在反饋路徑中插入一個可變電阻。然后將電阻調整到電路剛開始振蕩的點。這提供了失真最低的干凈正弦波。

盡管一些工程師認為可變電阻器是一種簡單的設計解決方案,但制造工程師認為這是一個耗時的生產難題。調整可變電阻需要時間和人力,使電路復雜且生產成本高昂。

解決這一困境的理想解決方案是插入一個電子可變電阻器或數字電位器(digipot)。在圖3中,用數字電位器代替可變電阻VR1提供了一種低成本、小型、簡單的解決方案,可以在生產過程中調整電路,以確保最小的失真。該數字電位器可以單獨使用,也可以與其他電阻串聯或并聯使用,以微調增益。一旦電路振蕩,JFET就會提供精細的增益修改,使電路保持運行。

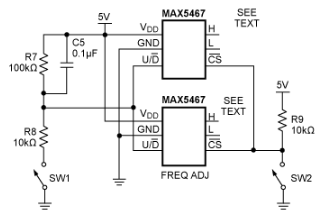

在圖3所示電路中,MAX5467 10kΩ數字電位器可以代替可變電阻VR1。由于該部件具有兩個浮動端子,因此不必以地面為參考。插入額外的MAX5467器件與R1和R2串聯,使用戶能夠調整電路的頻率。數字電位器具有簡單的數字接口,這意味著無需微控制器即可手動調整電路。

將兩個10kΩ數字電位器與電阻R1和R2串聯插入,電路的工作頻率可在833Hz至1.6kHz范圍內調節。此外,一旦插入10kΩ數字電位器代替VR1,電路的輸出就可以隨著電路增益的變化從直流到純正弦波和失真正弦波進行電子調節。

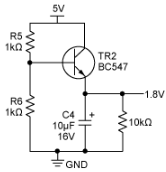

圖4所示為最終電路,包括MAX5467數字電位器。圖5所示為交流接地和JEFT偏置電路。圖6和圖7分別顯示了頻率和增益調整電路。數字電位器由符號IC2,IC3和IC4表示。IC2和IC3共享相同的數字接口,因此可以同時遞增和遞減。IC4提供獨立的增益調整電路。

為了進一步線性化JFET的特性,在柵極周圍增加了兩個100kΩ電阻。這些電阻為JFET提供一些負反饋,從而平滑JFET性能的非線性。

圖4.在反饋網絡中帶有JFET和數字電位器的維恩橋振蕩器。

圖5.交流接地和JFET偏置電路。

圖6.采用MAX5467的頻率調整電路。

圖7.采用MAX5467的增益調節電路

進一步實驗

本文分析了維恩橋振蕩器的要點以及許多振蕩器設計的基礎知識。如果沒有正確掌握基礎知識,在維也納橋周圍添加的任何電路都只會掩蓋錯誤。

但是,可以通過更仔細地檢查電路并添加額外的電路來進一步提高性能來進行改進。

反饋環路會導致失真。二極管正向電壓隨溫度漂移(2.1mV/°C)。這直接影響輸出電壓。此外,JFET偏置電壓隨溫度變化。這些電壓漂移可以通過在輸出端增加RMS-DC轉換器或峰值電平檢波器來克服。這種電路需要產生與正弦波輸出成比例的精確直流輸出電壓。如果該直流信號反相(使用簡單的運算放大器電路)并直接饋送到JFET輸入端,則可以使正弦波輸出更加穩定。

結論

維恩橋振蕩器在理論上很容易理解,但電路的實用性可能會使設計人員感到沮喪。在電路的三個關鍵區域插入數字電位器可確保更穩定的操作和工廠/用戶的可調節性。

審核編輯:郭婷

-

振蕩器

+關注

關注

28文章

3814瀏覽量

138912 -

運算放大器

+關注

關注

215文章

4900瀏覽量

172608

發布評論請先 登錄

相關推薦

使用運算放大器的維恩橋振蕩器設計

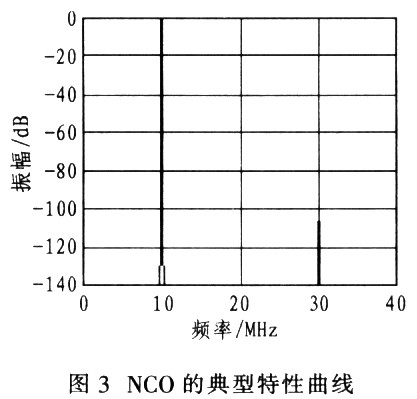

基于FPGA的數控振蕩器原理及設計方法

無信號源的自激式激磁電源的原理及設計 (采用維恩電橋振蕩器)

基于FPGA和SRAM的數控振蕩器的設計與實現

數控維恩橋振蕩器的分析

數控維恩橋振蕩器的分析

評論