作者:Steven Xie, Karl Wei, and Claire Croke

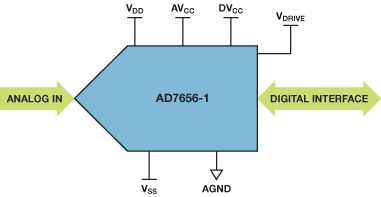

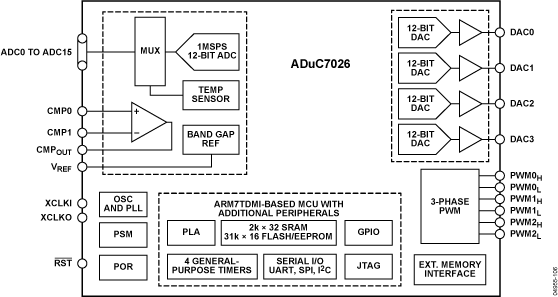

高壓開關(guān)、雙極性ADC和其他具有多個電源的器件通常需要按特定順序施加或移除電源電壓。本文提出了一種簡單、經(jīng)濟高效的方法,用于確定系統(tǒng)在受到電源瞬變、中斷或序列變化時的行為。采用多個電源的器件示例是AD7656-1(表1),這是一款16位、250 kSPS、6通道、同步采樣、雙極性輸入ADC。ADuC7026精密模擬微控制器的四個12位DAC提供DUT的可編程電源電壓。使用AD7656-1評估板和ADuC7026評估板,只需進行最少的硬件和軟件開發(fā)即可完成原型設(shè)計。

表 1.AD7656-1 典型電源電壓和最大電源電流

| Supply | AVCC, DVCC | VDRIVE | VDD | VSS |

| 電壓 | 5 |

3.3 |

10 | –10 |

| 電流(毫安) | 30 | 10 | 0.25 | 0.25 |

表1顯示了每個ADC電源的典型電壓和最大電流。ADuC7026上的四個DAC產(chǎn)生的可編程時序可控電壓波形由AD7656-1評估板上的超低噪聲和失真運算放大器AD797進行縮放,以提供指定的電源電壓和電流。微控制器的速度和可編程性有助于控制電源電壓的電壓電平、周期、脈沖寬度和斜坡時間。

例如,使用外部電源,AD7656-1評估板上的AD797放大器(配置為增益為5)可以產(chǎn)生0 V至12.5 V的電壓范圍,以驅(qū)動ADC的VDD供應軌。AD797的高輸出驅(qū)動能力允許為每個電源軌提供高達50 mA的電流。圖1顯示了與ADC的連接。

圖1.AD7656-1 連接圖

ADuC7026 DAC數(shù)據(jù)寄存器可通過41.78 MHz內(nèi)核時鐘以7 MHz頻率更新,從而最大限度地提高電壓更新速率。以下部分介紹開發(fā)過程,并提供使用評估板獲得的測量結(jié)果。

硬件開發(fā)和設(shè)置

ADuC7026評估板上的四個DAC輸出引腳和AGND分別連接到AD7656-1評估板上的四個AD797輸入和AGND。安捷倫 E3631A 外部電源模塊為 AD797 提供 ±15 V。通過USB連接到ADuC7026評估板的計算機提供5 V電源和串行通信。

原理圖設(shè)計

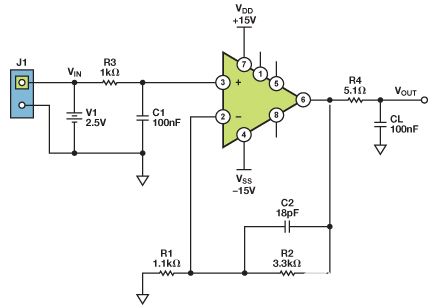

AD7656-1評估板上唯一需要的硬件更改與AD797有關(guān)。可以根據(jù)不同的增益和帶寬要求選擇R1和R2。圖3顯示AD797設(shè)置為增益= 4,以便從ADuC7026 DAC的0 V至2.5 V輸出提供0 V至10 V輸出。R3和C1形成一個低通濾波器,以降低高頻噪聲。CL用作電源軌上的負載電容器。

圖3.AD797原理圖設(shè)計,增益=4。

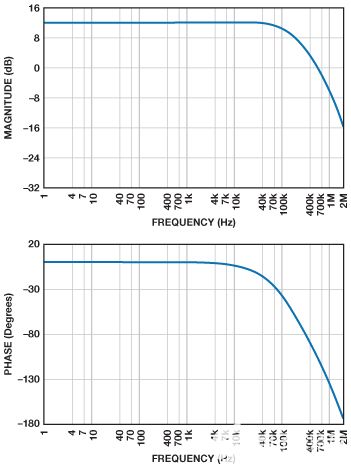

圖4顯示了AD797在增益= 4時的頻率響應,從NI 多 SIM 卡?模擬。1.0MHz 帶寬和 73° 相位裕量可提供快速瞬態(tài)響應和穩(wěn)定運行。

圖4.AD797的頻率響應,增益=4。

AD797 設(shè)計筆記

超低失真、超低噪聲運算放大器AD797具有80 μV最大失調(diào)電壓、出色的直流精度、800 ns建立至16位、50 mA輸出電流和±13 V輸出擺幅(采用±15 V電源供電),非常適合驅(qū)動電源軌。

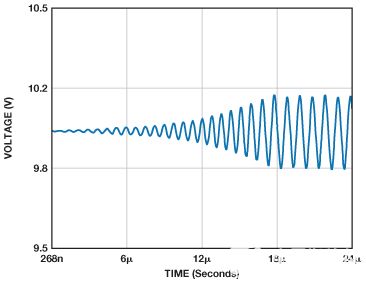

不過,它不會針對大量容性負載進行內(nèi)部補償,因此必須使用外部補償技術(shù)來優(yōu)化此應用。圖5顯示了驅(qū)動容性負載引起的AD797輸出振蕩。

圖5.無補償振蕩。

為了在電源軌上具有容性負載的情況下穩(wěn)定驅(qū)動,電阻R4放置在輸出和負載之間。該電阻將運算放大器輸出和反饋網(wǎng)絡與容性負載隔離開來,并在反饋網(wǎng)絡的傳遞函數(shù)中引入零點,從而降低更高頻率下的相移。1反饋電容C2補償運算放大器輸入端的容性負載,包括C1。

應用DAC

ADuC7026精密模擬微控制器具有四個12位電壓輸出DAC,具有軌到軌輸出緩沖器、三個可選范圍和10 μs建立時間。

每個DAC具有三個可選范圍:0 V至VREF(內(nèi)部帶隙2.5 V基準電壓源),0 V至DACREF(0 V至AVDD),和 0 V 至 AVDD.范圍使用控制寄存器 DACxCON 設(shè)置。DAC接受0 V至AV范圍的外部基準電壓源DD.使用內(nèi)部基準電壓源時,必須從VREF引腳連接到AGND,以確保穩(wěn)定性。

四個DAC中的每一個都可以通過控制寄存器DACxCON和數(shù)據(jù)寄存器DACxDAT獨立配置。一旦通過DACxCON寄存器配置了DAC,就可以將數(shù)據(jù)寫入DACxDAT以獲得所需的輸出電壓電平。

四個DAC輸出很容易使用C或匯編語言進行控制。此C代碼示例展示了如何選擇內(nèi)部2.5 V基準電壓源并將DAC0輸出設(shè)置為2.5 V。

將內(nèi)部 2.5 V 基準連接到 VREF 引腳

REFCON = 0x01;

//enable DAC0 operation

DAC0CON = 0x12;

//update DAC0DAT register with data 0xFFF

DAC0DAT = 0x0FFF0000;

Using assembly language,

DAC0CON[5] 被清除以使用內(nèi)核時鐘 (41.78 MHz) 更新 DAC0 以實現(xiàn)快速更新速率;

DAC0CON[1:0] 設(shè)置為“10”以使用 0 V 至 VREF (2.5 V) 輸出范圍

“DAC0DAT = 0x0FFF0000”可以通過兩個指令編譯為匯編代碼:

MOV R0, #0x0FFF0000

STR R0, [R1, #0x0604]

這兩個指令總共需要六個時鐘周期來執(zhí)行,對應于 7 MHz 更新速率和 41.78 MHz 內(nèi)核時鐘頻率。因此,電壓軌之間的時間延遲可以精確到144 ns。

測量結(jié)果

ADuC7026中的四個DAC為AD7656-1提供四個電源,以測試其在電源瞬變或時序變化下的行為。表2顯示了ADC的電源和電壓電平。

表 2.AD7656-1電源

| 數(shù)字轉(zhuǎn)換器通道 |

DAC0 |

數(shù)字轉(zhuǎn)換器1 |

DAC2 |

DAC3 |

| 輸出范圍 | 0 V 至 1.250 V | 0 V 至 0.825 V | 0 V 至 2.500 V | 0 V 至 2.500 V |

| AD797 增益 | 4 | 4 | 5 |

–5 |

| AD797 輸出擺幅 | 0 V 至 5.00 V | 0 V 至 3.30 V | 5.00 V 至 12.50 V |

–12.50 V 至 –5.00 V |

| 標稱電壓 | 5.00 伏 | 3.30 伏 | 10.00 伏 | –10.00V |

| AD7656-1 電源 | AVCC, DVCC | VDRIVE | VDD | VSS |

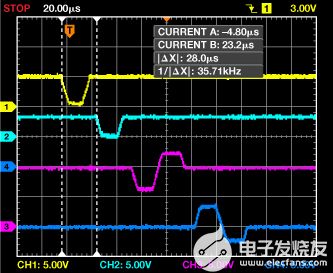

如表2所述,來自四個DAC輸出的波形是使用示波器捕獲的,如圖6所示。每個通道的電壓電平、周期、脈沖寬度和斜坡時間都是可編程的,易于控制。具體參數(shù)在以下各節(jié)中測量和描述。

圖6.四通道電壓波形。

為了達到每個電源的精確電壓電平,圖3中的R1可以使用可調(diào)電阻。通過使用安捷倫 34401A 數(shù)字萬用表調(diào)節(jié) R1 來校準電壓電平。

測量上升和下降斜坡時間以確定電壓波形的最大頻率。斜坡時間與電阻R4的值和容性負載CL有關(guān)。對于較慢的斜坡時間,R4和CL可以使用較大的電阻和電容值。AV的上升和下降斜坡時間抄送和DV抄送用不同的負載電容進行測試,結(jié)果如表3所示。使用1 μF電容時的上升波形如圖7所示。斜坡時間在10 V的10%至90%之間測量。

表 3.容性負載時的斜坡時間

| 容性負載 | 10 nF (V/μs) | 0.1 μF (V/μs) | 1 μF (伏/微秒) | 10 μF (V/μs) |

| 上升邊緣 | 6.90 | 0.97 | 0.07 | 0.01 |

| 落沿 | 5.71 | 0.93 | 0.06 | 0.01 |

圖7.1μF 容性負載下的上升時間。

電源紋波

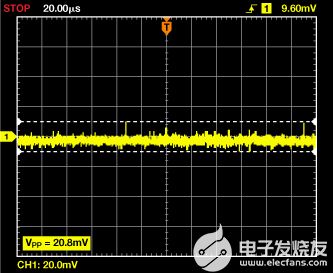

AD797具有出色的直流精度,可通過調(diào)節(jié)反饋電阻R1輕松為AD7656-1提供精確的標稱電壓電平。電源的峰峰值紋波是在標稱電壓電平下測量的,標稱電壓水平為200 MHz和20 MHz帶寬,容性負載為0.1 μF,采用DS1204B示波器。表4顯示紋波小于標稱電壓的1%,因此四個電源均符合要求。

表 4.每個電源的紋波

| Power Supply | AVCC, DVCC (5.00 V) | VDRIVE (3.30 V) | VDD (10.00 V) | VSS (–10.00 V) |

| 200 MHz (mV) | 20.8 | 28.0 | 25.6 | 30.4 |

| 20 MHz (mV) | 12.8 | 24.8 | 15.2 | 18.4 |

圖8.AVCC 和 DVCC 上的 5V 電源紋波。

生成波形

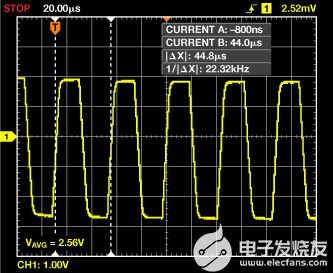

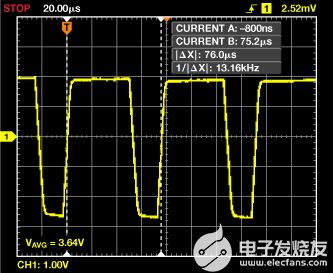

只需對ADuC7026源代碼進行簡單修改,就可以為需要評估不同電源條件下器件工作情況的各種不同應用生成許多不同的電壓波形序列。可以生成的典型波形如圖9和圖10所示。

圖9.22.32 kHz 方波。

圖 10.13.16 kHz 脈沖波形。

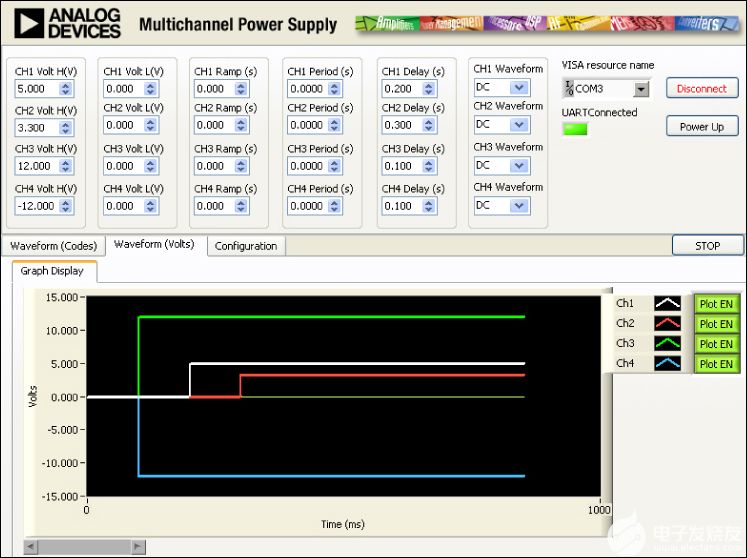

圖 11 中 顯示 的 LabVIEW GUI 可用于 生成 電源 波形。四個通道的電壓電平、斜坡時間、周期和序列延遲時間易于配置。串行端口用于GUI和ADuC7026之間的通信。

圖 11.電源配置圖形用戶界面。

結(jié)論

使用AD7656-1和ADuC7026評估板開發(fā)并驗證了一種簡單、經(jīng)濟高效的方法來評估電源排序的影響。ADuC7026評估板為四個電源生成一個可控的可編程序列,以評估ADC在不同電源時序/斜坡條件下的工作情況。微控制器中的三相16位PWM發(fā)生器可提供總共七個電壓通道。

審核編輯:郭婷

-

微控制器

+關(guān)注

關(guān)注

48文章

7487瀏覽量

151044 -

電源

+關(guān)注

關(guān)注

184文章

17578瀏覽量

249483 -

adc

+關(guān)注

關(guān)注

98文章

6430瀏覽量

544078

發(fā)布評論請先 登錄

相關(guān)推薦

aduc7026做I2C slave,接收數(shù)據(jù)存在的疑問求解

一個基于ADuC7026實現(xiàn)功率放大器監(jiān)控的參考設(shè)計

基于ADuC7026的網(wǎng)絡化數(shù)據(jù)采集系統(tǒng)設(shè)計

ADuC7023/ADuC7024/ADuC701925/ADuC7026中文資料

ADuC7026提供可編程電壓,用于評估多電源系統(tǒng)

ADUC7026 精密模擬微控制器,12位模擬I/O,ARM7TDMI? MCU

EVAR-ADC7026 ADUC7026/27 QUICKSTART和QUICKSTART PLUS開發(fā)

ADuC7026提供可編程電壓用于評估多個電源系統(tǒng)

ADuC7026提供可編程電壓用于評估多個電源系統(tǒng)

評論