PCB布局是優(yōu)化高速板線性度性能的關(guān)鍵因素。 本系列的前幾篇文章討論了減少二次諧波失真的一些基本技術(shù)。 這篇文章,靈感來自TI文檔”高速印刷電路板布局技術(shù)“,試圖詳細討論如何在高速差分ADC驅(qū)動器中布置軌到軌和軌到地旁路電容,以實現(xiàn)最大可能的線性度性能。

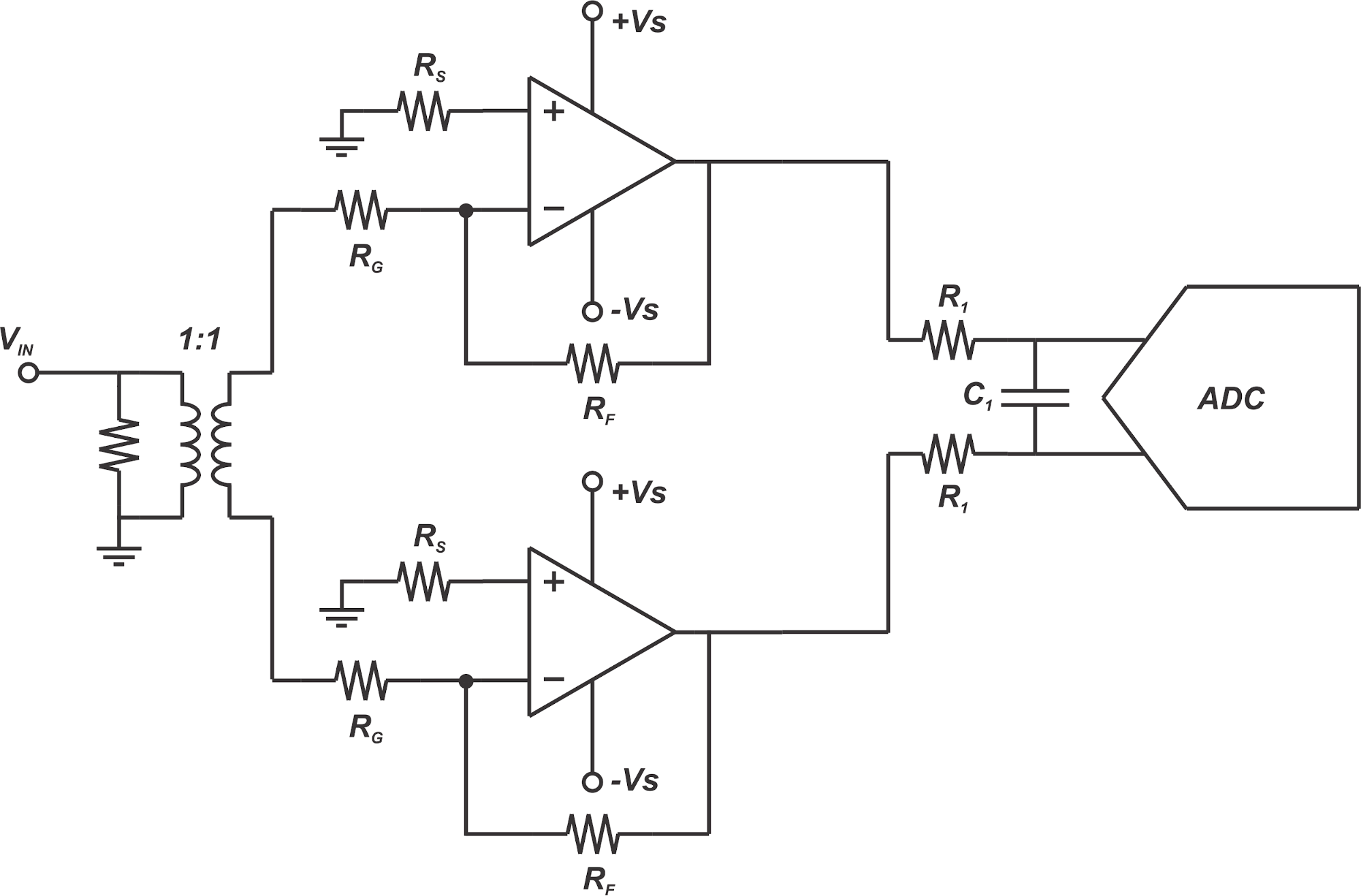

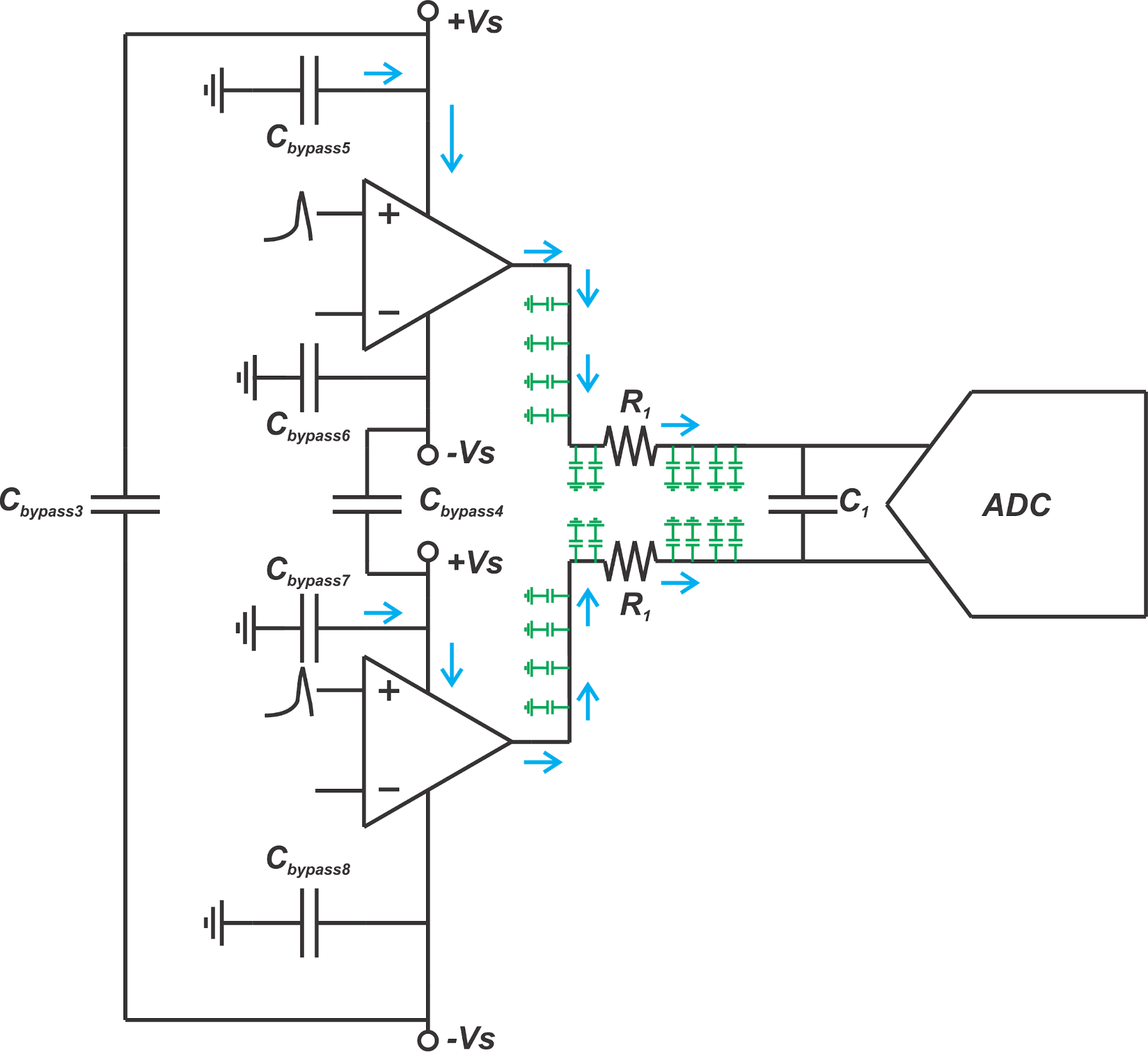

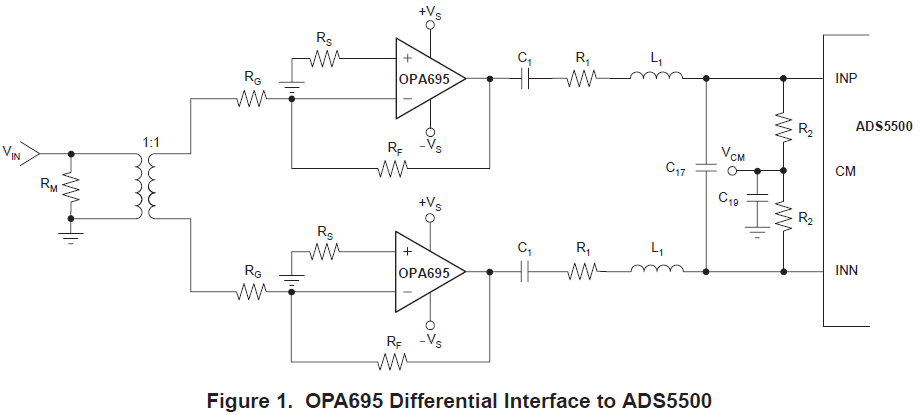

如圖1所示,差分ADC驅(qū)動器可通過采用兩個單端運算放大器來實現(xiàn)。

圖1. 使用兩個相同的單端運算放大器實現(xiàn)差分ADC驅(qū)動器

將差分信號施加到這些相同的路徑上時,各個運算放大器將產(chǎn)生相同的二次諧波分量。 這些失真分量在ADC輸入端顯示為共模信號,與任何其他共模噪聲和干擾信號一樣,差分ADC將抑制這些失真分量。

在上一篇文章中,我們討論了對稱印刷電路板布局需要保持兩條單端路徑相同并衰減二次諧波。 在本文中,我們將討論如何布置運算放大器的去耦電容,以實現(xiàn)最大可能的線性度性能。

我們知道 去耦電容器充當電荷源 并提供運算放大器應向負載提供的高頻電流。 為了提供高頻差分電流,我們可以使用軌對地和軌到軌去耦電容器。

軌到軌與軌到地面解耦結(jié)構(gòu)

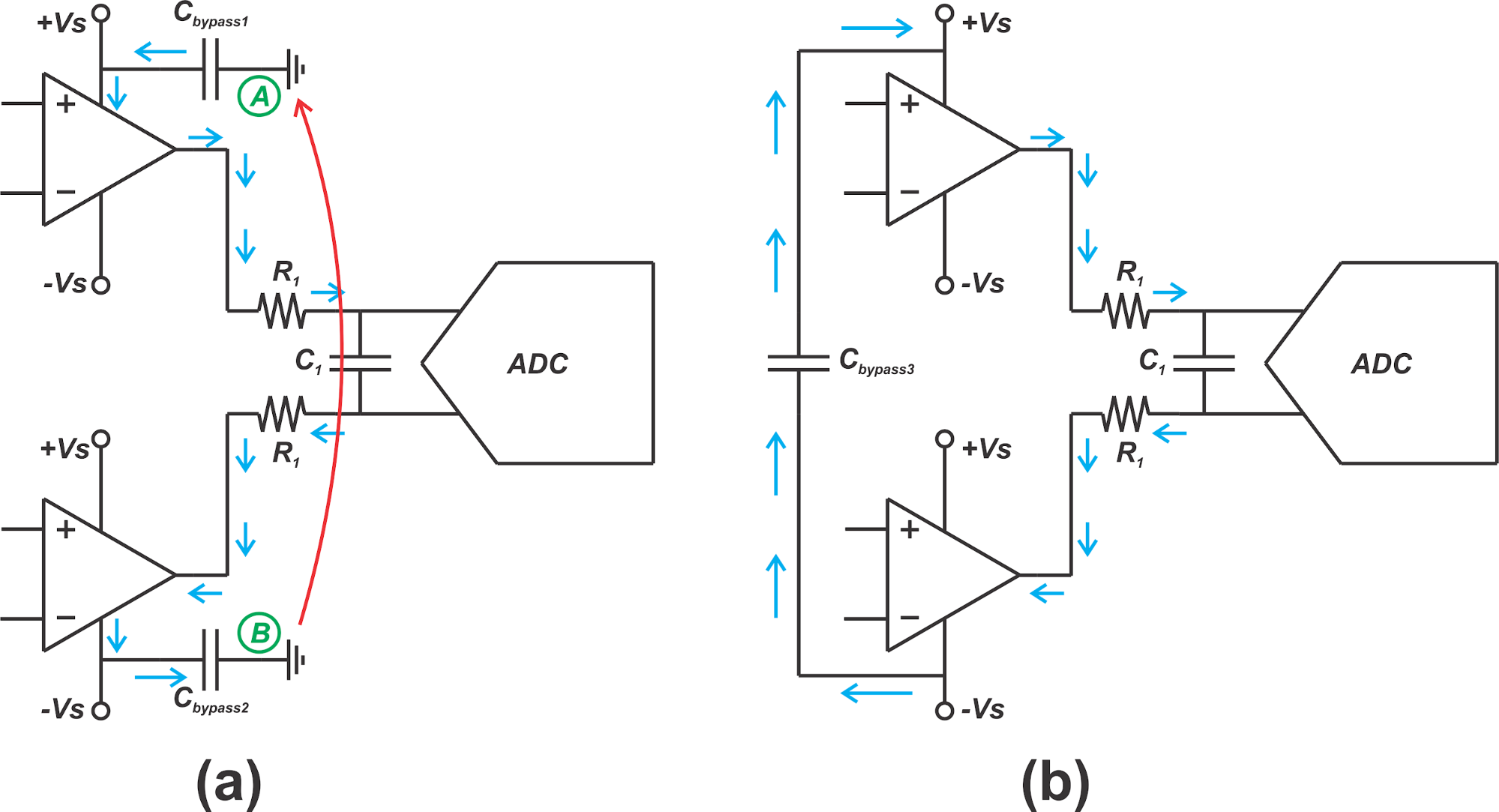

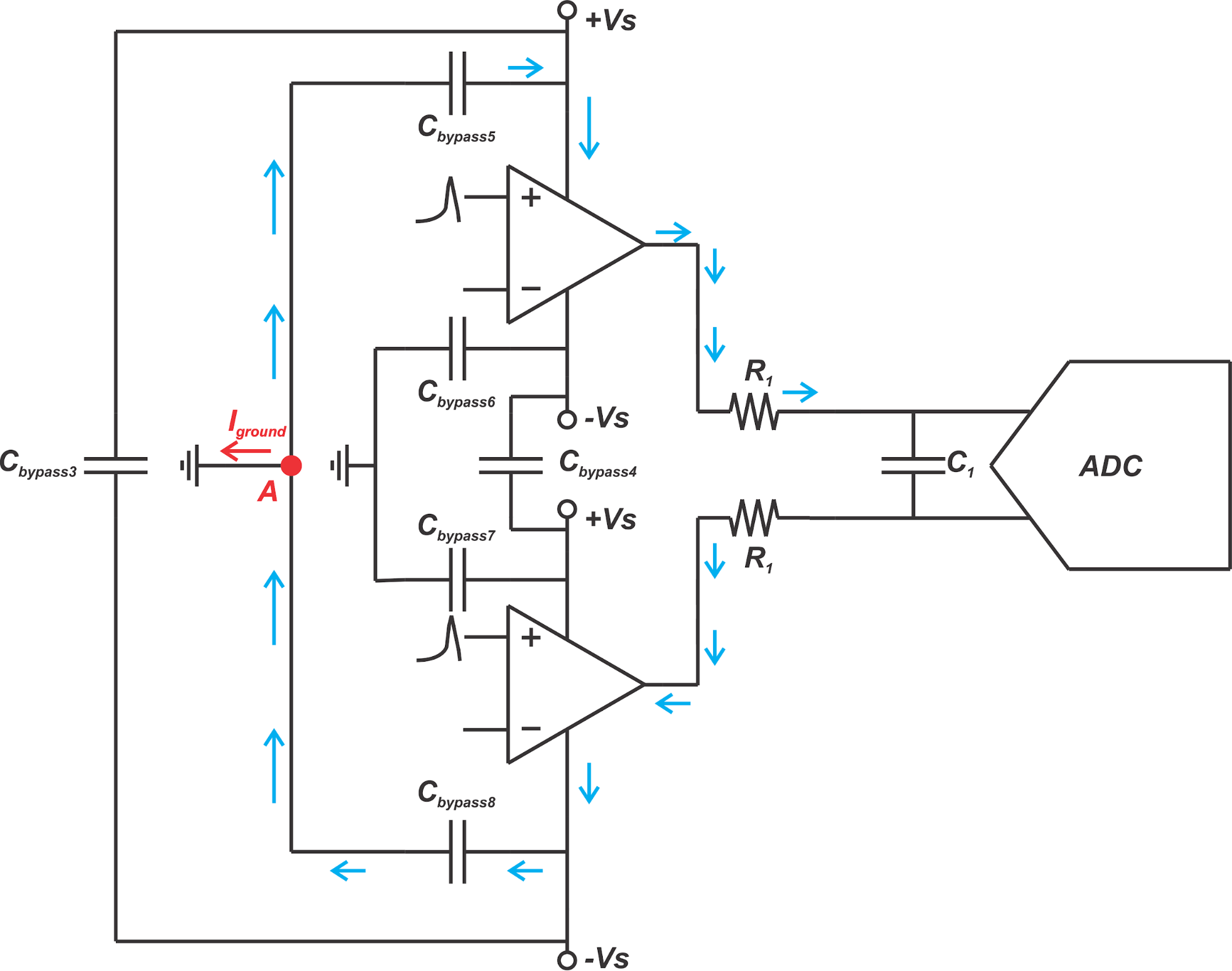

采用圖1所示結(jié)構(gòu),輸送到負載的電流是差分的,即當上部運算放大器向負載提供電流時,下部支路吸收電流,反之亦然。 讓我們考慮一下上部運算放大器提供負載電流,而下部路徑吸收負載電流的情況。 軌對地和軌到軌去耦選項以及電流路徑如圖2所示。 請注意,為簡單起見,本圖中未顯示放大級的電阻。 此外,我們假設采用具有專用接地層的多層板。

圖2. 軌對地 (a) 和軌到軌 (b) 去耦結(jié)構(gòu)

采用軌對地去耦結(jié)構(gòu)(圖2(a)),高頻電流將從正電源軌(C旁路1) 到負載,然后到負軌的旁路電容器 (C旁路2)如藍色箭頭所示。 電路原理圖暗示節(jié)點A和B都位于地面,藍色箭頭所示的路徑是電流的閉合路徑。 然而,實際上,節(jié)點A和B是接地層上的兩個不同節(jié)點,電流應該從節(jié)點B流向節(jié)點A,以獲得閉合的電流路徑。 因此,負載電流將通過接地層提供的阻抗最小的路徑流回C的接地側(cè)旁路1.

這種結(jié)構(gòu)的挑戰(zhàn)在于,在接地層中流動的任何足夠接近負載電流返回路徑的電流都可以與負載電流耦合并改變它。 此外,如果負載電流返回路徑從節(jié)點B到A出現(xiàn)任何不對稱,ADC驅(qū)動器的單端路徑之間的對稱性將受到影響,ADC輸入端將出現(xiàn)更大的二次諧波。

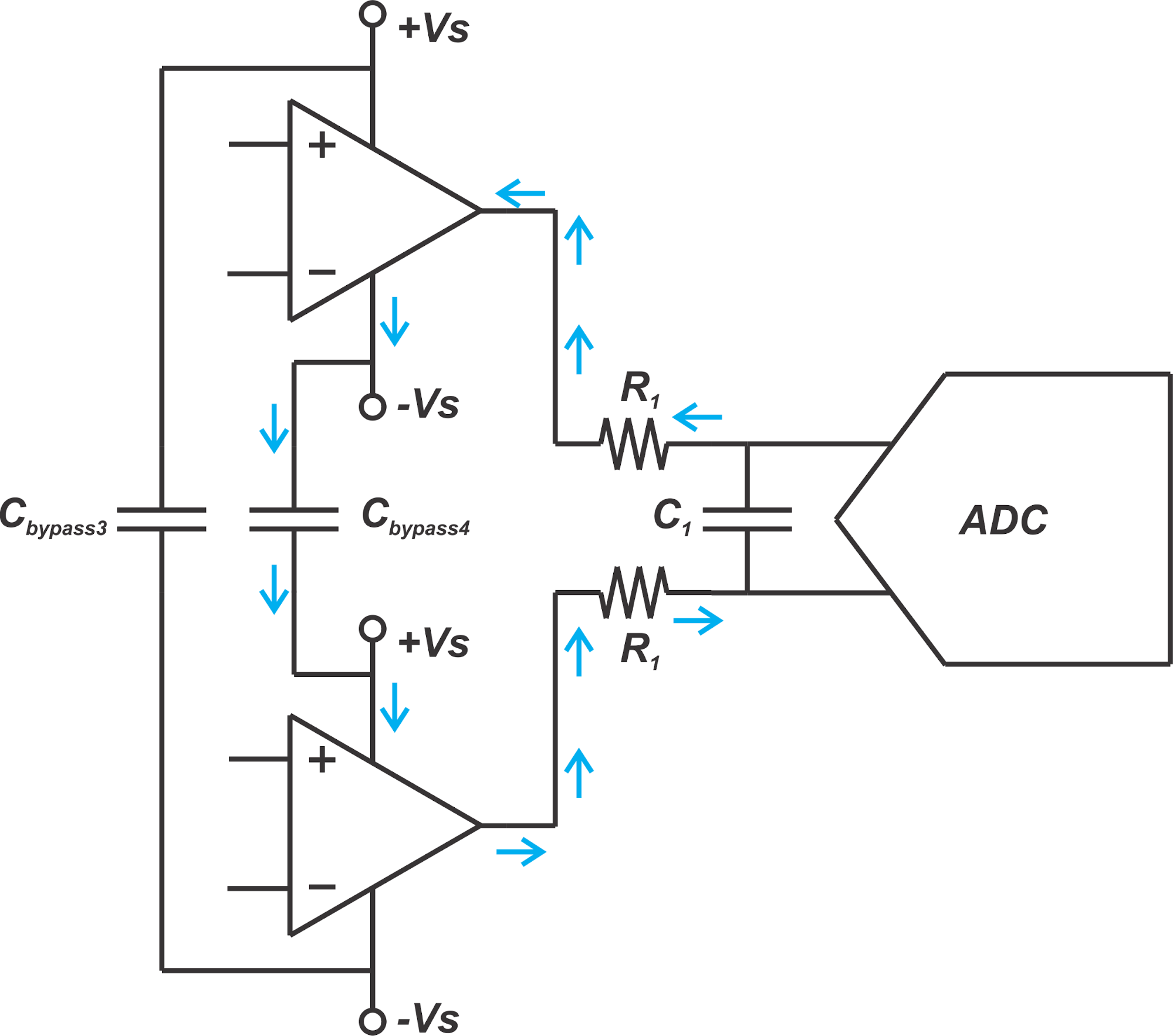

為了避免這些問題,可以采用圖2(b)中的去耦結(jié)構(gòu),在兩個電源軌之間放置一個旁路電容。 這樣,差分負載電流將沿著藍色箭頭所示的路徑流動,而不必流過接地層。 根據(jù)TI 文檔,軌到軌旁路電容器可將二次諧波失真降低6至10dB。 請注意,為了提供相反方向的差分負載電流,我們需要包括另一個軌到軌旁路電容(C旁路4) 如下圖 3

所示。

圖3

C 提供的負載電流路徑旁路4 由藍色箭頭顯示。

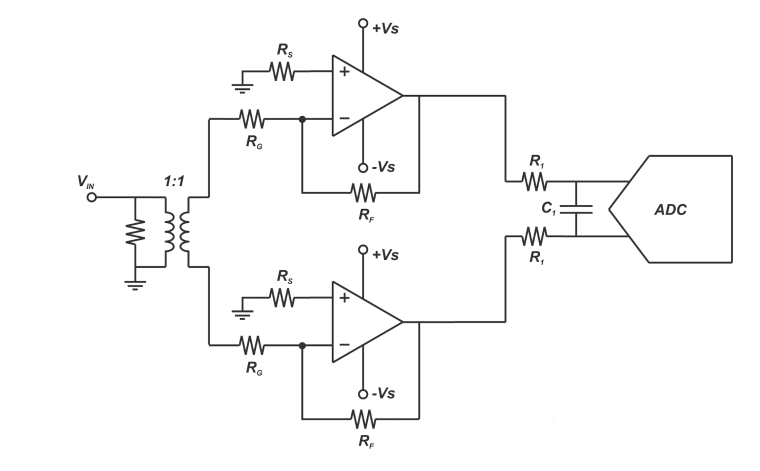

共模電流呢?

采用圖1所示結(jié)構(gòu),運算放大器提供的電流主要是差分電流,可由軌到軌去耦電容提供。 但是,我們?nèi)匀豢梢允褂眯〉墓材k娏髟?例如,假設噪聲分量耦合到兩個運算放大器的同相輸入,并略微提高這些節(jié)點的電壓。 這將產(chǎn)生從兩個運算放大器流出的共模電流。 如圖4所示,這樣的共模電流將為PCB走線的雜散電容充電。

圖4

請注意,軌到軌旁路電容無法提供這些共模電流。 在圖4中,運算放大器必須直接通過電源和接地導體提供高頻共模電流分量,這是不需要的。 因此,我們需要添加軌對地旁路電容,如圖5所示。

圖5

如您所見,從兩個運算放大器流出的共模電流將由正電源軌和地之間的旁路電容提供(C旁路5 和C旁路7)。 該共模電流將為走線的寄生電容充電。 因此,返回電流將從寄生電容的接地側(cè)流回C的接地側(cè)旁路5 和 C旁路7在接地層中。 類似地,兩個運算放大器吸收的共模電流將由放置在負電源軌和地之間的旁路電容提供(C旁路6 和 C旁路8)。

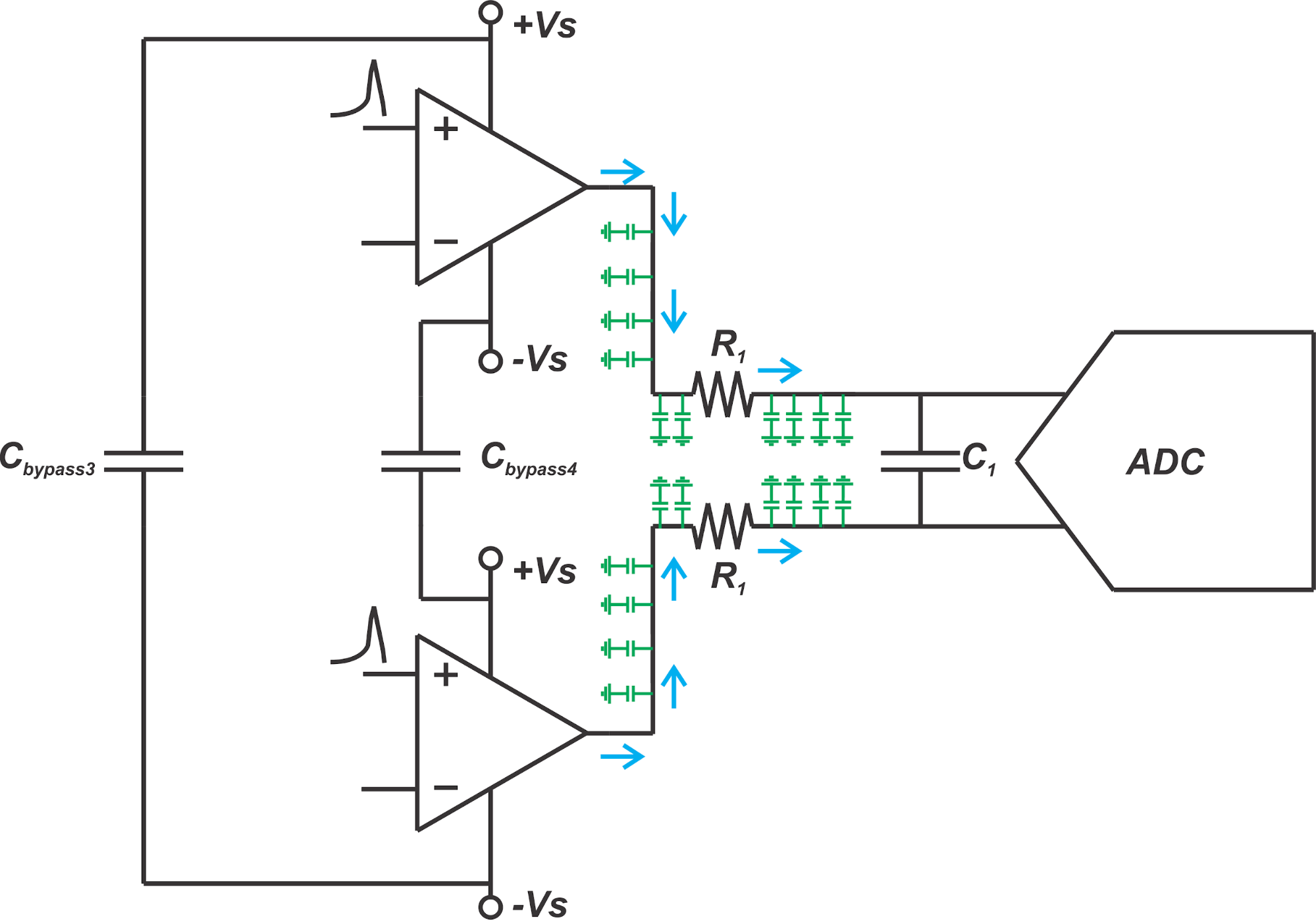

軌對地電容可提供共模和差分電流

雖然我們添加了 C旁路5, C旁路6, C旁路7和 C旁路8為了提供共模電流,這些電容器還將提供負載的一部分高頻差分電流。 如圖2(a)所示,使用軌對地電容會不必要地使差分負載電流流過接地層,這是不需要的。 為了避免這種情況,我們可以放置能夠以對稱方式提供差分電流的軌對地旁路電容器,并在中點將它們之間的走線接地。 圖6 以圖形方式對此進行了最佳說明。

圖6

上圖顯示了上部運算放大器提供負載電流,而下部路徑吸收負載電流的情況。 在這種情況下,C旁路5 和 C旁路8可以提供部分負載差動電流。 為了防止差分電流流過接地層,我們連接C的接地側(cè)旁路5 和 C旁路8通過電路板信號層上的PCB走線一起,并將該走線在中點(圖中的節(jié)點A)接地。 對于差分信號,節(jié)點A理論上應該是虛擬地,差分電流不應流入接地層(I地=0對于差分負載電流)。 同樣,我們放置 C旁路6 和 C旁路7 彼此對稱,并在中點處將兩個電容器之間的走線接地。 您可以在 中找到應用上述技術(shù)的示例布局 此 TI應用報告。

最后,值得一提的是,這些技術(shù)也適用于基于全差分運算放大器的ADC驅(qū)動器。 有關(guān)更多信息,請參閱我上面提到的 TI 文檔。

結(jié)論

為了從差分ADC驅(qū)動器中提取最大線性度性能,我們需要對稱的PCB布局。 采用軌到軌旁路電容器作為高頻差分電流的主要電荷源可將二次諧波分量降低6至10dB。 我們?nèi)匀恍枰墝Φ嘏月冯娙輥硖峁┕材k娏鳌?由于這些電容器還可以提供一部分負載差分電流,因此我們需要對稱布置它們,以使差分負載電流無法流入接地層。

-

放大器

+關(guān)注

關(guān)注

143文章

13434瀏覽量

212189 -

驅(qū)動器

+關(guān)注

關(guān)注

51文章

7998瀏覽量

145025 -

adc

+關(guān)注

關(guān)注

97文章

6300瀏覽量

542459 -

諧波

+關(guān)注

關(guān)注

7文章

783瀏覽量

41639 -

PCB

+關(guān)注

關(guān)注

1文章

1723瀏覽量

13204

發(fā)布評論請先 登錄

相關(guān)推薦

高速PCB布局:高速差分ADC驅(qū)動器軌至軌和軌至地旁路電容器布置方案

高速差分ADC驅(qū)動器設計指南(二)

關(guān)于差分ADC驅(qū)動器的選擇

減少差分ADC驅(qū)動器諧波失真的PCB布局技術(shù)

寬帶運算放大器優(yōu)化高速14位性能差分驅(qū)動器PCB布局技術(shù)的概述

ADA4939-1/ADA4939-2: 超低失真差分 ADC驅(qū)動器

探究減少差分ADC驅(qū)動器諧波失真的PCB布局技術(shù)

差分驅(qū)動ADC第二部分 ADC驅(qū)動器與ADC匹配

用于降低差分ADC驅(qū)動器諧波失真的PCB布局技術(shù)

用于降低差分ADC驅(qū)動器諧波失真的PCB布局技術(shù)

評論