邏輯綜合的含義是什么?

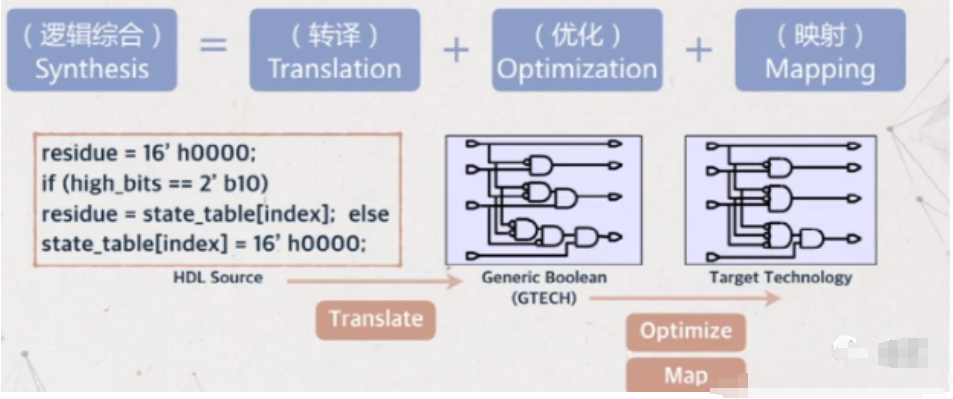

綜合(Logic Synthesize)是指將HDL語言、原理圖等設計輸入翻譯成由與、或、非門等基本邏輯單元組成的門級連接(網表),并根據設計目標與要求(約束條件)優化所生成的邏輯連接,輸出門級網表文件。RTL級綜合指將RTL級源代碼翻譯并優化為門級網表。

RTL級設計的基本要素和步驟是什么

時鐘域描述:描述所使用的所有時鐘,時鐘之間的主從與派生關系,時鐘域之間的轉換。

時序邏輯描述(寄存器描述):根據時鐘沿的變換,描述寄存器之間的數據傳輸方式。

組合邏輯描述:描述電平敏感信號的邏輯組合方式與邏輯功能。 書中推薦的設計步驟。

功能定義與模塊劃分:根據系統功能的定義和模塊劃分準則劃分各個功能模塊。

定義所有模塊的接口:首先清晰定義每個模塊的接口,完成每個模塊的信號列表,這種思路與Modular Design(模塊化設計方法)一致,利于模塊重用、調試、修改。

設計時鐘域:根據設計的時鐘復雜程度定義時鐘之間的派生關系,分析設計中有哪些時鐘域,是否存在異步時鐘域之間的數據交換;對于PLD器件設計,還需要確認全局時鐘是否使用PLL/DLL完成時鐘的分頻、倍頻、移相等功能,哪些時鐘使用全局時鐘資源布線,哪些時鐘使用第二全局時鐘資源布線;全局時鐘的特點是:幾乎沒有Clock Skew(時鐘傾斜),有一定的Clock Delay(時鐘延遲),驅動能力最強;第二全局時鐘的特點是:有較小的Clock Shew,較小的Clock Delay,時鐘驅動能力較強。

考慮設計的關鍵路徑:關鍵路徑是指設計中時序要求最難以滿足的路徑,設計的時序要求主要體現在頻率、建立時間、保持時間等時序指標上,;在設計初期,設計者可以根據系統的頻率要求,粗略的分析出設計的時序難點(如最高頻率路徑、計數器的最低位、包含復雜組合邏輯的時序路徑等),通過一些時序優化手段(如Pipeline、Retiming、邏輯復制等)從代碼上緩解設計的時序壓力,這種方法比依靠綜合與布線工具的自動優化有效的多。

頂層設計:RTL設計推薦使用自頂而下的設計方法,因為這種設計方法與模塊規劃的順序一致,而且更有利于進行Modular Design,可以并行開展設計工作,提高模塊復用率。

FSM設計:FSM是邏輯設計最重要的內容之一。

時序邏輯設計:首先根據時鐘域規劃好寄存器組,然后描述各個寄存器組之間的數據傳輸方式。

組合邏輯設計:一般來說,大段的組合邏輯最好與時序邏輯分開描述,這樣更有利于時序約束和時序分析,使綜合器和布局布線器達到更好的優化效果。

常用的復位方式有哪些

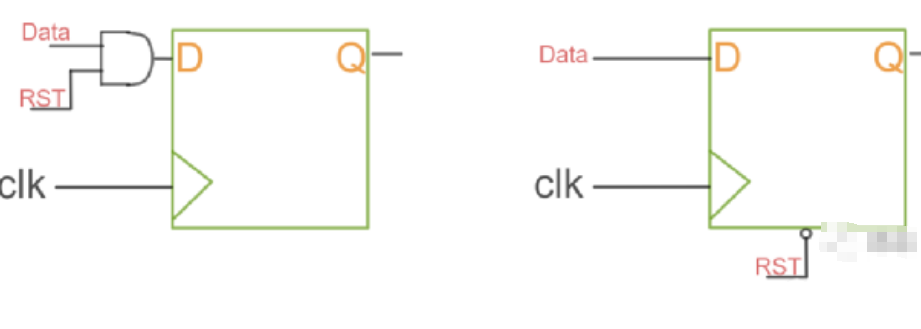

同步復位:當時鐘上升沿檢測到復位信號,執行復位操作(有效的時鐘沿是前提)。always @ ( posedge clk )。優點:有利于仿真器的仿真;可以使所設計的系統成為 100% 的同步時序電路,有利于時序分析,而且可綜合出較高的 Fmax;由于只在時鐘有效電平到來時才有效,所以可以濾除高于時鐘頻率的復位毛刺。缺點:復位信號的有效時長必須大于時鐘周期,才能真正被系統識別并完成復位任務。同時還要考慮諸如 clk skew 、組合邏輯路徑延時 、復位延時等因素(所以復位信號有時需要脈沖展寬,用以保證時鐘有效期間有足夠的復位寬度);由于大多數的邏輯器件的目標庫內的 DFF 都只有異步復位端口,所以,倘若采用同步復位的話,綜合器就會在寄存器的數據輸入端口插入組合邏輯,這樣就會一方面額外增加FPGA內部的邏輯資源,另一方面也增加了相應的組合邏輯門時延。

異步復位它是指無論時鐘沿是否到來,只要復位信號有效,就對系統進行復位。always @ ( posedge clk or negedge rst_n );優點:大多數目標器件庫的 DFF 都有異步復位端口,那么該觸發器的復位端口就不需要額外的組合邏輯,這樣就可以節省資源;設計相對簡單;異步復位信號識別方便(電路在任何情況下都能復位而不管是否有時鐘出現)。缺點:最大的問題在于它屬于異步邏輯,問題出現在復位釋放時,而不是有效時,如果復位釋放接近時鐘有效沿,則觸發器的輸出可能進入亞穩態(此時 clk 檢測到的 rst_n 的狀態就會是一個亞穩態,即是0是1是不確定的),從而導致復位失敗。可能因為噪聲或者毛刺造成虛假復位信號(比如以前的游戲機玩到一半突然復位)(注意:時鐘端口、清零和置位端口對毛刺信號十分敏感,任何一點毛刺都可能會使系統出錯,因此判斷邏輯電路中是否存在冒險以及如何避免冒險是設計人員必須要考慮的問題);靜態時序分析比較困難。對于 DFT設計,如果復位信號不是直接來自于 I/O 引腳,在 DFT 掃描和測試時,復位信號必須被禁止,因此需要額外的同步電路。

為什么推薦使用異步復位同步釋放

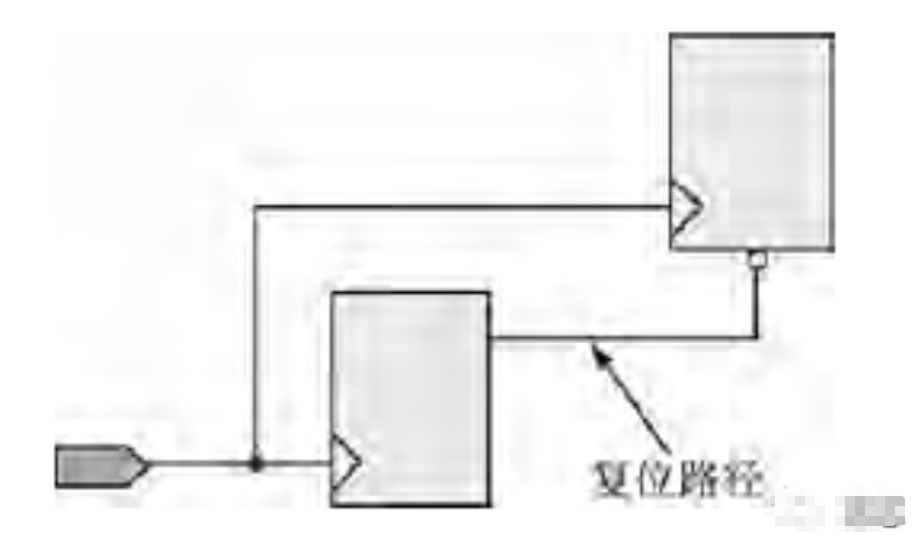

推薦的復位電路設計方式是異步復位,同步釋放。同步釋放的意思就是在正式進入func模式時在寄存器前面多打一拍,這樣可以規避亞穩態風險。異步復位就是復位信號可以直接不受時鐘信號影響,在任意時刻只要是低電平就能復位,即復位信號不需要和時鐘同步。同步釋放讓復位信號取消的時候,必須跟時鐘信號同步,即剛好跟時鐘同沿。

復位的主要目的是使芯片電路進入一個已知的,確定的狀態。主要是觸發器進入確定的狀態。在一般情況下,芯片中的每個觸發器都應該是可復位的。

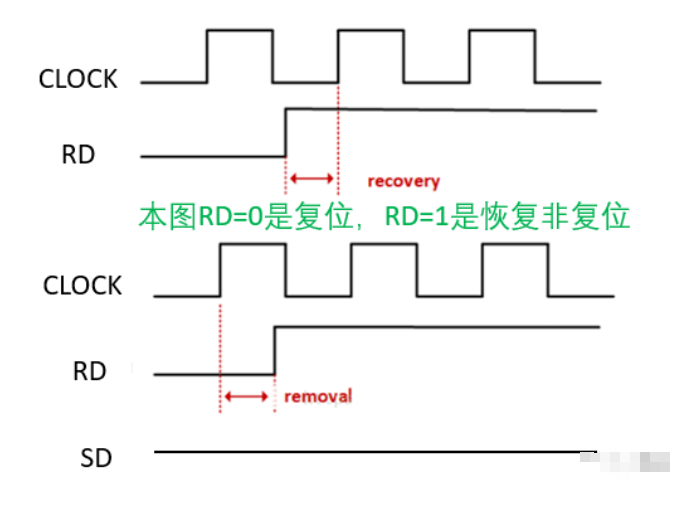

recovery time即恢復時間,撤銷復位時,恢復到非復位狀態的電平必須在時鐘有效沿來臨之前的一段時間到來,才能保證時鐘能有效恢復到非復位狀態,此段時間為recovery time。類似于同步時鐘的setup time。這個針對是本周期的RD的“恢復到非復位狀態的電平”。

什么是RTL建模

此級別的建模使用編程語句和運算符表示數字功能。RTL模型是功能模型,不包含有關如何在硅中實現該功能的詳細信息。由于這種抽象,復雜的數字功能可以比在詳細的門級更快速、更簡潔地建模。RTL模型的仿真速度也大大快于門級和開關級模型,這使得驗證更大、更復雜的設計成為可能。

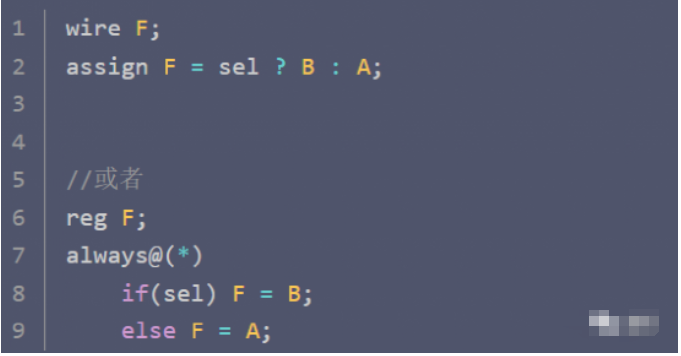

例如二選一選擇器的RTL模型:

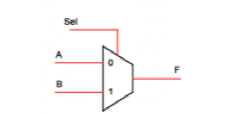

對應的門級電路是:

-

寄存器

+關注

關注

31文章

5317瀏覽量

120008 -

HDL

+關注

關注

8文章

327瀏覽量

47336 -

RTL

+關注

關注

1文章

385瀏覽量

59701 -

復位電路

+關注

關注

13文章

322瀏覽量

44537 -

時序邏輯

+關注

關注

0文章

39瀏覽量

9148

發布評論請先 登錄

相關推薦

RTL級設計的基本要素和步驟是什么

RTL級設計的基本要素和步驟是什么

評論