提到電子設(shè)備的“心臟”,很多人會不約而同地想到時鐘芯片,因為其作用就是基于一個參考頻率源(如石英晶體或單端或差分時鐘),產(chǎn)生頻率穩(wěn)定的節(jié)拍鐘振信號,就像是人的心臟一樣有節(jié)律地“跳動”,以確保系統(tǒng)中各個功能模塊都能夠以此為基礎(chǔ)穩(wěn)定運行并互相協(xié)同。

從更嚴(yán)格的定義上看,時鐘芯片就是在電子系統(tǒng)中生成、調(diào)節(jié)、操縱、分配或控制計時信號的集成電路,其核心的作用有兩點:一是生成準(zhǔn)確的時鐘脈沖信號,二是持續(xù)可靠地分發(fā)該信號供系統(tǒng)內(nèi)的各種計時設(shè)備使用。可以想見,隨著當(dāng)今電子系統(tǒng)運行速度越來越快,運行的環(huán)境越來越復(fù)雜,時鐘芯片面臨的設(shè)計和應(yīng)用挑戰(zhàn)也會越來越大。

時鐘發(fā)生器的選型

時鐘發(fā)生器是一種常見的時鐘芯片,顧名思義,它扮演的角色就是產(chǎn)生同步系統(tǒng)操作所需的計時信號。最基本的時鐘發(fā)生器由諧振電路和放大器組成,被廣泛地應(yīng)用在各類電子和信息通信產(chǎn)品中。諧振電路通常是一塊石英壓電振蕩器,也可以使用簡單的儲能電路甚至是RC電路;將諧振電路產(chǎn)生的振動信號通過頻率倍增器、分頻器和混頻器的處理以產(chǎn)生所需的輸出時鐘信號,這個過程也被稱為頻率合成或時鐘合成。

由于是為整個系統(tǒng)提供一個頻率基準(zhǔn),因此電子電路對于時鐘發(fā)生器這個頻率源的頻率穩(wěn)定度、頻譜純度、頻率范圍等的要求自然是容不得半點馬虎。具體來講,衡量時鐘發(fā)生器性能的優(yōu)劣,主要有以下一些關(guān)鍵指標(biāo):

時鐘抖動

這是用于測量時鐘在時間域或頻率域內(nèi)與理想信號之間誤差量的一個指標(biāo),也是反映時鐘信號質(zhì)量的關(guān)鍵指標(biāo)。

頻率范圍

不同的時鐘發(fā)生器會根據(jù)目標(biāo)應(yīng)用的頻率要求進行優(yōu)化,有些器件會注重支持較寬的頻率,而有些則強調(diào)在特定應(yīng)用的窄頻率范圍內(nèi)提供更高的性能。

輸入和輸出信號類型

每個時鐘信號都需要一個明確定義的高/低電壓和上升/下降時間,由此也就定義了符合行業(yè)標(biāo)準(zhǔn)的不同“信號類型”,包括LVCMOS、LVDS、LVPECL、HCSL等。有些時鐘發(fā)生器支持固定的信號類型,而有些則可支持多種類型。

電源電壓

即器件工作所需的電壓。一般來講,較低的電源電壓對應(yīng)著更低的功率損耗。在不犧牲性能的情況下盡可能節(jié)省功率,自然是理想時鐘發(fā)生器所追求的目標(biāo)。

集成度

像其他芯片一樣,在滿足系統(tǒng)要求的同時使用盡可能少的元器件,這一趨勢也在推動時鐘發(fā)生器向著更高的集成度發(fā)展。

靈活的可編程時鐘發(fā)生器

值得關(guān)注的是,隨著應(yīng)用的發(fā)展,時鐘發(fā)生器也面臨著新的挑戰(zhàn)。

首先,隨著電路復(fù)雜性的增加,如果要滿足電路中不同芯片和接口在時鐘信號方面的要求,傳統(tǒng)的解決方案需要由多個分散的晶振提供支持,而這種方法很可能會引發(fā)多個時鐘源相互之間的干擾,影響系統(tǒng)的性能。

其次,面對更復(fù)雜的系統(tǒng)、更多樣化的設(shè)計需求,開發(fā)者需要選用不同的時鐘源器件,這無疑會增加整個研發(fā)的工作量和BOM的復(fù)雜度,對于優(yōu)化產(chǎn)品生命周期中的研發(fā)和庫存管理成本顯然是不利的。

為了解決這些“痛點”,一種更加靈活的“可編程時鐘發(fā)生器”就應(yīng)運而生了。大家知道,很多時鐘信號發(fā)生器采用的是鎖相環(huán)時鐘(PLL時鐘)架構(gòu),其通過用于比較輸入相位并調(diào)整振蕩器頻率的PLL,保持相匹配的相位。所謂可編程時鐘發(fā)生器就是通過改變電路中倍增器或分頻器的參數(shù)來定義具有不同輸出頻率的時鐘信號,也就是說無需修改硬件,即可從相同的輸入頻率產(chǎn)生不同的輸出頻率,這自然是為開發(fā)者提供了一種極具靈活性和可擴展性的解決方案。而且很多可編程時鐘發(fā)生器還支持同一個器件輸出多路時鐘信號,這對于節(jié)省系統(tǒng)空間、實現(xiàn)更緊湊的設(shè)計也是大有裨益的。

總而言之,可編程時鐘發(fā)生器可通過取代分立的晶體、振蕩器等時鐘元件節(jié)省電路板空間和成本,也為消費電子、數(shù)據(jù)通信、電信和計算等應(yīng)用的設(shè)計開發(fā)帶來極大的靈活性,因此成為了一個頗受關(guān)注的時鐘芯片門類。

高性能、低功耗可編程時鐘發(fā)生器

正是認識到了可編程時鐘發(fā)生器的獨特價值,Renesas Electronics在這個領(lǐng)域一直深耕不輟,根據(jù)實際的目標(biāo)應(yīng)用,開發(fā)出了具有高性能、低功耗、微型封裝等不同特性的可編程時鐘發(fā)生器產(chǎn)品。

其中,VersaClock系列就是很有代表性的一個產(chǎn)品家族,目前已經(jīng)發(fā)展出了20多個可編程時鐘發(fā)生器產(chǎn)品組合,支持1.8V至3.3V的工作電壓,具有差(LVPECL/HCSL/LVSS/LPHCSL)和LVCMOS多樣化的輸出類型,集成最多3個PLL和多個分?jǐn)?shù)分頻器,以準(zhǔn)確生成所需的頻率信號,為用戶提供兼具低功耗、靈活性和高性能的解決方案,非常適合用于消費類、電信、數(shù)據(jù)通信和網(wǎng)絡(luò)應(yīng)用。

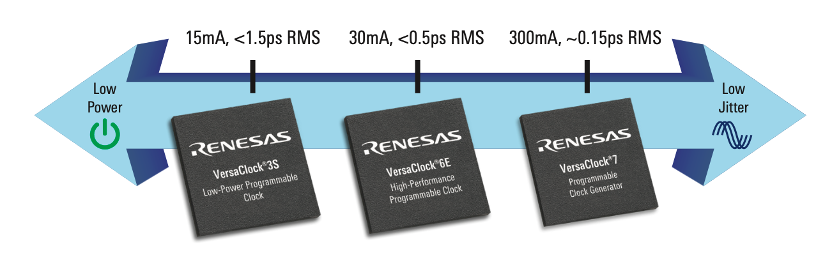

圖1:VersaClock系列主要產(chǎn)品

(圖源:Renesas Electronics)

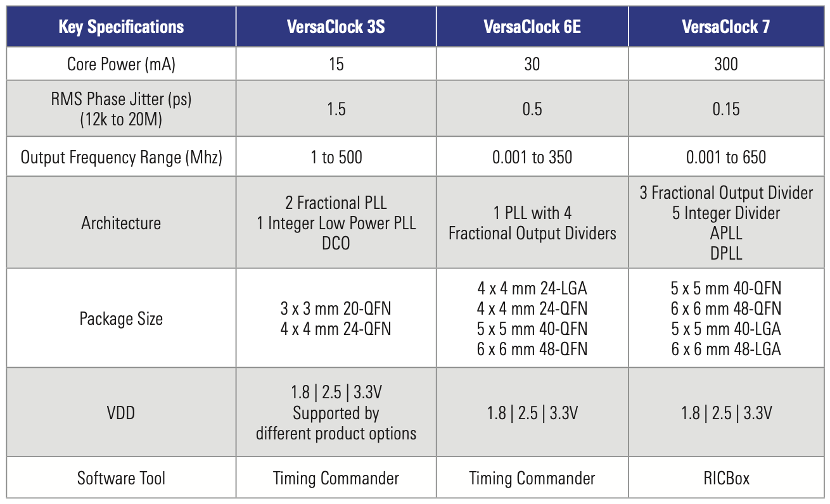

具體來講,VersaClock系列產(chǎn)品包括VersaClock 7、VersaClock 6、VersaClock 5、VersaClock 3S等幾個子系列,產(chǎn)品定義主要是從低功耗、低抖動兩個方向上進行布局(見圖1)。

VersaClock 3S產(chǎn)品低功耗特性出眾,能夠在節(jié)省PCB空間的同時提供出色的節(jié)能表現(xiàn),可滿足包括PCI Express Gen 1/2/3標(biāo)準(zhǔn)在內(nèi)的廣泛應(yīng)用的需求。

VersaClock 5為低功耗、高性能應(yīng)用提供0.7ps的相位抖動(12kHz至20MHz頻率范圍內(nèi)),以及在單個芯片上最多儲存和配置四種不同頻率信號的能力。同時,該時鐘發(fā)生器的工作核心功率仍低于100mW(比競爭產(chǎn)品低50%),低功耗表現(xiàn)也不俗。

VersaClock 6可編程時鐘發(fā)生器相對來講更偏重于高性能,其RMS相位抖動低于500飛秒(fs),適用于10G以太網(wǎng)、PCI Express 1/2/3代標(biāo)準(zhǔn)、PHY參考時鐘和高端FPGA等對于抖動和相位噪聲要求更為嚴(yán)苛的應(yīng)用。與此同時,其核心電流消耗仍控制在30mA,以盡可能降低系統(tǒng)的功耗。

VersaClock 7是VersaClock系列的新產(chǎn)品,適用于高階計算、有線基礎(chǔ)設(shè)施及數(shù)據(jù)中心設(shè)備的PCIe和以太網(wǎng)應(yīng)用。VersaClock 7產(chǎn)品包括5路、8路和12路輸出器件,12kHz至20MHz RMS抖動低至150fs,在同系列產(chǎn)品中性能表現(xiàn)搶眼。其中,以8路輸出器件為例,其采用5mm x 5mm QFN封裝,比目前市場上同類產(chǎn)品小30%,有助于開發(fā)者實現(xiàn)更緊湊的設(shè)計;此外,該系列時鐘發(fā)生器還提供集成晶體選項,可進一步節(jié)省系統(tǒng)空間并優(yōu)化BOM。

圖2:VersaClock 7可編程時鐘發(fā)生器

(圖源:Renesas Electronics)

VersaClock 7產(chǎn)品特性可以概括如下:

-

1.8V/2.5V/3.3V靈活電源軌

-

典型150fs RMS 12kHz-20MHz相位抖動

-

5/8/12輸出,帶集成晶體選項

-

1kHz至650MHz LVDS/LP-HCSL輸出

-

LVCMOS輸出:1kHz至200MHz

-

可編程硬件配置選擇引腳

-

支持PCIe Gen5/6

-

節(jié)省空間的封裝:4mm x 4mm、5mm x 5mm、6mm x 6mm

-

集成晶體選項,用于節(jié)省空間和優(yōu)化BOM

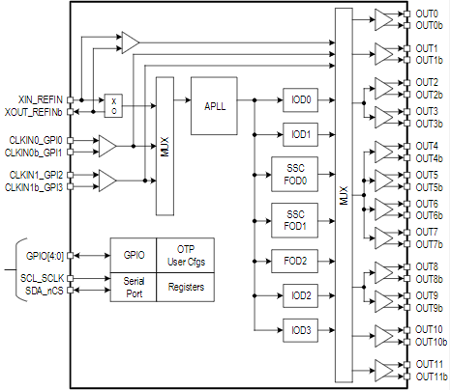

圖3:VersaClock 7可編程時鐘發(fā)生器框圖

(圖源:Renesas Electronics)

圖4:VersaClock系列主要產(chǎn)品性能對比

(圖源:Renesas Electronics)

便捷的可編程開發(fā)體驗

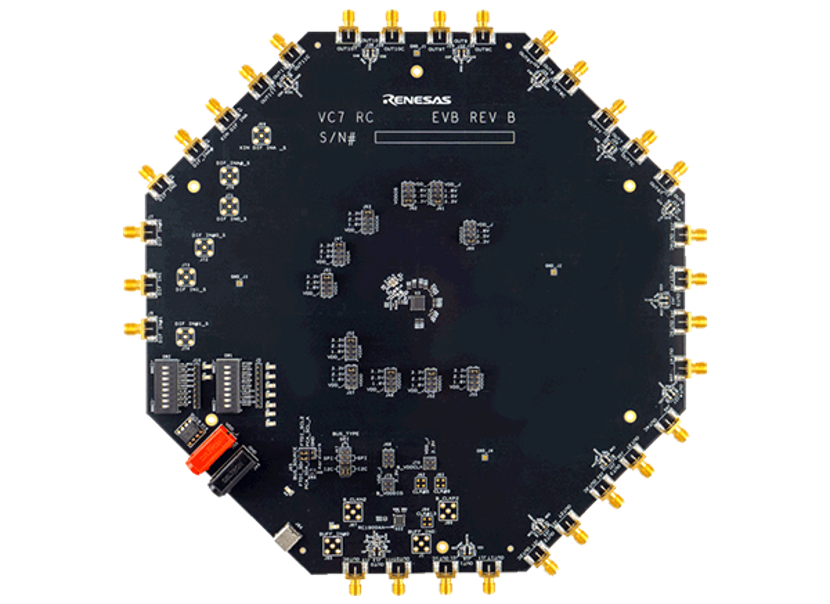

為了方便開發(fā),Renesas還提供了VersaClock評估板,用于評估VersaClock時鐘發(fā)生器。該VersaClock評估板特性包括:

-

通過SMA實現(xiàn)晶體或晶體過驅(qū)動(REFIN)

-

晶體過驅(qū)動和CLKIN上提供檢測線路

-

板載I2C和SPI通信

-

四個GPI和五個GPIO

-

GPI/GPIO LED指示燈和DIP開關(guān)

-

輸出上的測試點,用于Hi-Z探頭

圖5:VersaClock評估板

(圖源:Renesas Electronics)

而且,開發(fā)者通過Renesas提供的全新RICBox應(yīng)用程序,可以很方便地配置VersaClock 7器件,在評估板上完成配置創(chuàng)建和器件編程。也就是說,基于RICBox這個新推出的軟件平臺,客戶可以使用Python驅(qū)動或Windows GUI來創(chuàng)建自定義配置,并對評估板上的VersaClock 7器件進行編程,而無需相關(guān)的專業(yè)知識。而且,通過RICBox與Renesas的創(chuàng)新云端實驗室平臺無縫對接,用戶還可以下載自己創(chuàng)建的配置并在本地使用RICBox進行操作,或者是將配置上傳至云端實驗室進行性能分析。

總之,完整而易用的開發(fā)資源使得VersaClock 7可編程時鐘發(fā)生器在性能、設(shè)計靈活性方面的優(yōu)勢得以充分發(fā)揮出來,為用戶提供了極為便捷的開發(fā)體驗。

本文小結(jié)

在電子系統(tǒng)中,時鐘元件是系統(tǒng)穩(wěn)定運行、精準(zhǔn)通信的基石。而隨著系統(tǒng)復(fù)雜性的增加,從一個或多個參考頻率中產(chǎn)生多種頻率的時鐘信號,且可以通過編程靈活配置輸出頻率的可編程時鐘發(fā)生器更是成為市場上的大熱門;而且伴隨著各種應(yīng)用不斷發(fā)展,對這種精準(zhǔn)、靈活、小巧的時鐘芯片的需求也日趨旺盛。

Renesas顯然已經(jīng)為此做足了準(zhǔn)備,通過不斷擴充可編程時鐘產(chǎn)品組合、完善配套的設(shè)計資源,為開發(fā)者提供更高性能、更大自由度的開發(fā)體驗。這樣的解決方案,你想不想也來嘗試一下?

Renesas VersaClock 7時鐘發(fā)生器

VersaClock 7可編程時鐘發(fā)生器,了解詳情>>

VersaClock 7評估板,了解詳情>>

該發(fā)布文章為獨家原創(chuàng)文章,轉(zhuǎn)載請注明來源。對于未經(jīng)許可的復(fù)制和不符合要求的轉(zhuǎn)載我們將保留依法追究法律責(zé)任的權(quán)利。

關(guān)于貿(mào)澤電子貿(mào)澤電子(Mouser Electronics)是一家全球授權(quán)半導(dǎo)體和電子元器件授權(quán)分銷商,服務(wù)全球廣大電子設(shè)計群體。貿(mào)澤電子原廠授權(quán)分銷近1,200家知名品牌,可訂購數(shù)百萬種在線產(chǎn)品,為客戶提供一站式采購平臺,歡迎關(guān)注我們,獲取第一手的設(shè)計與產(chǎn)業(yè)資訊信息!

更多精彩

原文標(biāo)題:精準(zhǔn)、靈活、小巧的可編程時鐘發(fā)生器,你用過嗎?

文章出處:【微信公眾號:貿(mào)澤電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

貿(mào)澤電子

+關(guān)注

關(guān)注

16文章

1100瀏覽量

96557

原文標(biāo)題:精準(zhǔn)、靈活、小巧的可編程時鐘發(fā)生器,你用過嗎?

文章出處:【微信號:貿(mào)澤電子,微信公眾號:貿(mào)澤電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

可編程按鈕、脈沖檢測器和脈沖發(fā)生器解決方案

PLL1707-Q1多時鐘發(fā)生器數(shù)據(jù)表

CDCS501 SSC時鐘發(fā)生器/緩沖器數(shù)據(jù)表

CDCI6214超低功耗時鐘發(fā)生器(具有PCIe支持、四路可編程輸出和EEPROM)數(shù)據(jù)表

CDCE62005高性能時鐘發(fā)生器和分配器數(shù)據(jù)表

CDCE62002高性能時鐘發(fā)生器數(shù)據(jù)表

LMK05318B超低抖動時鐘發(fā)生器數(shù)據(jù)表

LMH1983高度集成的可編程音頻/視頻(AV)時鐘發(fā)生器數(shù)據(jù)表

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

LMK3H0102無基準(zhǔn)2差分或5單端輸出PCIe第1代到第6代兼容可編程BAW時鐘發(fā)生器數(shù)據(jù)表

具有14個可編程輸出的LMK03806超低抖動時鐘發(fā)生器數(shù)據(jù)表

探索 MEMS 可編程 LVCMOS 振蕩器 SiT8009 系列:精準(zhǔn)與靈活的時脈先鋒

解讀 MEMS 可編程 LVCMOS 振蕩器 SiT8008 系列:精準(zhǔn)與靈活的時脈之選

CDCE6214超低功率時鐘發(fā)生器數(shù)據(jù)表

時鐘發(fā)生器性能對數(shù)據(jù)轉(zhuǎn)換器的影響

精準(zhǔn)、靈活、小巧的可編程時鐘發(fā)生器,你用過嗎?

精準(zhǔn)、靈活、小巧的可編程時鐘發(fā)生器,你用過嗎?

評論