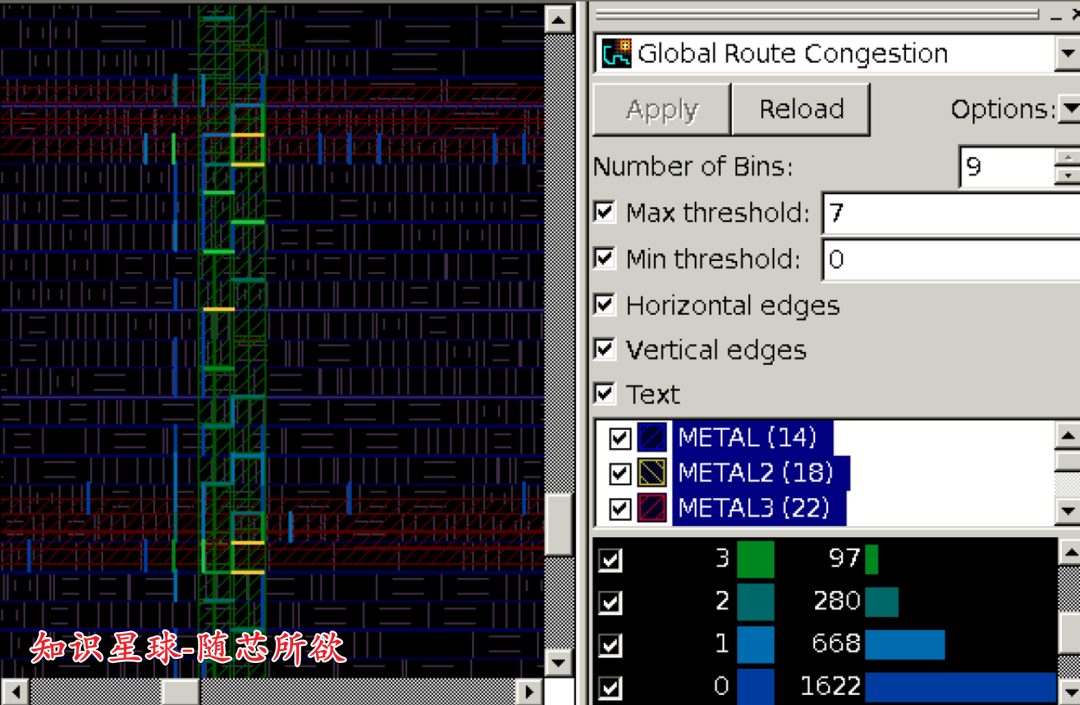

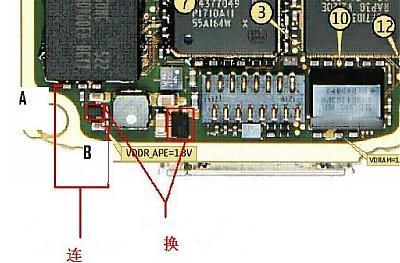

如果數字IC版圖設計中Power Mesh打的太寬(尤其是VDD和VSS的Stripe靠近放置的情況),下方還放置的有標準單元,那么在出Pin的地方可能會存在Congestion,如下圖所示,那么這種問題該如何解決呢?對于ICC、Innouvs、ICC2分別該如何解決呢? ?

?

解決方案:

1、調整PG structure,讓電源地間隔放置。或者合理減少power,不要打太多、不要打太寬。根據以往經驗和IR-drop分析的結果,可以在IR-drop滿足的情況下,降低PG的寬度,不用占用太多布線資源。

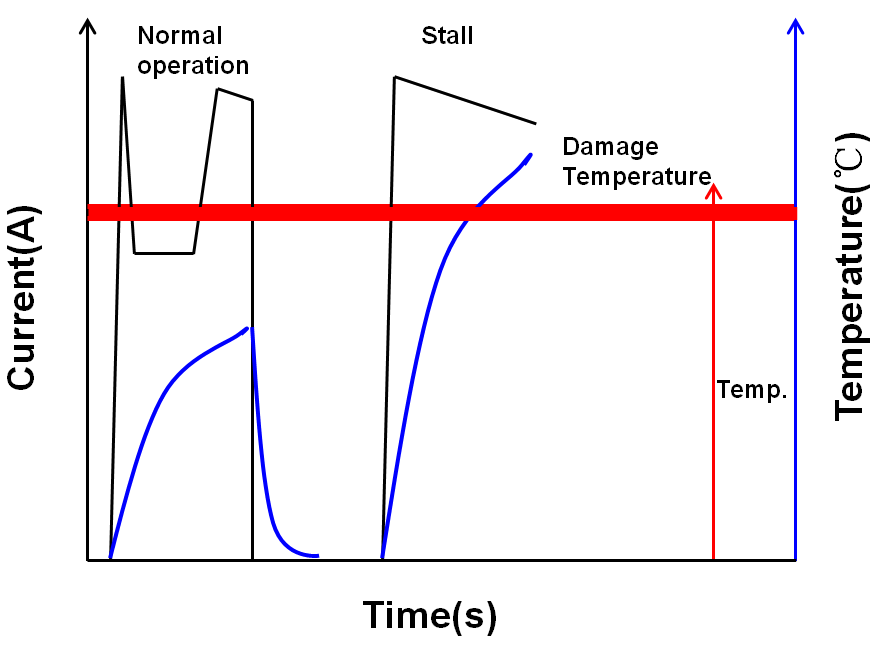

2、一般在電源地Strap下面放置標準單元時,可能會在Strap的地方存在Congestion。這時可以限制工具在電源地Strap下面少放或者不放置標準單元,設置hard blockage,partial blockage/partial density control。

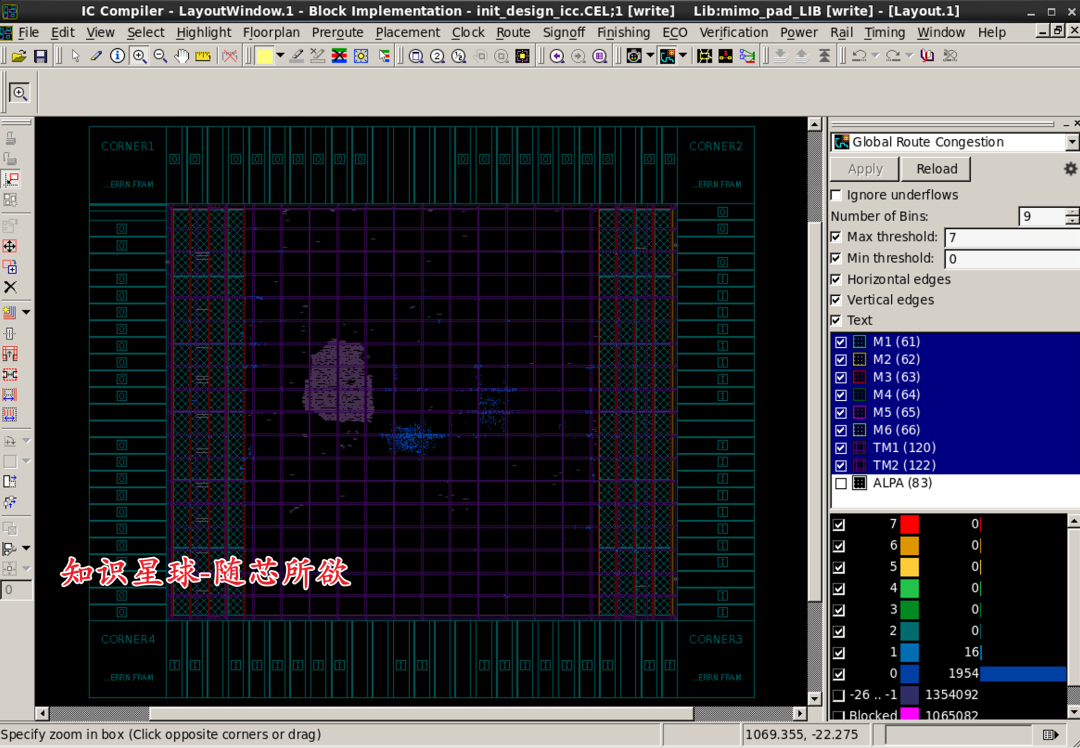

如下圖所示,可以非常清晰的看到,大部分的擁塞都發生在PG Mesh附近,這可以通過對Power Mesh設置partial blockage來解決。

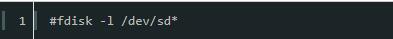

下面分別講解一下在ICC/ICC2和Innovus該如何實現該需求。

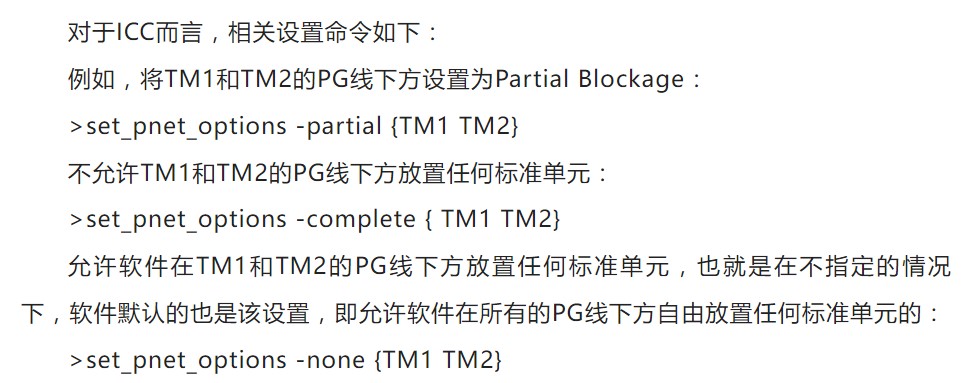

ICC設置:

ICC2設置

實例:

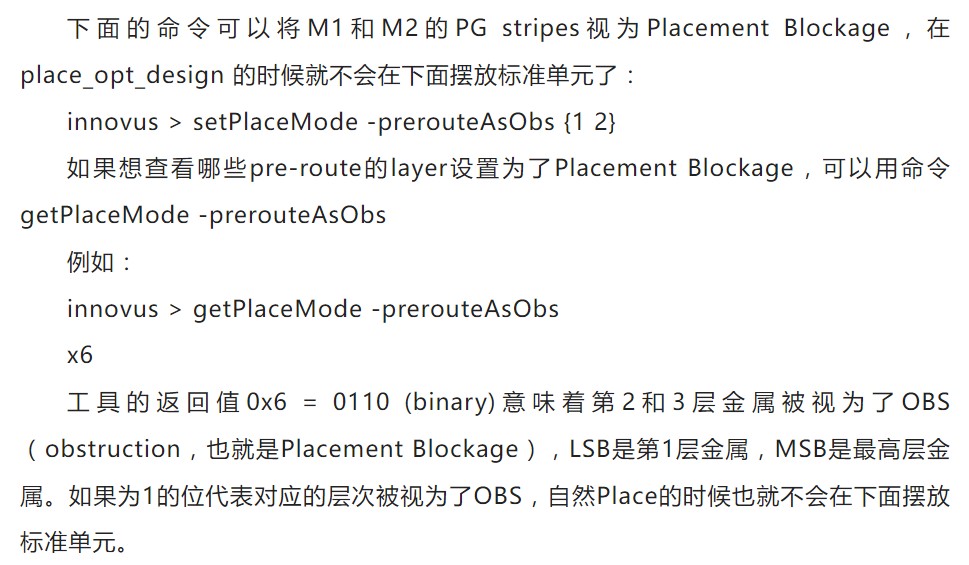

Innovus設置:

方法1:將指定Layer的preroute視為Placement Blockage

方法2:在PG stripes下方創建Partial Placement Blockage

審核編輯:劉清

-

數字IC

+關注

關注

1文章

37瀏覽量

12511 -

VDD

+關注

關注

1文章

311瀏覽量

33108 -

VSS

+關注

關注

1文章

31瀏覽量

21421 -

電源地

+關注

關注

0文章

36瀏覽量

9751 -

mesh技術

+關注

關注

0文章

14瀏覽量

8749

原文標題:Congestion修復實例及腳本分享 - 控制PG stripe下面少放甚至不放Cell

文章出處:【微信號:集成電路設計及EDA教程,微信公眾號:集成電路設計及EDA教程】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字IC版圖設計中Power Mesh打的太寬怎么辦

數字IC版圖設計中Power Mesh打的太寬怎么辦

評論