作者:Jim Surber and Leo McHugh

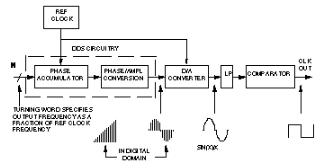

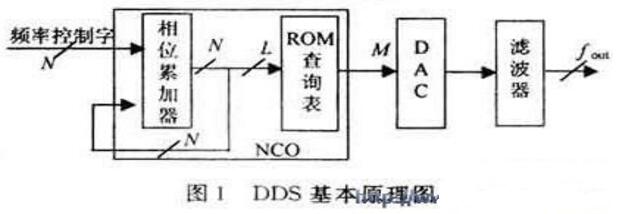

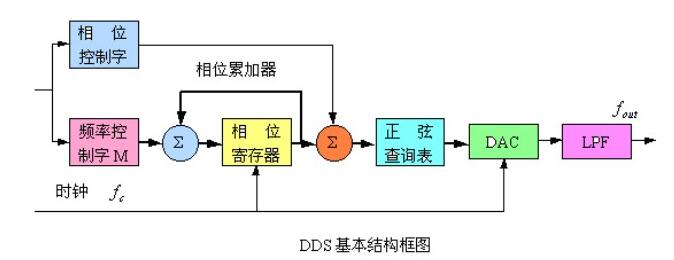

新的集成完整DDS產(chǎn)品為敏捷頻率合成應(yīng)用提供了一種有吸引力的模擬PLL替代方案。長期以來,直接數(shù)字頻率合成 (DDS) 一直被認(rèn)為是生成高精度、頻率捷變(寬范圍內(nèi)可快速變化的頻率)、低失真輸出波形的卓越技術(shù)。DDS架構(gòu)(圖1)采用精密相位累加器和數(shù)字信號處理技術(shù)來生成數(shù)字正弦波表示,該表示以高度穩(wěn)定的參考時(shí)鐘為參考。然后將數(shù)字正弦波數(shù)據(jù)施加到高速數(shù)模轉(zhuǎn)換器(DAC),以產(chǎn)生相應(yīng)的模擬正弦波輸出信號。

圖1.基本完整DDS系統(tǒng)框圖。

DDS系統(tǒng)的一個(gè)主要優(yōu)點(diǎn)是,可以在數(shù)字處理器控制下精確快速地控制其輸出頻率和相位。其他固有的DDS屬性包括能夠以極精細(xì)的頻率和相位分辨率進(jìn)行調(diào)諧(頻率控制在毫赫茲(mHz)范圍內(nèi),相位控制<0.09°,以及頻率快速“跳躍”(每秒高達(dá)2300萬次輸出頻率變化)。這些特性相結(jié)合,使該技術(shù)在軍用雷達(dá)和通信系統(tǒng)中非常受歡迎。事實(shí)上,DDS技術(shù)以前幾乎完全被降級為高端和軍事應(yīng)用:它成本高,耗電大(以瓦特為單位的耗散),難以實(shí)現(xiàn),需要分立的高速信號DAC,并且有一組用戶不利的系統(tǒng)接口要求。

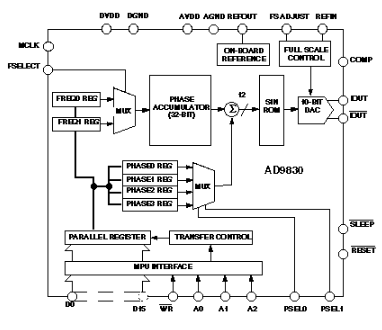

圖2.AD9830 50 MHz C-DDS的框圖

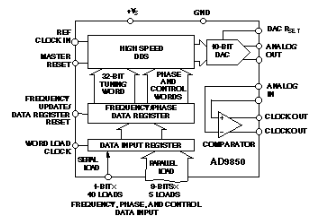

ADI公司推出的全新突破性CMOS數(shù)字頻率合成器產(chǎn)品系列提高了基于DDS的頻率合成器解決方案的吸引力。AD9850、AD9830125MHz和50 MHz完整DDS(CDDS)器件包括片內(nèi)10位信號DAC(圖2和圖3)。它們針對低輸出失真進(jìn)行了優(yōu)化,具有 72 dBc 窄帶的無雜散動(dòng)態(tài)范圍 (SFDR) 和高達(dá) 54 dBC 的寬帶 @ 40 MHz。 其他產(chǎn)品特性,如小型表面貼裝封裝、極低的功耗(+3.3 V時(shí)低至155 mW)、增強(qiáng)的功能和低廉的價(jià)格,共同確保這些器件確實(shí)是DDS技術(shù)的最新技術(shù)。它們現(xiàn)在允許用戶處理成本敏感型、大批量、消費(fèi)類合成器應(yīng)用;它們?yōu)榛谀M的鎖相環(huán)(PLL)技術(shù)提供了一種可行的替代方案,用于生成敏捷的模擬輸出頻率。

AD98x0器件對于本振(LO)和上/下變頻級應(yīng)該具有獨(dú)特的吸引力,而這些器件迄今為止一直是基于PLL的模擬頻率合成器的專屬領(lǐng)域。出于多種原因,AD98x0器件的完整DDS架構(gòu)與等效的基于PLL的敏捷模擬頻率合成器相比具有明顯的優(yōu)勢。例如:

輸出頻率分辨率:AD98x0 C-DDS產(chǎn)品具有32位相位累加器,可實(shí)現(xiàn)比基于PLL的頻率合成器更精細(xì)的輸出頻率調(diào)諧分辨率。AD9850的可調(diào)輸出分辨率為0.06 Hz,時(shí)鐘頻率為125 MHz;AD9830的調(diào)諧分辨率為0.012 Hz,參考時(shí)鐘為50 MHz。此外,這些器件的輸出在過渡到新頻率期間是相位連續(xù)的。相比之下,基于 PLL 的基本模擬頻率合成器的輸出調(diào)諧分辨率通常為 1 kHerz;它缺乏數(shù)字信號處理提供的固有分辨率。

輸出電壓開關(guān)時(shí)間:模擬PLL頻率開關(guān)時(shí)間是其反饋環(huán)路建立時(shí)間和VCO響應(yīng)時(shí)間的函數(shù),通常>1 ms。基于 C-DDS 的頻率合成器切換時(shí)間僅受 DDS 數(shù)字處理延遲限制;AD9850的最小輸出頻率開關(guān)時(shí)間為43 ns。

調(diào)諧范圍: 關(guān)鍵反饋環(huán)路帶寬和輸入?yún)⒖碱l率關(guān)系決定了典型模擬PLL電路的穩(wěn)定(可用)頻率范圍。基于 C-DDS 的頻率合成器不受此類環(huán)路濾波器穩(wěn)定性問題的影響,并且在整個(gè)奈奎斯特范圍(<時(shí)鐘速率的 1/2)內(nèi)可調(diào)諧。

相位噪聲: 由于分頻,基于C-DDS的解決方案在輸出相位噪聲方面比模擬PLL頻率合成器具有明顯的優(yōu)勢。C-DDS頻率合成器的輸出相位噪聲實(shí)際上優(yōu)于其參考時(shí)鐘源,而基于模擬PLL的頻率合成器的缺點(diǎn)是實(shí)際上會(huì)增加其參考頻率中的相位噪聲。

電路板空間要求: 高度集成的AD98x0 C-DDS器件采用非常小的表面貼裝封裝,與大多數(shù)高質(zhì)量等效帶寬分立PLL頻率合成器方案相比,不需要更多的電路板空間。

成本: 打破現(xiàn)有的DDS價(jià)格障礙,基于C-DDS的解決方案在大批量應(yīng)用中具有競爭力,具有帶寬等效的基于PLL的分立式頻率合成器解決方案。

功耗: C-DDS頻率合成器的功耗比早期的分立DDS解決方案低得多。例如,AD9850在3.3 V時(shí),采用100 MHz參考時(shí)鐘產(chǎn)生40 MHz信號時(shí)功耗為155 mW。這與同類分立式模擬PLL電路相比具有競爭力。

實(shí)施復(fù)雜性: 完整的DDS解決方案,包括信號DAC,意味著系統(tǒng)設(shè)計(jì)變得容易。不再需要實(shí)現(xiàn)DDS解決方案所需的RF設(shè)計(jì)專業(yè)知識;困難的部分已經(jīng)完成。用于控制的簡單數(shù)字指令集可最大程度地降低支持硬件的復(fù)雜性。數(shù)字系統(tǒng)設(shè)計(jì)取代了基于PLL的模擬頻率合成器解決方案所需的模擬密集型系統(tǒng)設(shè)計(jì),以解決類似問題。

圖3.AD9850 125 MHz C-DDS框圖

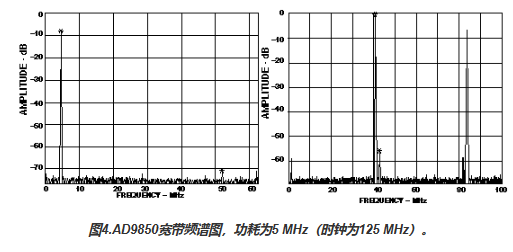

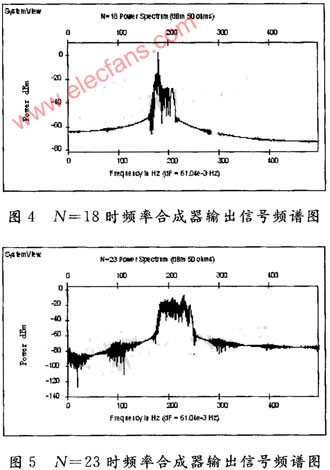

交流性能是選擇頻率合成器時(shí)的一個(gè)重要考慮因素。C-DDS頻率合成器系統(tǒng)的失真性能受其信號DAC的限制;AD98x0器件在CMOS DAC性能方面樹立了新的基準(zhǔn)。其板載 10 位 DAC 內(nèi)核針對寬輸出帶寬上的高 SFDR 進(jìn)行了深入優(yōu)化,本身就是技術(shù)突破(請參閱本期第 7-9 頁)。圖4和圖5顯示了AD9850輸出的寬帶頻譜圖,該輸出頻率采用125 MHz參考時(shí)鐘產(chǎn)生5 MHz和40 MHz輸出頻率。在62.5 MHz奈奎斯特帶寬(參考時(shí)鐘速率的1/2)下,AD9850輸出的SFDR分別為62.8 dB和55.2 dB。這種動(dòng)態(tài)性能以前只能通過耗散幾瓦的昂貴雙極性DAC來實(shí)現(xiàn)。

圖4.AD9850寬帶頻譜圖,功耗為5 MHz(時(shí)鐘為125 MHz)。

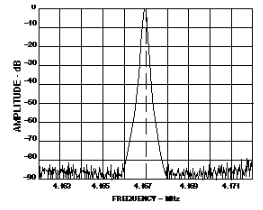

在其他應(yīng)用中,其中許多應(yīng)用以基于模擬PLL的頻率合成器解決方案為主,窄帶性能是一個(gè)重要的考慮因素。在窄帶應(yīng)用中,C-DDS頻率合成器輸出的雜散性能在很大程度上取決于DDS的數(shù)字截?cái)嚯娖剑皇荄AC的性能。圖6顯示了AD9830在4.16 MHz A時(shí)的窄帶圖外和一個(gè) 50 MHz 時(shí)鐘。SFDR在基波的±5 kHz窗口內(nèi)大于79 dB。

圖6.AD9830窄帶頻譜圖4.1 MHz Aout(50 MHz時(shí)鐘)。

AD9850和AD9830均采用非常簡單的負(fù)載方案,以實(shí)現(xiàn)用戶友好的操作。它們只需要一個(gè)數(shù)據(jù)時(shí)鐘和數(shù)據(jù)/地址總線來控制輸出頻率和相位,并啟用休眠模式。除了輸出濾波的特定要求外,不需要模擬密集型系統(tǒng)設(shè)計(jì)。AD9850還有一個(gè)有用的附加特性:集成高速比較器。DAC的濾波輸出可施加到該比較器,以產(chǎn)生方波輸出而不是正弦波,從而便于將該器件用作頻率捷變時(shí)鐘發(fā)生器。兩款器件均提供PC兼容評估板,便于對合成系統(tǒng)進(jìn)行臺架測試。

快速輸出跳頻、數(shù)字控制、低輸出失真和高調(diào)諧分辨率的組合使 Complete-DDS 解決方案成為模擬 PLL 頻率合成器的可行替代方案。AD9830和AD9850在CMOS DAC和DDS技術(shù)方面的突破值得認(rèn)真考慮任何頻率合成器要求。

是呢環(huán)保局:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19160瀏覽量

229115 -

pll

+關(guān)注

關(guān)注

6文章

774瀏覽量

135046 -

DDS

+關(guān)注

關(guān)注

21文章

631瀏覽量

152541

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化...

怎么設(shè)計(jì)直接數(shù)字頻率合成器?

基于FPGA的直接數(shù)字頻率合成器的設(shè)計(jì)

基于FPGA的直接數(shù)字頻率合成器的設(shè)計(jì)和實(shí)現(xiàn)

基于SystemView的數(shù)字頻率合成器的設(shè)計(jì)

放大直接數(shù)字頻率合成的DAC選型器應(yīng)用

基于單片機(jī)的直接數(shù)字頻率合成詳解

直接數(shù)字頻率合成知識點(diǎn)匯總(原理_組成_優(yōu)缺點(diǎn)_實(shí)現(xiàn))

直接數(shù)字頻率合成技術(shù)的頻率研究

數(shù)字頻率合成芯片AD9837的性能及應(yīng)用分析

ADI直接數(shù)字頻率合成器(DDS)

直接數(shù)字頻率合成信號發(fā)生器的設(shè)計(jì)

單芯片直接數(shù)字頻率合成與模擬PLL的比較

單芯片直接數(shù)字頻率合成與模擬PLL的比較

評論