作者:Doug Mercer and Joe DiPilato

引腳兼容的AD976x系列8位、10位、12位和14位TxDAC?低失真DAC以高達(dá)125 MSPS的時(shí)鐘速率提供出色的無(wú)雜散動(dòng)態(tài)范圍(SFDR)規(guī)格,具有CMOS器件典型的低價(jià)格和功耗水平。

面向消費(fèi)者的無(wú)線和有線通信市場(chǎng)的迅速擴(kuò)張催生了對(duì)高速模數(shù)和數(shù)模轉(zhuǎn)換器的永不滿足的需求,這些轉(zhuǎn)換器具有良好的動(dòng)態(tài)(頻域)性能,成本低,功耗低。最明顯的表現(xiàn)是為滿足接收路徑的需求而開(kāi)發(fā)的新型CMOS ADC產(chǎn)品的盛宴;但是,目前缺乏適合許多發(fā)射信號(hào)路徑應(yīng)用的具有動(dòng)態(tài)性能的低成本CMOS DAC產(chǎn)品。

傳統(tǒng)的時(shí)域和直流線性度特性,如積分非線性(INL)、差分非線性(DNL)、毛刺脈沖和建立時(shí)間,都不足以反映頻域中的響應(yīng)和失真。大多數(shù)現(xiàn)有的高速CMOS DAC主要用于視頻應(yīng)用,其無(wú)雜散動(dòng)態(tài)范圍(SFDR)和諧波失真(THD)往往較差。雙極性和BiCMOS器件可以提供所需的動(dòng)態(tài)性能,但它們通常成本太高,需要雙電源,并且功耗過(guò)高,不適合未來(lái)的大容量通信應(yīng)用。

低功耗需求是由通信平臺(tái)的變化驅(qū)動(dòng)的。它們要么在物理上變得越來(lái)越小,需要更高的組件封裝密度(例如,微型和微型基站封裝在懸掛在電線桿和建筑物側(cè)面的小盒子中);或便攜式和電池供電(例如,電話、尋呼機(jī)、抄表終端等);或由電話線供電(無(wú)線本地環(huán)路);或需要備用電池(電纜電話、生命線服務(wù))。這些要求都要求低功耗以延長(zhǎng)電池壽命,最大限度地減少散熱,并在有限的可用功率下運(yùn)行。在這方面,單電源組件避免了額外電源的成本和低效率。3V 單電源器件正變得非常流行,以實(shí)現(xiàn)更低的功耗并與高密度數(shù)字電路兼容。

這些對(duì)低成本、低功耗和良好動(dòng)態(tài)性能的要求導(dǎo)致了用于發(fā)射應(yīng)用的新型高速CMOS DAC的開(kāi)發(fā)。這種新型低成本TxDAC?系列的額定更新速率高達(dá)125 MHz,是高速發(fā)送路徑CMOS DAC的重大突破。它們提供的SFDR性能是迄今為止高速CMOS DAC無(wú)法實(shí)現(xiàn)的。

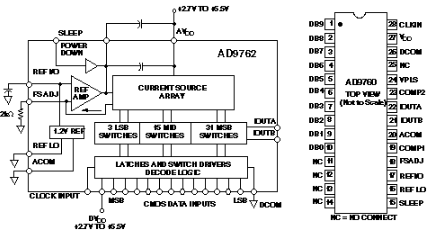

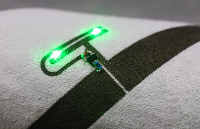

TxDAC系列的前五款產(chǎn)品包括8位、50 MSPS AD9708AR;10位、50 MSPS AD9760AR-50;10位、125 MSPS AD9760AR;12位、125 MSPS AD9762AR;以及14位、125MSPS AD9764AR。所有五種型號(hào)均采用引腳兼容的28引腳SOIC封裝,使設(shè)計(jì)人員能夠在設(shè)計(jì)周期的評(píng)估階段輕松權(quán)衡性價(jià)比。圖1顯示了12位AD9762的功能框圖和10位AD9760的引腳排列。無(wú)論分辨率如何,MSB (DB N1) 在該系列中始終是引腳 1;低分辨率設(shè)備可以直接連接到為高分辨率設(shè)備布線的電路。這允許統(tǒng)一的設(shè)計(jì)尺寸和直接交換不同分辨率的模型,以便進(jìn)行比較、升級(jí)和降低定價(jià)。

圖1.AD9762框圖和AD9760引腳排列。

這些器件采用低成本亞微米單多晶硅雙金屬CMOS工藝制造。每個(gè)DAC的模擬和數(shù)字電路均可采用+2.7 V至+5.5 V單電源供電(提供全3 V單電源供電)。每個(gè)DAC包括一個(gè)溫度補(bǔ)償型1.2 V帶隙基準(zhǔn)電壓源,提供高達(dá)20 mA滿量程(順從電壓= 1.25 V)的差分電流輸出,由片內(nèi)基準(zhǔn)電壓放大器調(diào)節(jié),可使用外部電阻在2 mA至20 mA范圍內(nèi)進(jìn)行設(shè)置。DAC輸出在35 ns內(nèi)穩(wěn)定至最終值的0.25%以內(nèi)。滿量程10%至90%的上升和下降時(shí)間規(guī)定為2.5 ns,輸出傳播延遲僅為1 ns。

設(shè)計(jì)特點(diǎn)

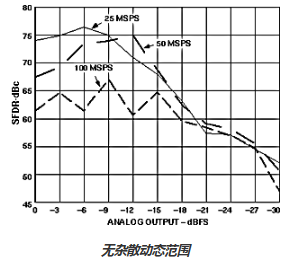

為了消除與傳統(tǒng)R-2R梯形架構(gòu)相關(guān)的幅度相關(guān)失真,并實(shí)現(xiàn)卓越的交流和直流性能,TxDAC采用了分段電流源。例如,12位AD9762的核心是49個(gè)電流源(圖1)。5 個(gè)最高有效位對(duì)輸出的貢獻(xiàn)由最多 31 個(gè)相等的電流源相加而成,每個(gè)電流源的權(quán)重為 25司 司長(zhǎng)。接下來(lái)四位的貢獻(xiàn)是通過(guò)將最多 15 個(gè)電流源相加,其權(quán)重是第一組的 1/16(即 29FS 每個(gè))。3 LSB 由或多或少的傳統(tǒng) 3 位二進(jìn)制 DAC 開(kāi)關(guān)電流組成,其權(quán)重為第二組的 1/2、1/4 和 1/8。這種分段架構(gòu)是AD9762實(shí)現(xiàn)±0.5 LSB 12位DNL性能和5 pV-s低輸出毛刺脈沖規(guī)格以及多音應(yīng)用中出色SFDR的關(guān)鍵,在這些應(yīng)用中,DAC的輸出通常以1/2或1/4滿量程工作。圖2顯示了AD9762在不同速率下的單音SFDR與輸出電平的關(guān)系。

對(duì)于通信應(yīng)用的傳輸路徑,分段電流源架構(gòu)本身不足以實(shí)現(xiàn)所需的SFDR。為了減少交流失真的固有原因,尤其是諧波,我們集中精力在改進(jìn)輸出開(kāi)關(guān)時(shí)序上。由此產(chǎn)生的創(chuàng)新專有鎖存器和開(kāi)關(guān)電路使SFDR比傳統(tǒng)的CMOS“視頻”DAC產(chǎn)品提高了約20 dB。此外,TxDAC 系列的 SFDR 性能可與最好的雙極性和 BiCMOS IC 器件相媲美,但功耗和價(jià)格僅為其一小部分。

無(wú)雜散動(dòng)態(tài)范圍圖2.SFDR與不同采樣率下的輸出幅度的關(guān)系。

為什么SFDR在通信中很重要?通常,傳輸?shù)?a target="_blank">信息與其他通信信道和應(yīng)用程序共享頻譜/帶寬(例如,通過(guò)公共電纜廣播或傳輸?shù)牟煌娨曨l道,蜂窩系統(tǒng)中的不同呼叫者,不同的FM廣播電臺(tái)等)。如果發(fā)射器將雜散信號(hào)發(fā)送到其他頻段,它們可能會(huì)損壞、中斷或消除相鄰信號(hào)。這被認(rèn)為是不好的做法,違反了FCC(和其他監(jiān)管機(jī)構(gòu))的規(guī)定,并可能導(dǎo)致法律訴訟。

TxDAC系列在奈奎斯特頻段的SFDR從時(shí)鐘頻率為100 MSPS并產(chǎn)生40 MHz輸出信號(hào)時(shí)的57 dB(10位AD9760)到78 dB(時(shí)鐘頻率為20 MSPS,產(chǎn)生2 MHz輸出)(14位AD9764)。表1顯示了AD9760、AD9762和AD9764在不同時(shí)鐘速率和輸出頻率下的典型SFDR和THD規(guī)格。雖然 12 位和 14 位器件為滿量程正弦波提供類似的 SFDR,但更高分辨率器件對(duì)于具有高峰均比和大量低電平內(nèi)容的信號(hào)具有更好的 SFDR。圖3顯示了12位AD9762奈奎斯特范圍內(nèi)的典型頻譜圖,輸出由時(shí)鐘速率為100 MSPS的單個(gè)20 MHz信號(hào)組成;圖中為60.8 dB的二次諧波,其余雜散為<75 dB。在大多數(shù)窄帶應(yīng)用中,諧波被濾除,“一個(gè)窗口”或“無(wú)諧波”內(nèi)的SFDR才是最重要的。在這種情況下,TxDAC系列提供80 dB范圍內(nèi)的性能,即使對(duì)于10位AD9760,時(shí)鐘頻率為100 MSPS的5 MHz范圍內(nèi)的輸出也是如此。

在寬帶應(yīng)用中,DAC將在其輸出端產(chǎn)生多個(gè)信號(hào),雙音或多音性能尤其令人感興趣。突出的應(yīng)用是通過(guò)電纜同時(shí)發(fā)送兩個(gè)或多個(gè)數(shù)據(jù)/語(yǔ)音/視頻通道。寬帶蜂窩基站是另一個(gè),除此之外,還有ADSL(非對(duì)稱數(shù)字用戶線)等應(yīng)用,它利用基于多音調(diào)的離散調(diào)制方案,并依賴于良好的多音性能。

| 表 1.典型的 SFDR 和 THD 規(guī)格 | |||

| SFDR | AD9760 | AD9762 | AD9764 |

|

FC=50兆赫;F外=5.05 MHz 至奈奎斯特 |

67分貝 |

70分貝 |

70分貝 |

|

FC=50兆赫;F外=20.2 MHz 至奈奎斯特 |

642分貝 |

67分貝 |

67分貝 |

|

FC=100兆赫;F外=5.05 MHz 至奈奎斯特 |

61分貝 |

64分貝 |

64分貝 |

| FC=100兆赫;F外=40.4 MHz 至奈奎斯特 | 57分貝 | 60分貝 |

60分貝 |

| FC=50兆赫;F外=5.05兆赫;2 兆赫跨度 | 84分貝 | 84分貝 | 84分貝 |

| FC=100兆赫;F外=5.05兆赫;2 兆赫跨度 | 84分貝 | 84分貝 | 84分貝 |

| 諧波失真 | |||

| FC=50兆赫;F外=5.05兆赫 |

-61 分貝 |

-64 分貝 |

-64 分貝 |

| FC=100兆赫;F外=5.05 |

-57 分貝 |

-60 分貝 |

-60 分貝 |

圖3.以 100 MSPS 采樣的 19.96MHz 正弦波;差分輸出,50(歐姆),20 pf,SFDR = 60.8 dB。

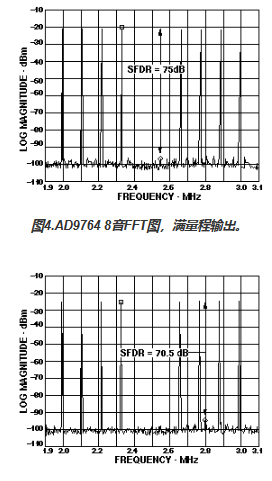

在大多數(shù)多音應(yīng)用中,發(fā)射路徑DAC的輸出通常在滿量程范圍的一小部分(例如,1/2或1/4 FS)下工作,以確保DAC輸出不會(huì)與接近滿量程的所有通道削波(削波發(fā)射波形產(chǎn)生的諧波可能導(dǎo)致非法“飛濺”)。圖4和圖5分別顯示了AD9764滿量程和半量程8音波形的頻譜圖;兩者都表示SFDR>70 dBc,這是創(chuàng)新轉(zhuǎn)換器架構(gòu)的重要結(jié)果。TxDAC系列的各種型號(hào)已經(jīng)針對(duì)在單音測(cè)試中表現(xiàn)相當(dāng)?shù)腂iCMOS DAC進(jìn)行了測(cè)量;TxDAC在多音應(yīng)用中實(shí)現(xiàn)了可重復(fù)的更好性能。這可能與廣泛使用的R-2R梯形網(wǎng)絡(luò)架構(gòu)引起的時(shí)序偏差有關(guān),TxDAC專有的電流開(kāi)關(guān)架構(gòu)已經(jīng)過(guò)優(yōu)化以最小化。

圖5.AD9764 8音FFT圖,1/2電平輸出。

TxDAC 內(nèi)核中使用的開(kāi)關(guān)電路提供真正的差分輸出,從而在差分使用器件時(shí)提高性能。盡管TxDAC系列的單端性能本身非常出色,但當(dāng)輸出通過(guò)變壓器差分驅(qū)動(dòng)時(shí),可以實(shí)現(xiàn)最佳的諧波性能。表2顯示了12位AD9762的差分性能比單端性能的改善,特別是在較高頻率下。

| 表 2.AD9762 無(wú)雜散動(dòng)態(tài)范圍,fs = 125 MSPS | ||

| 單音 | 單端 | 微分 |

|

1兆赫 |

70分貝 |

72分貝 |

|

5兆赫 |

63分貝 |

70分貝 |

|

10兆赫 |

58分貝 |

65分貝 |

| 39兆赫 | 46分貝 | 54分貝 |

每個(gè)DAC采用+5 V單電源供電,時(shí)鐘頻率為100 MSPS,功耗為150 mW,配置為20 mA滿量程電流輸出。時(shí)鐘頻率為40 MSPS,采用+3 V單電源供電,配置為2 mA滿量程輸出,功耗降至極低的35 mW。每個(gè)器件都支持睡眠模式,當(dāng)DAC不工作時(shí),功耗從+5 V降至<30 mW。

在許多情況下,數(shù)字通信系統(tǒng)的品質(zhì)因數(shù)是其誤碼率(BER)。誤碼率通常由適當(dāng)?shù)臉?biāo)準(zhǔn)/規(guī)范決定,并受模擬元件性能、傳輸介質(zhì)、調(diào)制方案、數(shù)據(jù)速率以及可用的均衡和糾錯(cuò)電路的組合影響。各種不同的無(wú)線和有線應(yīng)用(包括用于蜂窩、PCS、尋呼機(jī)、無(wú)線本地環(huán)路和衛(wèi)星服務(wù)的無(wú)線基站和終端,以及用于互聯(lián)網(wǎng)接入的有線調(diào)制解調(diào)器、交互式視頻機(jī)頂盒和數(shù)字用戶線路,如 ADSL、HDSL、VDSL 等)使用許多不同的調(diào)制方案,適應(yīng)不同的數(shù)據(jù)速率,并需要不同的系統(tǒng)級(jí)性能。

在這些情況下,由于與DAC性能缺乏獨(dú)特的關(guān)系,通信系統(tǒng)設(shè)計(jì)人員很難確定轉(zhuǎn)換器所需的分辨率/動(dòng)態(tài)范圍。幸運(yùn)的是,TxDAC的引腳兼容尺寸允許在開(kāi)發(fā)周期的任何階段進(jìn)行性價(jià)比權(quán)衡,并為未來(lái)更高性能的系統(tǒng)提供了升級(jí)途徑。系統(tǒng)設(shè)計(jì)人員可以靈活地在誤碼率性能與系統(tǒng)成本之間進(jìn)行權(quán)衡。該選擇允許設(shè)計(jì)人員適應(yīng)一定的誤差范圍,補(bǔ)償均衡和糾錯(cuò)方法和性能。此外,由于給定調(diào)制方案的數(shù)據(jù)速率與帶寬和動(dòng)態(tài)范圍成正比,因此設(shè)計(jì)人員可以在高端器件上提供更高的數(shù)據(jù)速率。

兩種基本的發(fā)射架構(gòu)如圖6和圖7所示。在基于正交的調(diào)制方案中,例如QPSK和QAM,部署混頻器以將同相(I)和正交(Q-90度異相)信號(hào)混合成復(fù)合單邊帶信號(hào)以進(jìn)行傳輸。圖6所示為基帶發(fā)射架構(gòu),該架構(gòu)可模擬I和Q信號(hào)混合。在本例中,每個(gè)發(fā)射通道需要兩個(gè)DAC。即使在許多基帶應(yīng)用中使用的低輸出頻率下,TxDAC系列也是最佳選擇,因?yàn)樵撓盗械乃谐蓡T在低輸出頻率下都結(jié)合了(1)高SFDR;(2)低功耗,單電源和3V操作,提高系統(tǒng)電源效率;(3)有競(jìng)爭(zhēng)力的價(jià)格(通過(guò)對(duì)信號(hào)進(jìn)行過(guò)采樣(插值)來(lái)減少DAC的帶內(nèi)混疊鏡像,從而減輕低通濾波器的工作,從而進(jìn)一步降低總成本);(4) 同一引腳布局中提供的各種分辨率允許最終的成本/性能權(quán)衡。例如,在許多 TxDAC 測(cè)試版站點(diǎn)應(yīng)用程序中,用戶從一個(gè)分辨率模型開(kāi)始,然后根據(jù)實(shí)際系統(tǒng)性能設(shè)計(jì)更高或更低分辨率的設(shè)備。

圖6.具有模擬正交混頻的基帶發(fā)射架構(gòu)。

圖7中的系統(tǒng)架構(gòu)使用I和Q信號(hào)的數(shù)字混頻,并將調(diào)制信號(hào)直接輸入到單個(gè)DAC。在這種情況下,DAC的帶寬要求更加嚴(yán)格。通過(guò)數(shù)字調(diào)制,可以通過(guò)TxDAC芯片產(chǎn)生40 MHz范圍內(nèi)的中頻(IF)。這足以直接傳輸高速調(diào)制解調(diào)器中的數(shù)據(jù)和交互式機(jī)頂盒中的上游信息。在其他應(yīng)用中,它可以消除上變頻器級(jí)。在這里,高SFDR、低價(jià)格、低功耗和系列引腳兼容性也是理想的(必需)屬性。如果將多個(gè)數(shù)字I&Q調(diào)制器饋入圖7所示的單個(gè)DAC,則系統(tǒng)將對(duì)應(yīng)于寬帶發(fā)射架構(gòu),為此,TxDAC系列產(chǎn)品的卓越多音性能是一個(gè)主要的性能屬性。

10位AD9760正在進(jìn)入高速互聯(lián)網(wǎng)數(shù)據(jù)調(diào)制解調(diào)器和交互式機(jī)頂盒,其中SFDR要求在50 dB范圍內(nèi),輸出頻率為40 MHz,時(shí)鐘速率高達(dá)120 MSPS。它們還用于無(wú)線本地環(huán)路和高速無(wú)線集群基站。這些 12 位器件被設(shè)計(jì)用于蜂窩和個(gè)人通信服務(wù) (PCS) 基站、電纜頭端設(shè)備和混合光纖同軸調(diào)制解調(diào)器,在這些器件中,在不同的時(shí)鐘和采樣速率下需要高達(dá) 70 dB 的 SFDR。14位AD9764正在ADSL調(diào)制解調(diào)器和下一代PCS基站中找到一>,在這些基站中,1 MHz至6 MHz信號(hào)需要70 dB<時(shí)鐘速率為15 MSPS。

圖7.具有數(shù)字調(diào)制的傳輸架構(gòu)。

用于普通CMOS制造的芯片設(shè)計(jì)的一個(gè)主要優(yōu)勢(shì)是數(shù)字集成兼容性。TxDAC內(nèi)核基于CMOS工藝進(jìn)行了優(yōu)化,可實(shí)現(xiàn)與數(shù)字信號(hào)處理(DSP)電路的高效集成,從而進(jìn)一步節(jié)省電路板和成本,并增強(qiáng)性能和可靠性。通過(guò)將數(shù)字處理與DAC內(nèi)核集成,可以實(shí)現(xiàn)比以往任何時(shí)候都更高速的數(shù)字切換。

例如,在使用數(shù)字DDS引擎和高性能(雙極性)DAC的傳統(tǒng)雙芯片直接數(shù)字合成(DDS)系統(tǒng)中,速度和分辨率受到將數(shù)字?jǐn)?shù)據(jù)從DDS芯片時(shí)鐘傳輸?shù)紻AC所需的速度和功率的限制(TTL邏輯限制為約100 MSPS)。通過(guò)將DDS電路與DAC集成,內(nèi)部數(shù)據(jù)速率將>200 MSPS可用且經(jīng)濟(jì)。除了單芯片高性能DDS(見(jiàn)第12頁(yè))外,未來(lái)的片上數(shù)字電路還將包括數(shù)字調(diào)制器和插值濾波器。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

184文章

17586瀏覽量

249502 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8627瀏覽量

146872 -

變頻器

+關(guān)注

關(guān)注

251文章

6504瀏覽量

144259

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

HV857已針對(duì)各種應(yīng)用進(jìn)行了優(yōu)化

AD9637-80EBZ,在小封裝尺寸至關(guān)重要的應(yīng)用中針對(duì)出色的動(dòng)態(tài)性能和低功耗進(jìn)行了優(yōu)化

采用AD9114雙路低功耗8位TxDAC的AD9114-EBZ評(píng)估板

DC2103A演示電路針對(duì)低啟動(dòng)電壓進(jìn)行了優(yōu)化,采用100:1匝數(shù)比變壓器

MIKROE-2815,基于MAX31865電阻數(shù)字轉(zhuǎn)換器,針對(duì)鉑電阻溫度檢測(cè)器或RTD進(jìn)行了優(yōu)化

AD9481-PCB,AD9481評(píng)估板是一款8位,單芯片模數(shù)轉(zhuǎn)換器(ADC),針對(duì)高速和低功耗進(jìn)行了優(yōu)化

對(duì)結(jié)構(gòu)體成員進(jìn)行了賦值

RS通信編碼器怎么進(jìn)行優(yōu)化設(shè)計(jì)?

請(qǐng)問(wèn)一下Arm Cortex-M85性能的提升是對(duì)總線進(jìn)行了優(yōu)化嗎?

STM32CubeIDE是否針對(duì)新MAC中的Apple M1芯片進(jìn)行了優(yōu)化?

TxDAC系列高速DAC的引腳兼容性

PRIZM LightTurn機(jī)械光學(xué)接口針對(duì)25Gbps及更高速率的鏈路進(jìn)行了優(yōu)化

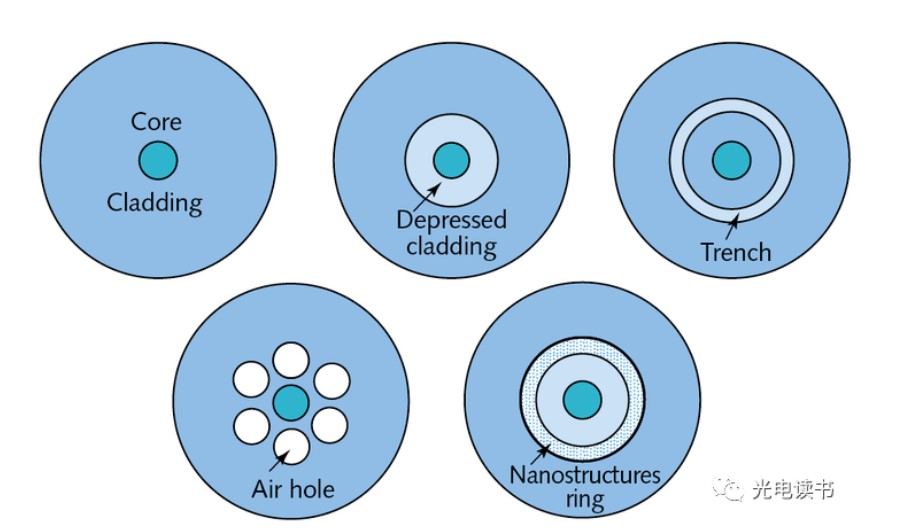

針對(duì)特定應(yīng)用定制化的光纖

LNA針對(duì)全球定位系統(tǒng)進(jìn)行了優(yōu)化

石墨烯基導(dǎo)電油墨具有良好的滲透性和低阻抗,針對(duì) RFID天線性能進(jìn)行了優(yōu)

DAC針對(duì)通信傳輸路徑進(jìn)行了優(yōu)化

DAC針對(duì)通信傳輸路徑進(jìn)行了優(yōu)化

評(píng)論