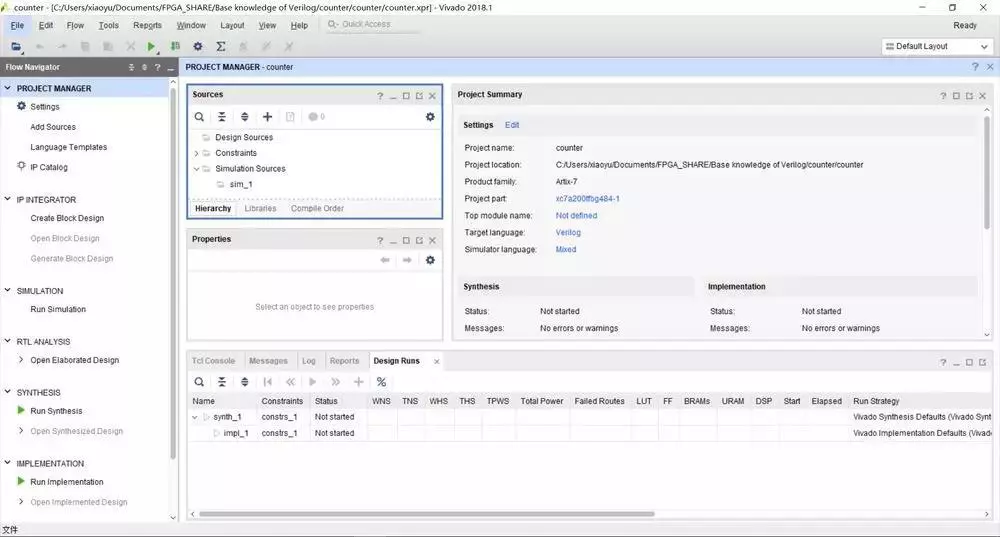

在Vivado Design Suite中,Vivado綜合能夠合成多種類型的屬性。在大多數情況下,這些屬性具有相同的語法和相同的行為。

?如果Vivado綜合支持該屬性,它將使用該屬性,并創建反映已使用屬性的邏輯。

?如果工具無法識別指定的屬性,則Vivado綜合會將屬性及其值傳遞給生成的網表。

1.ASYNC_REG

ASYNC_REG是影響Vivado工具流中許多進程的屬性。此屬性的目的是通知工具寄存器能夠在D輸入引腳中接收相對于源時鐘的異步數據,或者該寄存器是同步鏈中的同步寄存器。

當遇到此屬性時,Vivado綜合會將其視為DONT_TOUCH屬性,并在網表中向前推送ASYNC_REG屬性。此過程可確保具有ASYNC_REG屬性的對象未進行優化,并且流程中稍后的工具會接收屬性以正確處理它。

您可以將此屬性放在任何寄存器上;值為FALSE(默認值)和TRUE。可以在RTL或XDC中設置此屬性。

ASYNC_REG Verilog Example:

(*ASYNC_REG = “TRUE” *) reg [2:0] sync_regs;

2.CLOCK_BUFFER_TYPE

在輸入時鐘上應用CLOCK_BUFFER_TYPE以描述要使用的時鐘緩沖器類型。

默認情況下,Vivado綜合使用BUFG作為時鐘緩沖器。支持的值是“BUFG”,“BUFH”,“BUFIO”,“BUFMR”,“BUFR”或“無”。CLOCK_BUFFER_TYPE屬性可以放在任何頂級時鐘端口上。它可以在RTL和XDC中設置。

CLOCK_BUFFER_TYPE Verilog Example

(* clock_buffer_type = “none”*) input clk1;

CLOCK_BUFFER_TYPE XDC Example

set_property CLOCK_BUFFER_TYPEBUFG [get_ports clk]

3 FSM_ENCODING

FSM_ENCODING控制狀態機上的編碼。通常,Vivado工具會根據最適合大多數設計的啟發式方法為狀態機選擇編碼協議。某些設計類型使用特定的編碼協議可以更好地工作

FSM_ENCODING可以放在狀態機寄存器上。其合法價值是“one_hot”,“sequential”,“johnson”,“grey”,“auto”和“none”。“auto”值是默認值,允許工具確定最佳編碼。可以在RTL或XDC中設置此屬性。

FSM_ENCODING Example (Verilog)

(* fsm_encoding = “one_hot” *)reg [7:0] my_state;

4 KEEP

使用KEEP屬性可防止信號優化或被吸收到邏輯塊中的優化。此屬性指示綜合工具保持其所處的信號,并將該信號放入網表中。

例如,如果信號是2位AND門的輸出,并且它驅動另一個AND門,則KEEP屬性可用于防止該信號合并到包含兩個AND門的較大LUT中。

KEEP也常用于時序約束。如果對通常會優化的信號存在時序約束,KEEP會阻止該操作,并允許使用正確的時序規則

KEEP Example (Verilog)

(* keep = “true” *) wire sig1;

assign sig1 = in1 & in2;

assign out1 = sig1 & in2;

5 RAM_STYLE

RAM_STYLE指示Vivado綜合工具如何推斷內存。可接受的值是:

?block:指示工具推斷RAMB類型組件。

?distributed:指示工具推斷LUT RAM。

?寄存器:指示工具推斷寄存器而不是RAM。

?ultra:指示工具使用UltraScale +URAM原語。

默認情況下,該工具根據啟發式選擇要推斷的RAM,以便為大多數設計提供最佳結果。將此屬性放在為RAM聲明的數組或層次結構級別上。

?如果設置了信號,該屬性將影響該特定信號。

?如果設置在層次結構級別上,則會影響該層次結構級別中的所有RAM。

層次結構的子級別不受影響。

這可以在RTL或XDC中設置。

RAM_STYLE Example (Verilog)

(* ram_style = “distributed” *)reg [data_size-1:0] myram [2**addr_size-1:0];

6 ROM_STYLE

ROM_STYLE指示綜合工具如何推斷ROM存儲器。可接受的值是:

?block:指示工具推斷RAMB類型組件

?distributed:指示工具推斷LUT ROM。默認情況下,該工具根據啟發式選擇要推斷的ROM,以便為大多數設計提供最佳結果。

這可以在RTL和XDC中設置。

ROM_STYLE Example (Verilog)

(* rom_style = “distributed” *)reg [data_size-1:0] myrom [2**addr_size-1:0];

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5250瀏覽量

119180 -

HDL

+關注

關注

8文章

324瀏覽量

47228 -

觸發器

+關注

關注

14文章

1990瀏覽量

60862 -

數字邏輯電路

+關注

關注

0文章

100瀏覽量

15739 -

SRL

+關注

關注

0文章

5瀏覽量

6710

原文標題:xilinx verilog 語法技巧

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

硬件描述語言(HDL)編碼技術:xilinx verilog語法技巧

深入理解FPGA Verilog HDL語法(一)

科普一下ZYNQ是什么

Verilog_HDL的基本語法詳解(夏宇聞版)

科普一下MTU是什么,如何設置MTU

科普一下xilinx verilog語法技巧

科普一下xilinx verilog語法技巧

評論