寄存器對于學習集成電路知識十分重要,不管是單片機亦或是現代計算機的CPU離開寄存器都無法快速的進行操作。

1、寄存器

寄存器是處理器中用來存儲數據指令的電子元部件。例如在PC中數據由硬盤讀取到內存,當CPU發起請求后數據由內存轉儲到CPU緩存中。

CPU緩存是SRAM,位于處理器內部,與ALU通過數據總線連接,物理距離S~S~是所有存儲設備中最短的。

在前文中我們探究了內存的機理,內存由DRAM組成,每位DRAM由一個MOS管與電容構成,而電容充電充電時間常數的大小與電路的電阻有關,按照下式計算:

其中R是電阻;C是電容。

電路電阻和電容決定了DRAM響應速度有最大極限,SRAM由觸發器組成,沒有如電容、電感類的元器件,那么我們可以通過麥克斯韋電磁學方程對導體中電流速度進行定量描述。

電流在無損耗下,SRAM速度為真空中光速,考慮到電路中的阻抗,速度遠小于C。并可得出以下公式:

其中 為電子在阻抗電路中移動速度;Z是阻抗;

為電子在阻抗電路中移動速度;Z是阻抗; 分別是SRAM速度、DRAM速度;S為與ALU距離。

分別是SRAM速度、DRAM速度;S為與ALU距離。

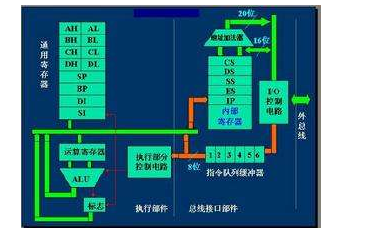

2、寄存器電路結構

寄存器由觸發器與鎖存器組成,觸發器負責儲存數據,鎖存器負責保持數據。

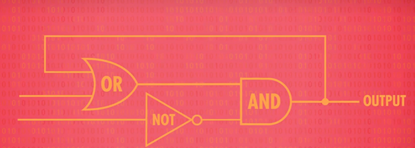

我們制造一個由或門構成的反饋電路,如圖①。

0 OR 0 = 0;經反饋為0;

1 OR 0 = 1;& 1 OR 0 = 1;經反饋后為1;

1 OR 1 = 1;經反饋后為1;

在此電路中一旦輸出為1不管如何改變A都無法改變輸出。此電路正好可以用作記錄1的電路。

同樣的,如果我們用與門構建反饋電路。

1 AND 1 =1;經反饋后輸出1。

0 AND 0 = 0;0 AND 1 = 0;1 AND 0 = 0;經反饋后都為0。

在此電路中一旦輸出為0不管如何改變A都無法改變輸出。此電路正好可以用作記錄0的電路。

此時將兩個電路以下圖方式組合起來便稱為:AND-OR鎖存器。

它有兩個輸入,SET 將輸出置1,RESET輸出置0。

SET = 1;RESET = 1;OUTPUT = 0;

SET = 1;RESET = 0;OUTPUT = 1;

SET = 0;RESET = 1;OUTPUT = 0;

SET = 0;RESET = 0;OUTPUT = 之前數據,也就說電路將數據鎖存起來了。

之所以叫“鎖存”,是因為它“鎖定”一個數據并保存狀態。將數據放入叫:寫入;數據輸出叫:讀取。

如果SET與RESET兩根線不容易記憶,那么可以使用一些邏輯門構成數據輸入與寫入使能。

將相關電路封裝起來,并使用線矩陣進行連接就可以支持多位數據位輸入輸出。

處理器中寄存器有很多,為了方便使用,我們一般將寄存器編號、命名。名字對應寄存器功能,寄存器編號對應寄存器地址。

3、寄存器慣常用法

我們本次匯編學習是基于80386進行的。

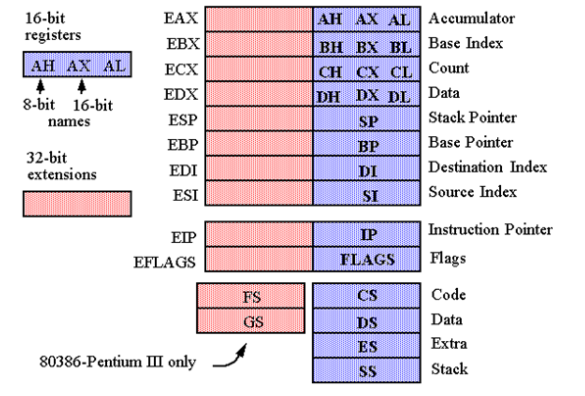

80386共提供7種類型的32位寄存器,如下:

通用寄存器(EAX、EBX、ECX、EDX、ESP、EBP、ESI、EDI)

段寄存器(CS、SS、DS、ES、FS、GS)

指令指針寄存器和標志寄存器(EIP、EFLAGS)

控制寄存器(CR0、CR1、CR2、CR3、CR4)

調試寄存器(DR0、DR1、DR2、DR3、DR4、DR5、DR6、DR7)

** 測試寄存器(TR6、TR7)**

一、通用寄存器

一組八個通用寄存器是對8086/80286通用寄存器的32位擴展,其用法與在8086/80286中相似,支持8位、16位、32位操作,進行32位操作是,寄存器名稱前面冠以“E”。

這八個寄存器的名稱如下:EAX(累加器)、EBX(基址)、ECX(計數)、EDX(數據)、ESP(棧指針)、EBP(基址指針)、ESI(源變址)、EDI(目的變址)。

二、段寄存器

80386比8086/80286增加了兩個段寄存器FS、GS。

除CS支持代碼段,SS支持堆棧段外,程序員可以利用其它的所有段寄存器支持數據段。

每個段寄存器對應這一個64位高速緩存器(有些資料中說有96位,但值使用其中的64位),這在8086中是沒有的(在80286中為48位),它的具體作用將另文介紹。

三、指令指針寄存器和標志寄存器

指令寄存器EIP是對8086/80286指令指針寄存器的32位擴展,它包含著待執行指令的32位偏移量,該值總是相對CS所代表的段基址而言的。

**IOPL** (I/O Privilege Level)是從80286開始出現的,占2個bit表示I/O特權級,如果當前特權級小于或等于IOPL,則可以執行I/O操作,否則將出現一個保護性異常。IOPL只能由特權級為0的程序或任務來修改。

**NT** (Nested Task)也是從80286開始出現的,表示嵌套任務,用于控制中斷返回指令IRET,當NT=0時,用堆棧中保存的值恢復EFLAGS、CS和EIP,從而實現返回;若NT=1,則通過任務切換實現中斷返回。

下面的標志位是80386以后的CPU才有的標志。

**VM** (Virtual-8086 mode)表示虛擬8086模式,如果VM被置位且80386已出于保護模式下,則CPU切換到虛擬8086模式,此時,對段的任何操作又回到了實模式,如同在8086下運行一樣。

RF(Resume flag)表示恢復標志(也叫重啟標志),與調試寄存器一起用于斷點和單步操作,當RF=1 時,下一條指令的任何調試故障將被忽略,不產生異常中斷。當RF=0時,調試故障被接受,并產生異常中斷。用于調試失敗后,強迫程序恢復執行,在成功執行每條指令后,RF自動復位。

**AC** (Alignment check)表示對齊檢查。這個標志是80486以后的CPU才有的。當AC=1且CR0中的AM=1時,允許存儲器進行地址對齊檢查,若發現地址未對齊,將產生異常中斷。所謂地址對齊,是指當訪問一個字(2字節長)時,其地址必須是偶數(2的倍數),當訪問雙字(4字節長)時,其地址必須是4的倍數。

但是只有運行在特權級3的程序才執行地址對齊檢查,特權級0、1、2忽略該標志。

**VIF** (Virtual interrupt flag)表示虛擬中斷標志。以下的三個標志是Pentium以后的CPU才有的。當VIF=1時,可以使用虛擬中斷,當VIF=0時不能使用虛擬中斷。該標志要和下面的VIP和CR4中的VME配合使用。

**VIP** (Virtual interrupt pending flag)表示虛擬中斷掛起標志。當VIP=1時,VIF有效,VIP=0時VIF無效。

**ID** (Identification flag)表示鑒別標志。該標志用來只是Pentium CPU是否支持CPUID的指令。

實際上,如果不編寫操作系統,大部分標志可能很難得用到一次,有個印象就好了,用到了再去查不遲。

四、系統表寄存器

80386 中有4個系統表寄存器,分別是全局描述符表寄存器(GDTR)、中斷描述符表寄存器(IDTR)、局部描述符表寄存器(LDTR)、任務狀態寄存器(TR)。系統表寄存器用于在保護方式下,管理4 個系統表,由于只能在保護方式下使用,因此又稱為保護方式寄存器。有關描述附表的問題,另文介紹。

五、控制寄存器

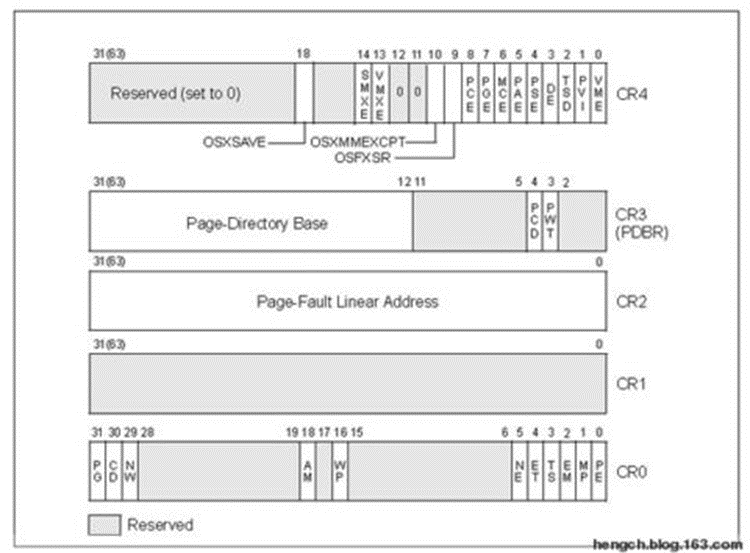

80386的控制寄存器有4個,其中CR1保留以后使用,從Pentium開始,又增加了一個CR4,CR0的低16位包含了與80286的MSW一致的位定義,保持了和80286的兼容,同時也兼容了從80286開始的兩條指令LMSW/SMSW,其基本定義如下:

CR0中各位含義如下:

·PE (Protection Enable)保護模式允許,PE=0表示CPU工作在實模式,PE=1表示CPU工作在保護模式

·MP (Monitor Coprocessor)監控協處理器,MP=1表示協處理器在工作,MP=0表示協處理器未工作。

·EM (Emulation)協處理器仿真,當MP=0,EM=1時,表示正在使用軟件仿真協處理器工作。

·TS (Task Switched)任務轉換,每當進行任務轉換時,TS=1,任務轉換完畢,TS=0。TS=1時不允許協處理器工作。

以上4個定義從80286開始,下面的2個定義從80386開始存在

·ET (Extension Type)處理器擴展類型,反映了所擴展的協處理器的類型,ET=0為80287,ET=1為80387。

·PG (Paging)頁式管理機制使能,PG=1時頁式管理機制工作,否則不工作。

從80486開始又增加了如下位定義。

·NE (Numeric Error)數值異常中斷控制,NE=1時,如果運行協處理器指令發生故障,則用異常中斷處理,NE=0時,則用外部中斷處理。

·WP (Write Protect)寫保護,當WP=1時,對只讀頁面進行寫操作會產生頁故障。

·AM(Alignment Mask)對齊標志,AM=1時,允許對齊檢查,AM=0時不允許,關于對齊,在EFLAGS的AC標志時介紹過,在80486以后的CPU中,CPU進行對齊檢查需要滿足三個條件,AC=1、AM=1并且當前特權級為3。

·NW (Not Write-through)和CD(Cache Disable),這兩個標志都是用來控制CPU內部的CACHE的,當NW=0且CD=0時,CACHE使能,其它的組合說起來比較復雜,如果有讀者真的想搞清楚的話,可以參閱《Intel? 64 and IA-32 Architectures》中的“Software Developer’s Manual Volume 3A”這一冊,在第10章對這兩個標志的各種組合有比較詳細的說明。

CR1保留未用;CR2存放引起頁故障的線性地址,只有在PG=1時,CR2才有效,當頁故障處理程序被激活時,壓入頁故障處理程序堆棧中的錯誤碼提供頁故障的狀態信息。

CR3的bit12--bit31存放頁目錄的基地址,因為也目錄總是頁對齊的(一頁為4K),所以頁目錄基地址從bit12開始就可以了。只有當CR0中的PG=1時,CR3的頁目錄基地址才有效。

從80486開始,在CR3的低12位定義了兩個控制位,如下:

·PCD (Page-level Cache Disable)頁CACHE禁止,當PCD=0時,頁目錄表進行高速緩存,PCD=1時,不進行高速緩存;該位控制PCD引腳控制外部CACHE工作還是不工作。

·PWT (Page-level Writes Transparent),CACHE的寫入分為透寫(Write-Through)和回寫(Write-Back),80486以上的CPU內部的CACHE都是透寫的,但對外部CACHE而言,允許某些頁是回寫的,而另一些頁是透寫的,當PWT=1時,外部CACHE對頁目錄進行透寫,否則進行回寫;此位驅動PWT引腳以控制外部CACHE是透寫還是回寫。

CR4是從Pentium CPU開始出現的。

·VME (Virtual-8086 Mode Extensions)虛擬8086方式擴展,VME=1允許使用虛擬8086擴展模式,否則只能使用80386/80486的虛擬8086模式。

·PVI (Protected-Mode Virtual Interrupts)保護模式虛擬中斷,PVI=1時,在保護模式下支持虛擬中斷標志VIF(EFLAGS中),PVI=0則不支持虛擬中斷標志。

·TSD (Time Stamp Disable)時間戳禁止,TSD=1時,允許在特權級為0的程序中執行RDTSC指令(讀時間戳計數指令),TSD=0時,允許任何特權級執行RDTSC指令。

·DE (Debugging Extensions)調試擴展,

·PSE (Page Size Extensions)頁大小擴展,PSE=1時,頁大小可以擴展到2M或4M,PSE=0時,頁大小只能是4K.

·PAE (Physical Address Extension)物理地址擴展,PAE=1時,頁物理地址可以擴展到36bits以上,PAE=0時只能用32bits的物理地址。

·MCE (Machine-Check Enable)硬件檢查使能,Pentium以后的CPU有一種硬件檢測功能,MCE=1時允許使用該功能。

·PGE (Page Global Enable)全局頁使能,PGE=1時,允許使用全局頁,PGE=0時禁止使用全局頁。

·PCE (Performance-Monitoring Counter Enable)性能監視計數器使能,當PCE=1時,允許在任何保護級下執行RDPMC指令,PCE=0時,只有特權級0的程序可以執行RDPMC指令。

·OSFXSR (Operating System Support for FXSAVE and FXRSTOR instructions)

·OSXMMEXCPT (Operating System Support for Unmasked SIMD Floating-Point Exceptions)

·VMXE (VMX-Enable Bit)VMX使能位,VMXE=1時,允許VMX操作。

·SMXE (SMX-Enable Bit)SMX使能位,SMXE=1時,允許SMX操作。

·OSXSAVE (XSAVE and Processor Extended States-Enable Bit)

六、調試寄存器

一共有8個調試寄存器DR0--DR7,DR0-DR3可以分別設置4個斷點的線性地址,DR4-DR5保留未用,DR6是斷點狀態寄存器,DR7是斷點控制寄存器(包括斷點類型、斷點長度,斷點開放/禁止)

七、測試寄存器

一共有8個測試寄存器TR0--TR7,TR0-TR2保留,TR3-TR5用作CACHE測試,TR6為命令測試寄存器,TR7為測試數據寄存器。

參考文獻:

1、 INTEL 80386 PROGRAMMER'S REFERENCE MANUAL 1986 (mit.edu)

2、 https://www.cnblogs.com/darknife/p/3159059.html

-

集成電路

+關注

關注

5381文章

11389瀏覽量

360879 -

寄存器

+關注

關注

31文章

5321瀏覽量

120016 -

cpu

+關注

關注

68文章

10826瀏覽量

211160

發布評論請先 登錄

相關推薦

定時器A各寄存器的用法以及功能

ADC0809用法詳解_引腳圖及功能_工作原理_內部結構及應用電路

Java數組的常用方法_Java:數組工具類Arrays類的常用方法的用法及代碼

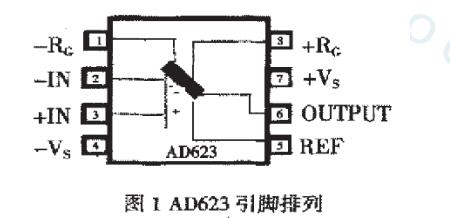

ad623典型電路用法介紹_ad623結構與工作原理

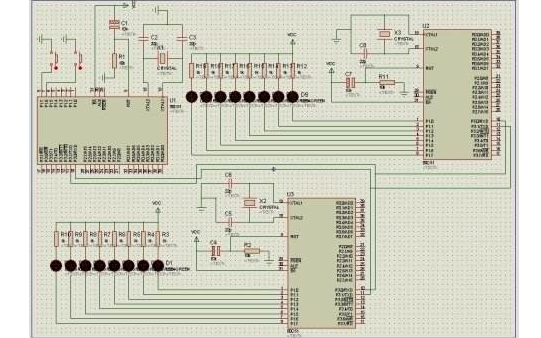

51單片機的原理,指令,寄存器,以及接口

探究寄存機的電路結構以及慣常用法

探究寄存機的電路結構以及慣常用法

評論