本文介紹一系列即插即用D類放大器,通過消除通常對I的需求來簡化系統設計2C 編程、低抖動采樣時鐘、邏輯電平轉換器、精心設計的電路板設計或 EMI 濾波。它將解釋如何在提供高性能音頻的同時節省板載空間、成本和精力。

介紹

新一代即插即用數字輸入D類音頻放大器的音頻性能遠遠優于傳統的模擬D類放大器。更重要的是,數字輸入D類放大器具有降低功耗、復雜性、噪聲和系統成本等額外優勢。

電子產品供應商通常使用高效、無濾波器、模擬輸入 D 類放大器來管理手機、平板電腦、家庭監控和智能揚聲器中便攜式音頻揚聲器的功率要求。這些 D 類放大器允許直接連接到電池,從而最大限度地減少損耗并減少元件數量。這些放大器還實現了>80 dB PSRR性能,這對于避免217 Hz解調GSM信號發出嗡嗡聲非常重要。

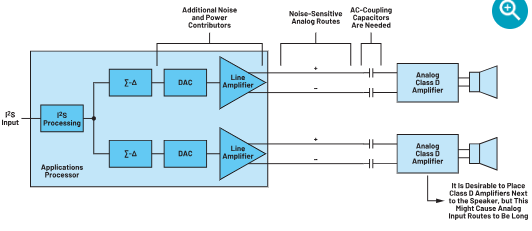

模擬輸入D類放大器通常需要應用處理器上的DAC和線路驅動器放大器(圖1),這會增加揚聲器輸出的芯片成本、功耗和噪聲。這些D類放大器還需要仔細的電路板設計,以避免由于信號耦合到模擬板路徑而退化。

圖1.帶有模擬輸入 D 類揚聲器放大器的傳統系統。應用處理器上的DAC和線路驅動器放大器會增加揚聲器輸出的芯片成本、功耗和噪聲。

數字輸入D類音頻放大器不受大多數電路板設計問題的影響。單通道D類放大器可以放置在電路板上的遠程位置,以最大限度地減少大電流電池和揚聲器負載連接的布線。這些放大器不需要模擬輸入D類設計的DAC和線路驅動器放大器。因此,空間和系統成本下降,設計更簡單。

簡化的系統設計

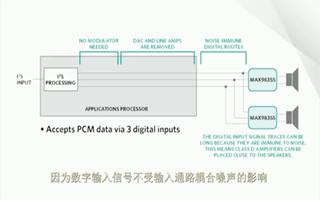

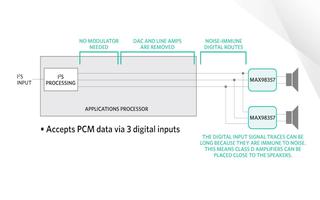

大多數數字輸入放大器接受脈沖編碼調制 (PCM) 或 I2S 數據,需要三根電線:BCLK、LRCLK 和 DIN。PCM 數據格式不需要調制器或應用處理器上的數據上采樣(圖 2)。PCM輸入放大器的一些較舊實現方案還需要一個干凈的主時鐘(MCLK)來獲得無抖動的采樣時鐘。較新的PCM輸入放大器,如MAX98357、MAX98360和MAX98365不再需要MCLK輸入,因此引腳數、功耗和電路板復雜性都降低了。

圖2.具有PCM輸入D類揚聲器放大器的系統使用三根線,但不需要調制器或應用處理器上數據的上采樣。

較舊的數字輸入放大器提供可調的采樣速率和/或位深度,在某些情況下,需要對放大器進行復雜的編程。新一代數字輸入放大器可自動檢測各種采樣速率和位深度,無需任何編程即可自行配置。

在多通道實現中,數字輸入D類音頻放大器減少了電路板上外部電容和布線線路的數量。PCM 輸入只需要 BCLK、LRCLK 和 DIN 線路即可提供立體聲或 8 通道 TDM 數據。相比之下,立體聲模擬輸入D類放大器通常需要兩個差分輸入信號(四根線)與交流耦合電容進行布線(見圖1和圖2)。

大多數數字輸入放大器需要低數字電源電壓(1.8 V)和高揚聲器電源電壓(2.5 V至5.5 V)。現在,使用MAX98357和MAX98360等單電源D類放大器可以簡化電路板設計和元件數量。MAX98365可以采用3.0 V至5.5 V單電源供電,或者采用1.8 V至5.5 V電源供電,另一電源采用3.0 V至14.0 V電源供電。數字輸入邏輯電壓與這些器件上的電源電壓無關。輸入邏輯范圍為1.2 V至5.5 V,無需邏輯電平轉換器。

抖動容限和時鐘生成

數字輸入D類音頻放大器通常對時鐘抖動提出了新的挑戰。為了獲得良好的音頻質量,大多數數字輸入放大器在BCLK或MCLK上需要相當低的抖動水平。數據手冊中通常未引用抖動容限;引用抖動容限時,典型規格為~200 ps的均方根抖動。高水平的時鐘抖動通常會降低放大器的動態范圍或滿量程THD + N性能。

在許多系統中,應用處理器的基準振蕩器不是BCLK的方便倍數,因此為放大器提供低抖動時鐘并不容易。例如,13 MHz是GSM電話常用的晶體頻率,27 MHz通常用于視頻解決方案。這些參考頻率都不是 44.1 kSPS 或 48 kSPS 音頻采樣率的方便倍數。因此,這些系統通常會實現復雜的小數N分頻PLL來創建音頻時鐘。在某些情況下,該解決方案需要單獨的音頻參考振蕩器,這會增加復雜性和物料清單 (BOM)。

另一種優選的解決方案是數字輸入放大器,它可以容忍高時鐘抖動而不會降低音頻性能。這種放大器將降低系統復雜性。在最簡單的情況下,可以使用周期跳躍時鐘來生成BCLK,但這會產生非常高的抖動。如果周期跳過 13 MHz 參考時鐘以產生 6.144 MHz BCLK (48 kSPS × 128 OSR),則峰值抖動將為 38.4 ns,均方根抖動將為 22.2 ns(圖 3)。這表示抖動比大多數DAC可以容忍的要高兩個數量級。

然而,這些新的D類音頻放大器在這種時鐘抖動下仍能產生>103 dB的動態范圍性能。可以在應用處理器上使用少量數字門創建周期跳躍時鐘。新器件不需要PLL解決方案中需要的振蕩器或環路濾波器。參見圖 4。

圖3.來自周期跳過的 12 MHz 時鐘的 288.25 MHz MCLK。

圖4.小數N分頻PLL與周期跳躍時鐘實現。

抖動容限測試結果

測試結果表明,MAX98357、MAX98360和MAX98365的動態范圍不會隨著周期跳躍的抖動時鐘而降低。這些器件在抖動時鐘下的性能比120 dB DAC高出20 dB以上。有關Σ-Δ型DAC抖動容限的更多詳細信息,請參閱配套文章。1

圖5.動態范圍下降,11.5 ns rms周期跳躍時鐘抖動。

結論

數字輸入無濾波器D類音頻放大器允許簡單的板級實現,無需I級2C,無MCLK,無電平轉換,無EMI濾波。它們提供高效率、低 EMI 和高輸出功率。MAX98357和MAX98360采用WLP或QFN封裝,可產生3.2 W輸出功率。MAX98365采用WLP封裝,可產生17.6 W輸出功率。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13547瀏覽量

213097 -

驅動器

+關注

關注

52文章

8154瀏覽量

145998 -

濾波器

+關注

關注

160文章

7727瀏覽量

177671

發布評論請先 登錄

相關推薦

如何通過即插即用數字輸入D類放大器實現卓越的音頻性能

如何通過即插即用數字輸入D類放大器實現卓越的音頻性能

評論