介紹

對于需要高動態范圍的應用,通常使用Σ-Δ轉換器。這些應用主要在化學分析、醫療保健和體重管理領域。但是,其中許多模塊無法快速轉換。圖1中的電路描述了一種將高動態范圍與高轉換速率相結合的方法。

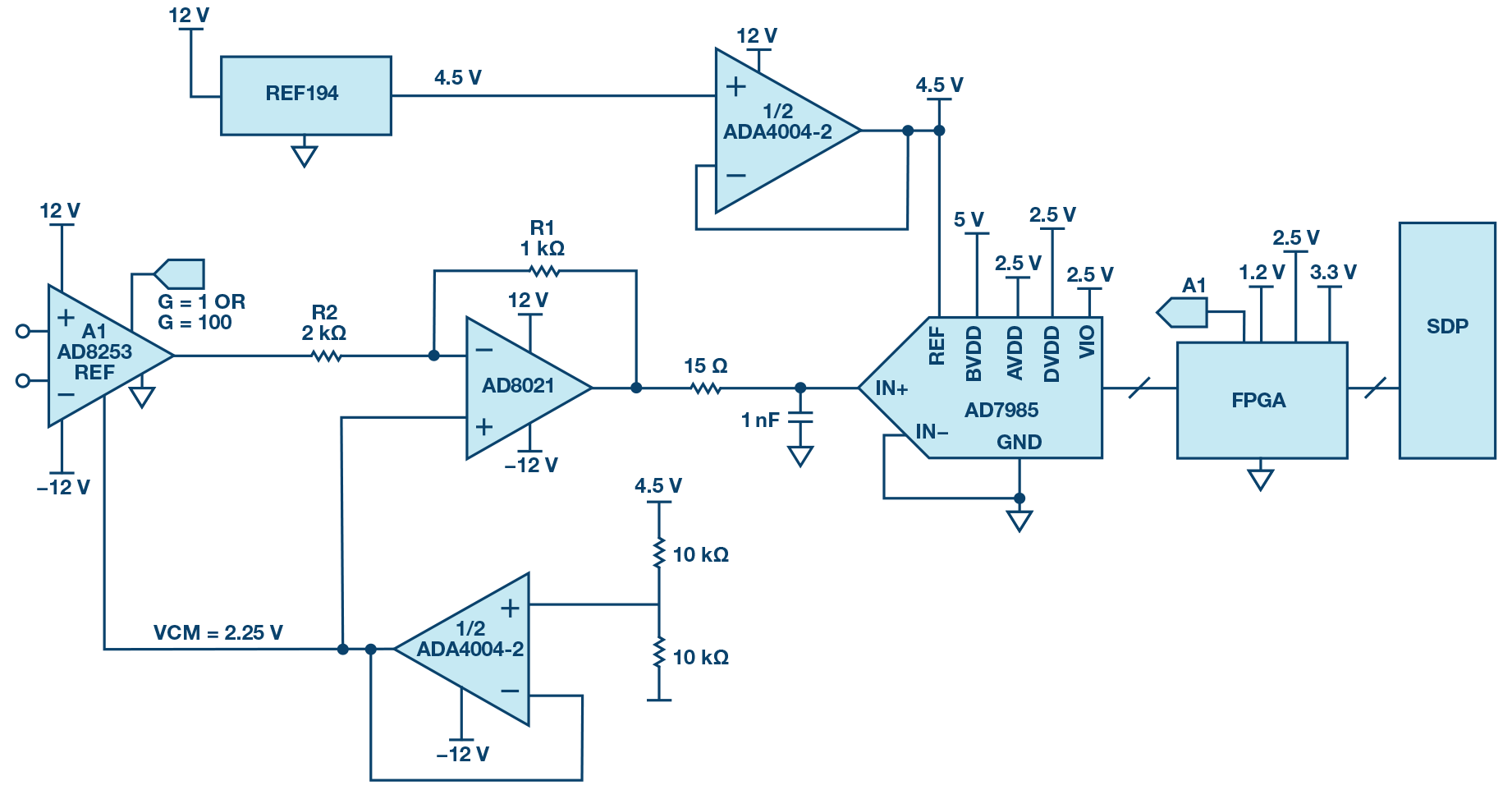

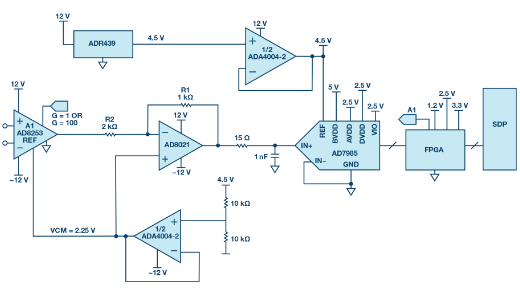

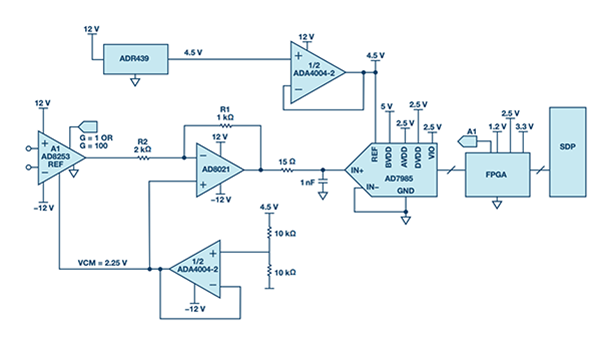

圖1.具有自動增益調節功能的SAR轉換器。

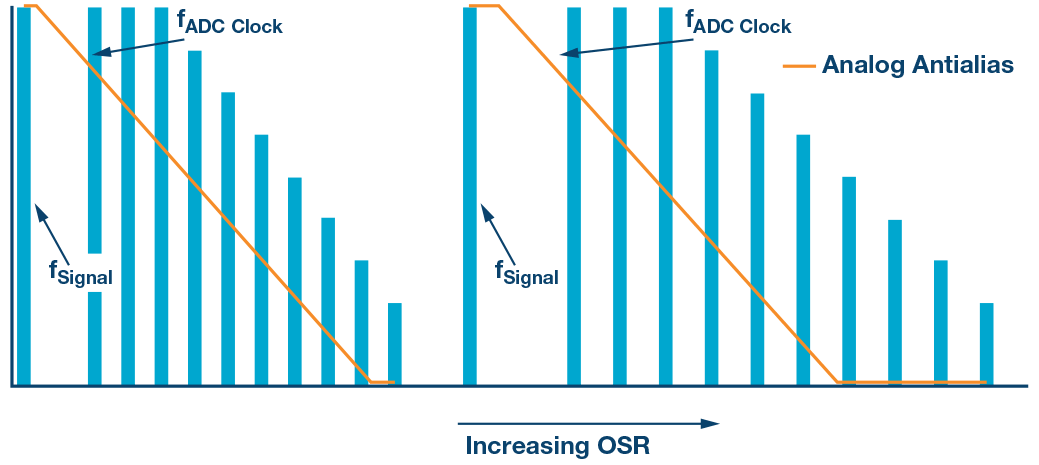

圖1中的電路顯示了一個具有16.2 MSPS的5位SAR轉換器和一個上游可編程儀表放大器,該放大器將增益設置為1或100。通過在FPGA中進行過采樣和數字信號處理,該電路實現了大于125 dB的動態范圍,并且仍然非常安靜。高動態范圍是通過AD8253的自動切換和過采樣實現的,在過采樣中,信號的采樣速率遠高于奈奎斯特頻率。根據經驗,采樣頻率加倍可將原始信號帶寬下的信噪比(SNR)提高約3 dB。在圖1所示電路中,FPGA中仍應用數字濾波,以消除高于目標信號帶寬的噪聲。原理如圖2所示。

為了實現最大動態范圍,在輸入端使用儀表放大器將極低信號放大100倍。關于噪聲的一些注意事項如下:

對于>126 dB的動態范圍要求,在1 V (3 V p-p)的輸入信號下,產生的最大噪聲電平為6 μV rms。AD7985是一款16位SAR轉換器,具有2.5 MSPS。如果以600 kSPS(11 mW的低功率損耗)和72倍的過采樣工作,則采樣速率約為8 kSPS,因此帶寬為4 kHz。在這些條件下,產生的噪聲密度(ND)最大為15.8 nV/√Hz。該值對于選擇正確的儀表放大器非常重要。ADC的SNR通常為89 dB,而72倍的過采樣可提供額外的18 dB,因此仍需要約20 dB才能達到126 dB的目標,這是儀表放大器的任務。AD8253在增益為11時,其值為100 nV/√Hz。以下用作ADC驅動器和電平調整的AD8021又增加了2.1 nV/√Hz的噪聲。

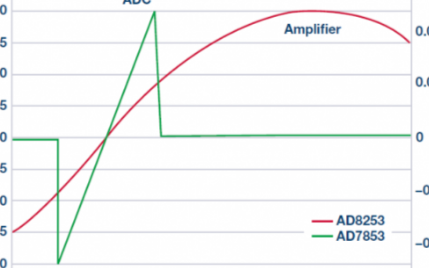

圖2.過采樣的增加消除了部分噪聲。

模擬信號鏈由基準電壓源REF194和ADA4004-2作為基準電壓緩沖器和用于產生失調電壓的驅動器組成。

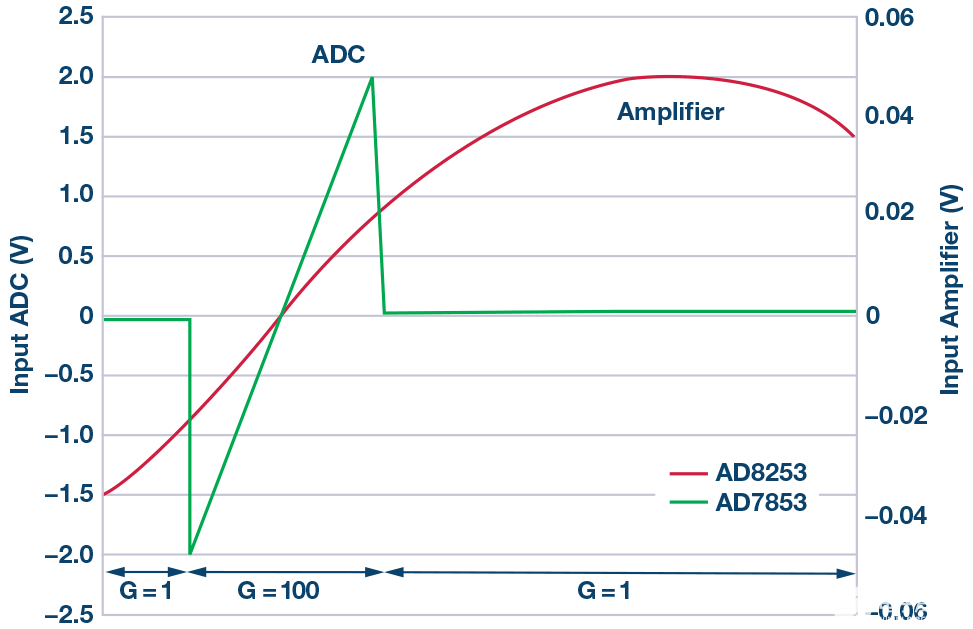

除了模擬路徑中的組件外,FPGA(或處理器)對電路性能也很重要。關鍵任務是將儀表放大器的增益從1切換到100。為此,對多個閾值進行編程,以確保ADC不飽和。因此,AD8253在高達約100 mV的輸入電壓下以20的增益工作,導致ADC輸入端的最大增益為2.0 V。然后,FPGA將AD8253的增益無延遲地降低到1,以防止過驅(見圖3)。

圖3.增益開關示例。

該電路的變化可與其他ADC配合使用,例如AD7980(16位,1 MSPS)、AD7982(18位,1 MSPS)或AD7986(18位,2 MSPS)。 同樣,也可以使用增益為8253、1、10和100的AD1000,而不是增益為8251、1、2和4的儀表放大器,例如增益為8、<>、<>和<>的儀表放大器。基準電壓選擇也可能發生變化。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19160瀏覽量

229120 -

轉換器

+關注

關注

27文章

8625瀏覽量

146867 -

儀表放大器

+關注

關注

17文章

405瀏覽量

71141

發布評論請先 登錄

相關推薦

凌力爾特24 位2Msps SAR ADC實現145dB動態范圍

16位SAR轉換器應用可以在600 kSPS時達到125 dB的動態范圍嗎?

PGA-SAR系統無法達到12比特級別的可重復性時,Δ-Σ系統會怎么樣呢?

如何采用SAR轉換器實現125dB的動態范圍

采用PGA的SAR轉換器可實現125 dB的動態范圍

18 位、2.5Msps、無延遲 SAR ADC可實現 99.8dB SNR 及靈活的模擬輸入范圍

CN0260 采用PGA的過采樣SAR ADC,可實現125 dB以上的動態范圍

24位SAR A/D轉換器具實現145dB動態范圍

帶PGA的SAR轉換器可實現125dB的動態范圍

帶PGA的SAR轉換器可實現125dB的動態范圍

評論