作者:Dr. Jiang Wu and Robert Peloquin

1588年推出的IEEE 2002標(biāo)準(zhǔn)定義了在網(wǎng)絡(luò)上同步分布式時(shí)鐘的協(xié)議。它正在成為許多不同應(yīng)用的首選時(shí)鐘同步方法,包括測(cè)試和測(cè)量、電信和多媒體流。這種標(biāo)準(zhǔn)化的時(shí)鐘同步方法具有成本效益,支持異構(gòu)系統(tǒng),并提供納秒級(jí)同步精度。

本文介紹了原始 IEEE 1588-2002 標(biāo)準(zhǔn)以及作為更新的 IEEE 1588-2008 版本的一部分所包含的增強(qiáng)功能。針對(duì)IEEE 1588的專用硬件支持已集成到ADSP-BF518中1Blackfin嵌入式處理器,因?yàn)镮EEE 1588在其某些目標(biāo)應(yīng)用中的重要性日益增加。本文概述了其功能,然后舉例說明了ADSP-BF518處理器解決方案獲得的時(shí)鐘同步性能結(jié)果。

現(xiàn)在 幾點(diǎn)鐘?

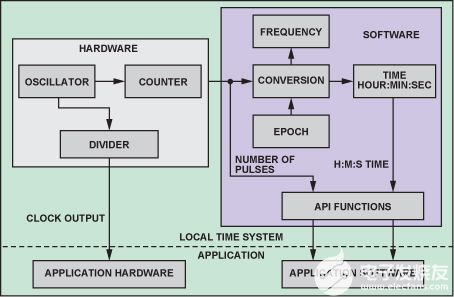

系統(tǒng)通常需要使用本地振蕩器來保持自己的時(shí)間感。圖 1 顯示了硬件和軟件如何結(jié)合以在系統(tǒng)內(nèi)生成時(shí)間信息。

圖1.本地計(jì)時(shí)。

此時(shí)信息可由系統(tǒng)內(nèi)的硬件和軟件資源使用。在硬件中,一個(gè)或多個(gè)物理時(shí)鐘信號(hào)(時(shí)鐘輸出)來自振蕩器的時(shí)鐘,可用于驅(qū)動(dòng)或觸發(fā)系統(tǒng)的其他部分。軟件中維護(hù)的時(shí)間通常稱為系統(tǒng)時(shí)間。系統(tǒng)時(shí)間可以用時(shí)鐘脈沖數(shù)或秒/納秒表示法表示。系統(tǒng)軟件從振蕩器時(shí)鐘脈沖的數(shù)量及其頻率信息中得出時(shí)間,并提供應(yīng)用程序編程接口(API)功能,軟件的其他部分使用該函數(shù)來檢索和設(shè)置時(shí)間。如果需要絕對(duì)時(shí)間,則提供的時(shí)間與預(yù)定義的紀(jì)元相關(guān)聯(lián),該紀(jì)元標(biāo)識(shí)參考時(shí)間點(diǎn)。

同步您的手表

許多應(yīng)用需要兩個(gè)獨(dú)立的器件才能以同步方式運(yùn)行。如果每個(gè)器件僅依靠自己的振蕩器,則各個(gè)振蕩器的特定特性和工作條件之間的差異將限制時(shí)鐘同步運(yùn)行的能力。解決這些限制的一些可能的簡(jiǎn)單解決方案包括:

所有器件都可以使用單個(gè)物理振蕩器。這僅適用于近距離的分布式系統(tǒng);高頻時(shí)鐘信號(hào)無法可靠地長(zhǎng)距離傳輸。

所有器件都可以使用具有幾乎相同特性的振蕩器。這種方法是不切實(shí)際的,因?yàn)楹茈y獲得幾乎相同的振蕩器并防止它們隨著時(shí)間的推移而漂移。更重要的是,每個(gè)振蕩器將受到不同的工作條件的影響。

如果所有設(shè)備都通過以太網(wǎng)等通信網(wǎng)絡(luò)互連,則它們可以通過網(wǎng)絡(luò)交換時(shí)間消息,將其各個(gè)時(shí)鐘動(dòng)態(tài)調(diào)整為單個(gè)“主”時(shí)鐘。使用網(wǎng)絡(luò)時(shí)間協(xié)議(NTP)(傳統(tǒng)的時(shí)間同步協(xié)議),系統(tǒng)中的每個(gè)設(shè)備都會(huì)根據(jù)從NTP時(shí)間服務(wù)器檢索的時(shí)間信息調(diào)整其時(shí)鐘。但是,該協(xié)議只能實(shí)現(xiàn)毫秒量級(jí)的同步精度。

IEEE 1588 定義了能夠?qū)崿F(xiàn)納秒級(jí)同步精度的較新協(xié)議。以下各節(jié)將討論如何實(shí)現(xiàn)此級(jí)別的時(shí)鐘同步。

IEEE 1588 的作用

IEEE 1588 標(biāo)準(zhǔn)定義了用于時(shí)間同步設(shè)備的協(xié)議,這些設(shè)備地理位置分散,但通過某種形式的通信技術(shù)(例如以太網(wǎng))互連。通過在設(shè)備之間交換定時(shí)消息,它們可以保持相同的絕對(duì)系統(tǒng)時(shí)間,以秒和納秒表示。

實(shí)現(xiàn)此目標(biāo)的一種直觀方法是讓具有“最佳”(最準(zhǔn)確)時(shí)鐘并被指定為主時(shí)鐘設(shè)備的一個(gè)設(shè)備將其時(shí)間廣播到其他設(shè)備。其他設(shè)備將調(diào)整其時(shí)間以匹配主時(shí)鐘發(fā)送的時(shí)間。但是,此解決方案有幾個(gè)限制:

主時(shí)鐘設(shè)備不能以無窮小的間隔廣播時(shí)間,因此“從”時(shí)鐘設(shè)備必須使用自己獨(dú)立的“劣質(zhì)”振蕩器來插值來自主時(shí)鐘設(shè)備的兩次廣播之間的時(shí)間點(diǎn)。這會(huì)導(dǎo)致在主時(shí)鐘更新之間的時(shí)間內(nèi)同步降級(jí)。

廣播路徑上不可避免地存在延遲,其幅度取決于通信技術(shù),例如,物理信號(hào)沿著電線從一個(gè)設(shè)備傳輸?shù)搅硪粋€(gè)設(shè)備所需的時(shí)間。此延遲導(dǎo)致主時(shí)鐘和每個(gè)從時(shí)鐘之間產(chǎn)生額外的偏移。

主時(shí)鐘設(shè)備和每個(gè)從時(shí)鐘設(shè)備之間的廣播路徑之間的差異將進(jìn)一步降低各個(gè)從時(shí)鐘設(shè)備之間的同步。

IEEE 1588 指定了一種協(xié)議,該協(xié)議通過測(cè)量路徑延遲來解決第二個(gè)和第三個(gè)問題。它還允許調(diào)整從時(shí)鐘以匹配主時(shí)鐘的節(jié)奏,以緩解第一個(gè)問題。在可能的情況下,可以通過使用更小的廣播間隔和更高質(zhì)量的振蕩器來進(jìn)一步減少第一個(gè)問題。

IEEE 1588 如何測(cè)量通信延遲

IEEE 1588-20022定義四條消息來測(cè)量正向(主站到從站)和后向(從站到主站)路徑的通信延遲:同步、跟蹤、延遲Req和延遲Resp。較新版本 IEEE 1588-2008,3提供了進(jìn)一步的機(jī)制來測(cè)量具有三個(gè)附加消息的對(duì)等延遲:PdelayReq、PdelayResp 和 PdelayRespFollowup。

在這些消息中,Sync、DelayReq、PdelayReq 和 PdelayResp,即所謂的事件消息,在它們離開并到達(dá)設(shè)備時(shí)必須帶有時(shí)間戳(記錄本地時(shí)間)。有兩種方法可以為數(shù)據(jù)包添加時(shí)間戳:

當(dāng)消息由軟件處理時(shí),會(huì)出現(xiàn)軟件時(shí)間戳。時(shí)間戳通常發(fā)生在消息的接收/發(fā)送中斷服務(wù)例程 (ISR) 中,時(shí)間戳是系統(tǒng)時(shí)間的當(dāng)前值。

當(dāng)消息實(shí)際到達(dá)或離開設(shè)備時(shí),將發(fā)生硬件時(shí)間戳。時(shí)間戳操作由硬件執(zhí)行,硬件維護(hù)自己的連續(xù)時(shí)間信息。

在 IEEE 1588 中,這兩種時(shí)間戳方法都是可以接受的,但硬件時(shí)間戳可以提供明顯更好的精度,如下所示。

從主時(shí)鐘設(shè)備到從時(shí)鐘設(shè)備的延遲

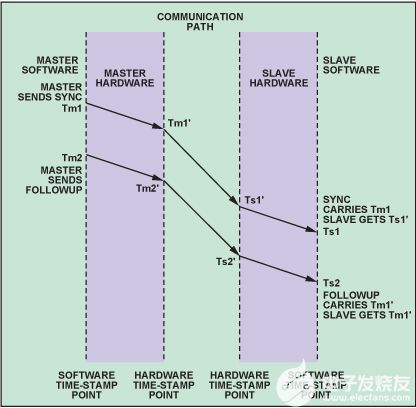

消息同步和跟進(jìn)由主時(shí)鐘設(shè)備發(fā)送;從時(shí)鐘設(shè)備負(fù)責(zé)接收它們并計(jì)算從主時(shí)鐘設(shè)備到從時(shí)鐘設(shè)備的通信路徑延遲。

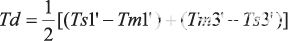

在圖 2 中,在時(shí)間 Tm1 處,主時(shí)鐘設(shè)備軟件讀取當(dāng)前本地系統(tǒng)時(shí)間(Tm1,軟件時(shí)間戳),將其插入同步消息,然后將消息發(fā)送出去。該消息稍后離開主時(shí)鐘設(shè)備,即硬件時(shí)間戳 Tm1'。它以 Ts1'(從時(shí)鐘設(shè)備本地時(shí)間)到達(dá)從時(shí)鐘硬件,并在稍后的時(shí)間 Ts1 由從時(shí)鐘設(shè)備軟件接收。軟件將讀取硬件時(shí)間戳以獲取 Ts1'。如果沒有通信延遲,Ts1' 應(yīng)等于 (Tm1' + Tms),其中 Tms 是主時(shí)鐘和從時(shí)鐘之間的時(shí)間差。該協(xié)議的最終目標(biāo)是補(bǔ)償這種差異。

圖2.測(cè)量主時(shí)鐘和從時(shí)鐘設(shè)備之間的通信延遲。

發(fā)送同步消息后,主時(shí)鐘設(shè)備軟件通過時(shí)間戳單元讀取同步消息的離開時(shí)間 Tm1',將其插入后續(xù)消息,并在 Tm2 發(fā)送該消息。此消息由 Ts2 的從時(shí)鐘設(shè)備軟件接收。此時(shí),從時(shí)鐘設(shè)備軟件有兩個(gè)時(shí)間,Ts1'(同步到達(dá)時(shí)間)和Tm1'(同步出發(fā)時(shí)間)。主從路徑延遲Tmsd由公式1確定。

|

(1) |

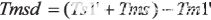

從時(shí)鐘設(shè)備到主時(shí)鐘設(shè)備的延遲

DelayReq 消息由從時(shí)鐘設(shè)備發(fā)送,DelayResp 消息由主時(shí)鐘設(shè)備發(fā)送作為響應(yīng)。通過這些消息,從時(shí)鐘器件可以計(jì)算從時(shí)鐘器件到主時(shí)鐘器件的通信路徑延遲。

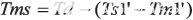

在時(shí)間Ts3(圖3),從時(shí)鐘設(shè)備軟件讀取當(dāng)前本地系統(tǒng)時(shí)間(Ts3),將其插入DelayReq消息,然后將消息發(fā)送出去。發(fā)送消息后,從時(shí)鐘設(shè)備軟件讀取時(shí)間戳以獲取消息的離開時(shí)間Ts3',并等待來自主時(shí)鐘設(shè)備的響應(yīng)。

圖3.測(cè)量從主通信延遲。

DelayReq 消息稍后到達(dá)主時(shí)鐘設(shè)備 Tm3',并由主軟件在 Tm3 進(jìn)行處理。然后,軟件讀取時(shí)間戳以獲取到達(dá)時(shí)間Tm3',將其放入DelayResp消息中,并發(fā)送到Tm4的從時(shí)鐘設(shè)備。當(dāng)從時(shí)鐘器件軟件在Ts4處收到DelayResp消息時(shí),它可以提取時(shí)間Tm3',并通過公式2計(jì)算從機(jī)到主站延遲Tsmd。

|

(2) |

在等式1和等式2中,都有一個(gè)未知變量,即主從時(shí)差Tms。因此,不可能單獨(dú)獲得Tmsd或Tsmd。但是,如果做出通常可接受的假設(shè),即通信路徑是對(duì)稱的

|

(3) |

—IEEE 1588正常工作的關(guān)鍵假設(shè)—然后,將等式1和等式2相加得到

|

(4) |

所有這些計(jì)算都是由從時(shí)鐘設(shè)備執(zhí)行的,因?yàn)檎撬鼈儗で髮⒆约号c主時(shí)鐘設(shè)備同步。它們從主時(shí)鐘設(shè)備的后續(xù)消息中獲取 Tm1',從其 Rx(接收)時(shí)間戳中獲取 Ts1',從其 Tx(傳輸)時(shí)間戳中獲取 Ts3',從主時(shí)鐘設(shè)備的 DelayResp 消息中獲取 Tm3'。

如何計(jì)算從時(shí)鐘和主時(shí)鐘之間的時(shí)間差

一旦獲得通信路徑延遲Td,就可以使用公式1或公式2輕松計(jì)算從主時(shí)間差,如公式5和公式6所示。

|

(5) | ||

|

(6) |

如何調(diào)整從時(shí)鐘設(shè)備的時(shí)間

由于已知與主時(shí)鐘的時(shí)間差,每個(gè)從時(shí)鐘設(shè)備都需要調(diào)整自己的本地時(shí)間以匹配主時(shí)鐘。這項(xiàng)任務(wù)有兩個(gè)方面。首先,從時(shí)鐘設(shè)備需要通過添加時(shí)差來調(diào)整其絕對(duì)時(shí)間,使其時(shí)間與此時(shí)的主時(shí)鐘時(shí)間完美匹配。然后,每個(gè)從時(shí)鐘設(shè)備需要調(diào)整其時(shí)鐘頻率以匹配主時(shí)鐘的頻率。我們不能僅僅依靠絕對(duì)時(shí)間,因?yàn)闀r(shí)間差只適用于某個(gè)時(shí)期,可以是正數(shù),也可以是負(fù)數(shù);結(jié)果,調(diào)整將使從時(shí)鐘時(shí)間跳躍甚至倒退。因此,在實(shí)踐中,調(diào)整需要兩個(gè)步驟。

如果時(shí)差太大,例如大于一秒,則應(yīng)用絕對(duì)時(shí)間調(diào)整。

如果時(shí)間差很小,則對(duì)從時(shí)鐘應(yīng)用頻率的百分比變化。

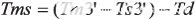

一般來說,系統(tǒng)成為一個(gè)控制回路,其中主時(shí)鐘時(shí)間是參考命令,從時(shí)鐘時(shí)間是跟蹤主時(shí)鐘時(shí)間的輸出,它們的差異驅(qū)動(dòng)可調(diào)時(shí)鐘。許多IEEE 1588實(shí)現(xiàn)常用的PID控制可用于實(shí)現(xiàn)特定的跟蹤性能。圖4顯示了此控制環(huán)路。

圖4.IEEE 1588 控制回路。

點(diǎn)對(duì)點(diǎn)延遲

修訂版IEEE 1588-2008引入了一種測(cè)量路徑延遲的新機(jī)制,稱為點(diǎn)對(duì)點(diǎn)(P2P)延遲。相比之下,前幾節(jié)中討論的主從機(jī)制是端到端 (E2E) 延遲。在支持 IEEE 1588-2008 的網(wǎng)絡(luò)中,主時(shí)鐘設(shè)備可以直接或通過多個(gè)躍點(diǎn)(級(jí))鏈接到從時(shí)鐘設(shè)備。E2E 延遲實(shí)際上是從主時(shí)鐘設(shè)備到從時(shí)鐘設(shè)備的總延遲,包括兩者之間的所有躍點(diǎn)。但是,P2P 延遲僅限于兩個(gè)直接連接的設(shè)備。路徑上的總體延遲是所有躍點(diǎn)的 P2P 延遲之和。從保持路徑對(duì)稱性的角度來看,P2P機(jī)制提供了更好的精度。

如前所述,IEEE 1588-2008 包括三個(gè)附加消息,PdelayReq、PdelayResp 和 PdelayRespFollowup,用于測(cè)量 P2P 延遲。它們的工作方式與上述類似。參考文獻(xiàn) 3 提供了更多詳細(xì)信息。

影響同步性能的因素

精心設(shè)計(jì)的IEEE 1588器件能夠?qū)崿F(xiàn)高精度的時(shí)鐘同步,但重要的是要認(rèn)識(shí)到直接影響性能的關(guān)鍵因素。其中一些包括:

路徑延遲:如前所述,IEEE 1588的路徑延遲測(cè)量假設(shè)通信路徑延遲是對(duì)稱的,即正向路徑的傳輸延遲等于反向傳輸延遲。此外,延遲測(cè)量期間不應(yīng)變化。測(cè)量過程中延遲的變化會(huì)產(chǎn)生不對(duì)稱和延遲抖動(dòng),直接影響同步精度。雖然延遲對(duì)稱性和抖動(dòng)無法在 IEEE 1588 設(shè)備邊界之外進(jìn)行控制,但如果測(cè)量基于硬件時(shí)間戳,則可以在器件內(nèi)改善路徑對(duì)稱性和抖動(dòng)。硬件時(shí)間戳消除了由于中斷延遲、上下文切換和線程調(diào)度而導(dǎo)致的軟件時(shí)間戳導(dǎo)致的顯著抖動(dòng)。

時(shí)鐘的漂移和抖動(dòng)特性:主時(shí)鐘的頻率和相位代表跟蹤控制系統(tǒng)的輸入,從時(shí)鐘是控制對(duì)象。主時(shí)鐘的任何時(shí)變行為都會(huì)對(duì)控制系統(tǒng)造成干擾,并導(dǎo)致穩(wěn)態(tài)和瞬態(tài)誤差。因此,漂移和抖動(dòng)較小的時(shí)鐘將提高同步精度。

控制法:控制方法確定在從時(shí)鐘的調(diào)整中如何糾正從時(shí)鐘設(shè)備時(shí)間的誤差。包括建立時(shí)間、過沖和穩(wěn)態(tài)誤差在內(nèi)的控制律參數(shù)將直接影響時(shí)鐘同步性能。

時(shí)鐘的分辨率:如圖1所示,本地時(shí)間的分辨率由時(shí)鐘的頻率決定;時(shí)間的最小增量是時(shí)鐘信號(hào)的一個(gè)周期。IEEE 1588 協(xié)議的運(yùn)行時(shí)間為 IEEE 1-1588 的分辨率為 2002 ns,2–16適用于 IEEE 1588-2008。時(shí)鐘為 2 是不切實(shí)際的16(!)千兆赫(甚至 1 千兆赫)。本地時(shí)鐘的量化預(yù)計(jì)將影響本地時(shí)間測(cè)量和控制的精度。

發(fā)出同步消息的頻率:從時(shí)鐘的更新頻率最終會(huì)影響同步的精度。較長(zhǎng)的周期通常會(huì)導(dǎo)致在下一次同步時(shí)觀察到較大的時(shí)間誤差,因?yàn)闀r(shí)間誤差是從時(shí)鐘頻率誤差的積分累積。

進(jìn)行延遲測(cè)量的頻率:延遲測(cè)量定期執(zhí)行,間隔基于相鄰樣本之間延遲不會(huì)發(fā)生顯著變化的預(yù)期。如果 IEEE 1588 網(wǎng)絡(luò)遇到較大的延遲變化,則增加延遲測(cè)量頻率將提高時(shí)鐘同步性能。

哪個(gè)是主時(shí)鐘?

在考慮了如何準(zhǔn)確確定主時(shí)鐘設(shè)備和從時(shí)鐘設(shè)備之間的時(shí)間差之后,一個(gè)相關(guān)的問題是如何確定在可能數(shù)百個(gè)互連設(shè)備中哪個(gè)設(shè)備將作為主時(shí)鐘。

IEEE 1588 定義了一種稱為最佳主時(shí)鐘 (BMC) 算法的方法來選擇主時(shí)鐘設(shè)備。對(duì)于這種方法,IEEE 1588 網(wǎng)絡(luò)的每個(gè)設(shè)備都維護(hù)一個(gè)數(shù)據(jù)集,描述其本地時(shí)鐘的性質(zhì)、質(zhì)量、穩(wěn)定性、唯一標(biāo)識(shí)符和偏好。當(dāng)設(shè)備加入IEEE 1588網(wǎng)絡(luò)時(shí),它將廣播自己的時(shí)鐘數(shù)據(jù)集,并從所有其他設(shè)備接收數(shù)據(jù)集。使用所有參與設(shè)備的數(shù)據(jù)集,每個(gè)設(shè)備都運(yùn)行相同的BMC算法來決定主時(shí)鐘及其自己的未來狀態(tài)(主時(shí)鐘或從時(shí)鐘)。由于相同的算法由同一數(shù)據(jù)上的所有設(shè)備獨(dú)立執(zhí)行,因此所有設(shè)備都會(huì)得出相同的結(jié)論,而無需它們之間進(jìn)行任何協(xié)商。有關(guān) BMC 算法詳細(xì)信息的詳細(xì)信息,請(qǐng)參閱參考文獻(xiàn) 2 和 3。

ADSP-BF518處理器對(duì)IEEE 1588的支持

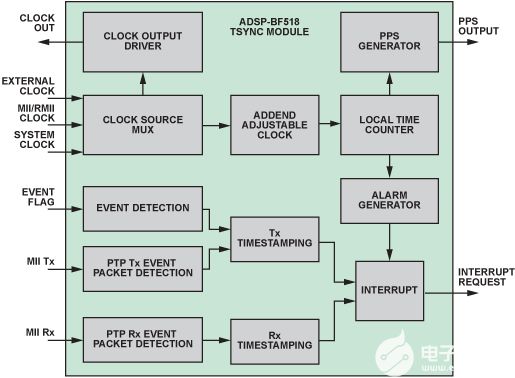

ADI公司的ADSP-BF518處理器最近加入了ADI公司的Blackfin DSP系列。與其前身ADSP-BF537一樣,4它具有內(nèi)置的以太網(wǎng)媒體訪問控制器(EMAC)模塊。它支持IEEE 1588標(biāo)準(zhǔn)中的EMAC功能的能力通過附加的TSYNC模塊以及支持以太網(wǎng)上各種IEEE 1588應(yīng)用的額外功能進(jìn)行了擴(kuò)展。圖 5 顯示了 TSYNC 模塊的框圖。ADSP-BF51x Blackfin處理器硬件參考提供了更多信息。5

圖5.ADSP-BF518處理器TSYNC模塊框圖。

數(shù)據(jù)包檢測(cè)

ADSP-BF518處理器可以檢測(cè)所有IEEE 1588事件消息(包括傳入和傳出數(shù)據(jù)包)并提供硬件時(shí)間戳。IEEE 1588 系統(tǒng)的精度在很大程度上取決于事件消息時(shí)間戳的準(zhǔn)確性及其采用的位置,因?yàn)檫@些會(huì)影響對(duì)路徑延遲的對(duì)稱性和恒定性的要求。ADSP-BF518的TSYNC模塊持續(xù)監(jiān)控MAC控制器與以太網(wǎng)物理接口收發(fā)器(PHY)之間的硬件接口,即媒體無關(guān)接口(MII),并在檢測(cè)到事件消息時(shí)生成硬件時(shí)間戳,該功能可提高ADSP-BF518的同步精度。

事件消息的檢測(cè),設(shè)計(jì)為可編程的,基本上可以配置為支持 IEEE 1588-2002(默認(rèn))或 IEEE 1588-2008。此外,這種可編程性允許支持未來版本的IEEE 1588以及其他需要時(shí)間戳的通用協(xié)議,包括配置為對(duì)進(jìn)出處理器的每個(gè)以太網(wǎng)數(shù)據(jù)包進(jìn)行時(shí)間戳。

靈活的時(shí)鐘源

本地時(shí)鐘的屬性對(duì)于 IEEE 1588 系統(tǒng)的性能非常重要。為了滿足各種應(yīng)用的要求,ADSP-BF518處理器為本地時(shí)鐘源提供了三種選擇:系統(tǒng)時(shí)鐘、外部時(shí)鐘或以太網(wǎng)時(shí)鐘。如果應(yīng)用程序有特定的時(shí)鐘要求,它可以選擇外部時(shí)鐘并提供自定義時(shí)鐘源。如果主時(shí)鐘設(shè)備和從時(shí)鐘設(shè)備背靠背連接,以太網(wǎng)時(shí)鐘選項(xiàng)可以提供良好的精度,因?yàn)闀r(shí)鐘是從以太網(wǎng)線路推斷的,并且兩個(gè)設(shè)備在同一時(shí)鐘上運(yùn)行。一般應(yīng)用程序可以將處理器的系統(tǒng)時(shí)鐘作為其時(shí)鐘源。

選定的源時(shí)鐘也由 TSYNC 模塊驅(qū)動(dòng),作為處理器的輸出,通過特定的引腳 Clockout,供系統(tǒng)的其他部分用于本地時(shí)間信息。

繳費(fèi)靈輸出

每秒脈沖數(shù) (PPS) 信號(hào)是時(shí)間信息的物理表示。它標(biāo)稱是一個(gè) 1 Hz 信號(hào),每一秒轉(zhuǎn)換一個(gè)脈沖。它可用于控制本地設(shè)備或在網(wǎng)絡(luò)故障時(shí)提供輔助時(shí)間通道。它也可以用于測(cè)試。兩個(gè)器件的PPS信號(hào)之間的相位差是其時(shí)間偏移的物理測(cè)量值。

ADSP-BF518處理器提供靈活的PPS輸出。它使用可編程的開始時(shí)間 (PPS_ST) 和周期 (PPS_P) 來生成脈沖在 (PPS_ST + n × PPS_P 發(fā)生頻率的信號(hào),其中 n = 1, 2, 3...在基本用法中,只需將PPS_P設(shè)置為 1 秒即可創(chuàng)建 PPS 信號(hào),并將PPS_ST到任何未來的時(shí)刻作為秒的倍數(shù)。這種PPS輸出能力允許將其用作生成具有完全可編程頻率和啟動(dòng)時(shí)間的周期信號(hào)的參考。

輔助快照

某些應(yīng)用程序可能需要為標(biāo)志信號(hào)切換指示的特定事件添加時(shí)間戳。ADSP-BF518的TSYNC模塊通過提供輔助快照功能(使用專用引腳接受外部標(biāo)志)來促進(jìn)這一請(qǐng)求。切換標(biāo)志將觸發(fā)模塊在時(shí)間戳寄存器中捕獲當(dāng)前本地時(shí)間,以供軟件訪問。

報(bào)警

如果應(yīng)用程序需要在特定時(shí)間執(zhí)行任務(wù),則可以利用TSYNC模塊的告警功能。此功能允許設(shè)置絕對(duì)本地時(shí)間,以便在時(shí)間到來時(shí)觸發(fā)處理器中斷。然后,軟件可以為中斷提供服務(wù)并運(yùn)行任務(wù)。

可調(diào)時(shí)鐘

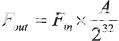

TSYNC 模塊的可調(diào)時(shí)鐘是基于加法的時(shí)鐘。如圖6所示,它采用固定的輸入時(shí)鐘信號(hào)并輸出輸入的“脈沖竊取”版本:在每個(gè)輸入時(shí)鐘處將加法值添加到累加器中,每次累加器溢出時(shí),進(jìn)位驅(qū)動(dòng)本地時(shí)間計(jì)數(shù)器,該計(jì)數(shù)器根據(jù)計(jì)數(shù)的脈沖數(shù)給出本地時(shí)間。本地時(shí)鐘的頻率可以通過更改加法來調(diào)整,因?yàn)榧臃Q定了累加器溢出的頻率,因此本地時(shí)間計(jì)數(shù)器增加的頻率。如果輸入時(shí)鐘的頻率為F在,并且加法的值為 A,則本地時(shí)鐘頻率為

|

(7) |

圖6.基于附加的可調(diào)時(shí)鐘。

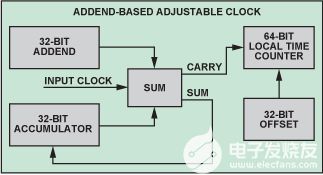

在ADSP-BF1588處理器上實(shí)現(xiàn)IEEE 518

完整的IEEE 1588-2008兼容系統(tǒng)基于ADSP-BF518處理器構(gòu)建,如圖7所示。

圖7.IEEE 1588在ADSP-BF518上的實(shí)現(xiàn)。

處理器的 TSYNC 模塊檢測(cè)傳入和傳出的 IEEE 1588 消息,并使用硬件為事件消息添加時(shí)間戳。由IXXAT(IXXAT Automation GmbH)提供的IEEE 1588堆棧軟件實(shí)現(xiàn)了標(biāo)準(zhǔn)要求的消息交換協(xié)議。它使用 TSYNC 驅(qū)動(dòng)程序來讀取、寫入和調(diào)整 TSYNC 時(shí)鐘,并使用 MAC 控制器驅(qū)動(dòng)程序在以太網(wǎng) MAC 層(開放系統(tǒng)互連模型的第 2 層)上發(fā)送和接收消息。它還實(shí)現(xiàn)了P2P延遲測(cè)量的控制律和濾波。以太網(wǎng) PHY 是美國國家半導(dǎo)體公司 DP83848,6 因其低抖動(dòng)延遲特性而被選中。為簡(jiǎn)單起見,選擇處理器的系統(tǒng)時(shí)鐘 (80 MHz) 作為 TSYNC 模塊時(shí)鐘源。

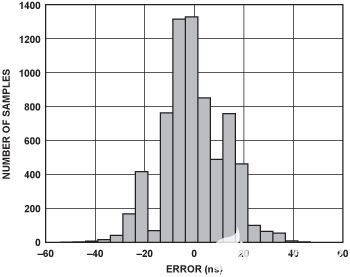

圖8.ADSP-BF1588上IEEE 518系統(tǒng)的從時(shí)鐘誤差直方圖。

圖8顯示了該器件的時(shí)鐘同步性能,作為兩個(gè)相同的ADSP-BF518 IEEE 1588系統(tǒng)之間測(cè)量誤差的直方圖。在大約 6938 秒的時(shí)間內(nèi)進(jìn)行了 1700 次測(cè)量。得到的平均誤差為0.015 ns,標(biāo)準(zhǔn)差為12.96 ns。此測(cè)試使用了 0.25 秒的同步消息間隔。

結(jié)論

IEEE 1588 標(biāo)準(zhǔn)為同步分布式時(shí)鐘提供了一種高精度、低成本的方法。雖然 IEEE 1588 沒有明確要求硬件支持,但硬件輔助消息檢測(cè)和時(shí)間戳對(duì)于實(shí)現(xiàn)最高級(jí)別的同步精度至關(guān)重要。ADSP-BF518處理器為IEEE 1588-2002和IEEE 1588-2008提供硬件支持,包括可支持各種應(yīng)用的特性。通過使用ADSP-BF1588處理器和IXXAT IEEE 518-1588協(xié)議軟件實(shí)現(xiàn)IEEE 2008技術(shù),已經(jīng)證明了高精度時(shí)鐘同步。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19174瀏覽量

229191 -

嵌入式

+關(guān)注

關(guān)注

5070文章

19024瀏覽量

303478 -

振蕩器

+關(guān)注

關(guān)注

28文章

3813瀏覽量

138911

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Blackfin嵌入式處理器介紹

嵌入式處理器和數(shù)字信號(hào)處理器(DSP)選型指南

基于Blackfin處理器的嵌入式數(shù)碼相框設(shè)計(jì)

ADI推出不到2美元的Blackfin嵌入式處理器ADSP-BF592

IEEE1588時(shí)鐘同步在PTN網(wǎng)中的實(shí)現(xiàn)

IEEE1588同步原理及其在PTN網(wǎng)中的實(shí)現(xiàn)

嵌入式設(shè)計(jì)經(jīng)驗(yàn):ARM-WinCE平臺(tái)時(shí)鐘同步設(shè)計(jì)

利用匯聚式處理器Blackfin和uClinux系統(tǒng)實(shí)現(xiàn)嵌入式數(shù)碼相框的設(shè)計(jì)

ADSP-BF538/ADSP-BF538F:Blackfin嵌入式處理器數(shù)據(jù)手冊(cè)

ADSP-BF539/ADSP-BF539F:Blackfin嵌入式處理器數(shù)據(jù)手冊(cè)

ADSP-BF561:Blackfin嵌入式對(duì)稱多處理器數(shù)據(jù)手冊(cè)

IEEE1588時(shí)鐘同步在PTN網(wǎng)中的實(shí)現(xiàn)

使用IEEE 1588和Blackfin嵌入式處理器同步設(shè)備時(shí)鐘

使用IEEE 1588和Blackfin嵌入式處理器同步設(shè)備時(shí)鐘

評(píng)論