內置自檢(BIST)曾經是為復雜的數字芯片保留的,現在可以在許多數字內容相對較少的設備中找到。向更精細的直線工藝幾何形狀的轉變使ADI公司的多個數據轉換器能夠包含BIST功能。對于芯片制造商來說,BIST可以通過提供對器件的更大可見性來幫助簡化器件表征過程,并通過允許對芯片的某些子集進行自主測試來縮短制造測試時間。當片上BIST功能被整合到系統級設計中時,BIST在系統級實現了更大的優勢。隨著系統變得越來越復雜,將單個組件與BIST集成,可以實現分層測試策略,從而為增強系統可靠性提供強大的功能。

在系統層面,BIST功能可用于設計階段,以表征數字處理器和數據轉換器之間的數字接口時序。如果沒有BIST,數字接口中的位錯誤必須通過轉換器本底噪聲的變化來檢測。這種類型的錯誤檢測遠不如基于數字的BIST簽名檢查敏感,后者可以檢測單個比特錯誤。同樣的數字接口檢查可以在生產測試車間執行,也可以在現場的系統級自檢中執行。

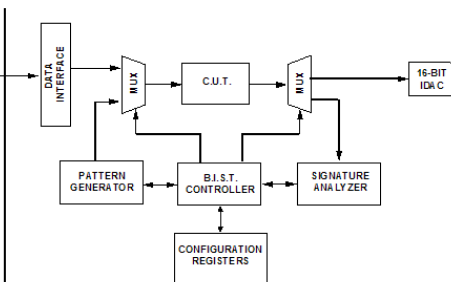

圖1 – BIST電路的功能框圖

圖 1 顯示了一個基本的 BIST 實現。將BIST集成到設備中需要添加三個功能塊:模式生成器,簽名(或響應)分析器和測試控制器。碼型發生器激勵被測電路(CUT)。特征碼分析器收集 CUT 對測試模式的響應,并將其壓縮為單個值,稱為特征碼。測試控制器協調測試電路的動作,并提供一個簡單的外部接口。

模式生成器和特征分析器通常使用線性反饋移位寄存器(LFSR)實現。帶有n個觸發器的LFSR如圖2所示。這種類型的模式生成器可以產生寬度為 n 的偽隨機模式,具有 2n重復前有 -1 個唯一組合(除所有零之外的所有可能組合)。當初始條件已知時,該模式是完全確定的。

圖2 – BIST功能所需的基本組件

特征分析也利用LFSR。 利用第二個類似構造的LFSR可以將CUT對整個模式的響應壓縮為單個值。該值在測試完成后存儲在寄存器中。然后可以將簽名與預期的簽名進行比較,以驗證設備的正確操作。壓縮響應的過程引入了使錯誤的CUT產生正確特征的可能性,但是隨著模式長度的增加,未檢測到故障的可能性變得非常小。

在系統級別使用 BIST

在板級,BIST功能可以幫助進行多種類型的測試。例如,測試DAC和數字數據源之間的接口可以通過調用BIST特征分析電路并使用數字源提供測試模式來完成。在這種情況下,DAC制造商將提供測試模式和預期的簽名。該設備已經過制造商的測試,因此不正確的簽名可能歸因于數字接口故障。或者,DAC制造商可以提供一種算法,用于為任意測試模式生成預期的簽名。這為源可以提供的模式提供了更大的靈活性。ADI公司提供AD9736高速DAC的BIST模型、測試模式和預期特征。

簽名測試是通過/失敗類型的測試。不正確簽名的特定值無助于診斷故障。但是,設備被激勵的方式可以提供有關故障類型的一些信息。例如,不同的測試模式可以將故障隔離到特定的輸入引腳。在表征數字接口時,這種類型的測試可用于確定是否存在任何導致降低整個總線時序裕量的外圍連接。此信息可用于在后續修訂中改進電路板布局。

在某些情況下,可以使用BIST碼型發生器代替外部數字碼型發生器,從而簡化器件和下游信號鏈其余部分的評估。AD9789內置片內QAM映射器、插值濾波器、數字上變頻器,后接14位DAC。可以將 BIST 模式生成器配置為將數據發送到 QAM 映射器。設備將此數據作為調制信號傳輸。模擬性能可以在DAC的輸出端和發射路徑信號鏈的其余部分測量,而無需任何額外的數字激勵。這可以加快設計模擬部分的評估,因為它將模擬評估與數字開發分離,并消除了數字測試模式生成所需的特殊電路。

預計在數據轉換器和其他“模擬”器件上集成BIST電路將變得越來越普遍,并且功能更強大,因為這些器件轉向更小的工藝幾何形狀。隨著 系統 的 復雜 化, 包含 測試 能力 變得 重要。隨著數字接口速度的提高,驗證這些接口是否可靠變得更加重要和困難。尋找在單個設備上使用 BIST 功能的方法,以提高系統級可測試性和設備評估。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8627瀏覽量

146869 -

濾波器

+關注

關注

160文章

7728瀏覽量

177684 -

變頻器

+關注

關注

251文章

6504瀏覽量

144256

發布評論請先 登錄

相關推薦

虛擬設備,模擬實體設備和云端通信

數字BIST的基本原則

適用于低頻測量應用的AD7195

USB標準適用于哪些應用

鈕扣電池都有哪些類型分別適用于哪些設備?

7000應用開發技巧:模擬設備驅動(Mocking)

模擬設備高速轉換器

常見的PLC模擬量IO有哪些?

適用于模擬輸出模塊的雙極Fly-Buck-Boost解決方案

適用于TI超聲AFE的模擬時間增益控制(ATGC)解決方案

適用于模擬設備的BIST

適用于模擬設備的BIST

評論