作者:Thomas Cameron and Peadar Forbes

想象一下,一種設備可以在您家中提供高質量的手機接收,讓您和您的家人以較低的月費無限制地使用語音和數據。毫微基站(通常稱為家庭基站)提供所有這些以及更多功能。這種小型無線設備可改善家庭或辦公室的本地無線覆蓋范圍,有望極大地改變無線基礎設施的格局。

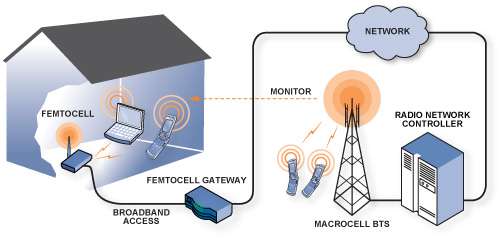

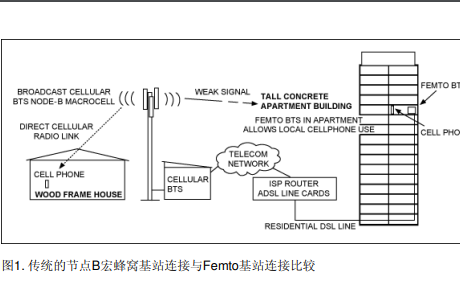

圖1說明了家庭基站的概念。傳統基站提供廣域覆蓋,而家庭基站則在住宅等小區域內提供無線覆蓋。家庭基站通過用戶的寬帶互聯網連接將移動流量路由到網絡,從而減輕無線網絡的流量。家庭基站提高了網絡的容量,同時降低了運營商的回程、電力和維護成本。它還使運營商能夠在信號覆蓋范圍有限的家庭中競爭服務。為了換取補貼的家庭基站,運營商會在客戶的每月蜂窩計劃中增加額外費用。在家庭基站區域時,所有移動使用都將包含在家庭計費計劃中,允許在家中無限制地使用語音和數據,而不會產生大筆月度賬單。家庭基站的接近可實現高質量的鏈路,同時減少手機電池的使用。家庭基站克服了來自基站的3G信號穿透墻壁的限制,實現了對移動數據服務的高速訪問,例如瀏覽互聯網,下載音樂和手機上的流媒體視頻。

家庭基站類似于Wi-Fi路由器,基于經過驗證的無線基礎設施標準(UMTS,CDMA)。它與新興標準兼容,使用運營商擁有的頻譜提供高效、強大的無線鏈路。與現有手機的兼容性使連接對用戶透明。與將數十個或數百個基站聚合到核心網絡上的宏蜂窩網絡不同,家庭基站網關必須管理數千甚至數百萬個家庭基站節點。

家庭基站必須以與手機相似的成本提供基站預期的服務質量(QoS),這給無線電設計人員帶來了獨特的挑戰。家庭基站必須以宏節點的一小部分成本提供高質量的語音服務和高速移動數據服務(EVDO和HSPA)。為了應對這些挑戰,家庭基站設計必須利用低成本制造技術和高度集成的電路,以最大限度地減少校準和測試時間。家庭基站駐留在家中,因此它們必須體積小、成本低且用戶安裝。以 100 mW 量級的低功耗傳輸時,家庭基站必須了解無線環境,以減輕干擾并滿足監管要求。3G家庭基站必須監控UMTS信道以檢測附近的基站,以及GSM信道,以建立當用戶離開家庭基站區域時可能適合切換的小區。

家庭基站可以看作是兩個不同的功能:模擬前端和基帶處理器。前端是本文的主題,它將數字數據流轉換為發射電路中的RF信號,反之亦然。前端設計需要在集成和性能之間進行權衡。雖然可以定制分立式解決方案以提供最佳性能,但對于家庭基站設計而言,成本過高。相反,完全集成的解決方案可以提供最低的成本,但性能可能還不夠。

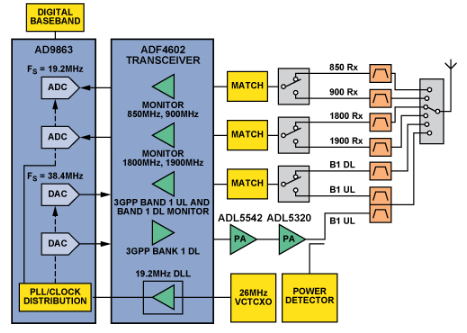

圖2顯示了家庭基站的高級框圖,該框圖旨在支持UMTS頻段1中的本地基站操作以及監視850 MHz、900 MHz、1800 MHz、1900 MHz和2100 MHz頻段的信號。AD98631混合信號前端(MxFE)基帶收發器ADF4602?2集成無線電收發器,ADL55423和ADL53204線性放大器、開關、濾波器和其他相關支持電路構成了家庭基站的緊湊、高性能前端。下面詳細介紹了突出顯示的塊。

在發射端,數字基帶向AD12饋送9863位并行數據流,AD4602將其轉換為模擬I/Q基帶信號。基帶信號由ADF5542轉換為RF,由ADL5320和ADL6增益級放大,然后發送到雙工器。功率檢波器監視RF輸出。單刀六擲 (SP13T) 開關選擇將哪個發射或接收監控鏈連接到單個天線。該信號鏈在RF輸出連接器上提供3 dBm輸出功率,同時滿足25GPP標準TS104.<>中定義的發射ACLR規范。

接收鏈包括表面聲波 (SAW) 濾波器和用于監控主路徑的單刀雙擲開關。匹配模塊由一個簡單的串聯/并聯電感組成,用于每個接收端口。ADF4602具有三個接收器輸入引腳:一個用于頻段1,一個用于高頻段和低頻段監控功能。頻段 1 接收功能可在 1960 MHz 和 2140 MHz 之間切換以接收上行鏈路信號,以監控下行鏈路頻率。ADF4602將所選RF信號下變頻并濾波為基帶I/Q信號。基帶信號由AD9863中的雙通道ADC采樣,并轉換為數字基帶的雙通道12位并行位流。

該功能分區為設計人員提供了靈活性,確保了信號鏈的高性能,并允許選擇數據轉換器的速度和分辨率以滿足應用的要求。ADI解決方案使設計人員能夠將模擬前端與商用基帶功能相結合,加快家庭基站設計的上市時間,同時隨著家庭基站市場的成熟,保持ADI技術未來集成的優勢。

ADF4602 集成無線電收發器

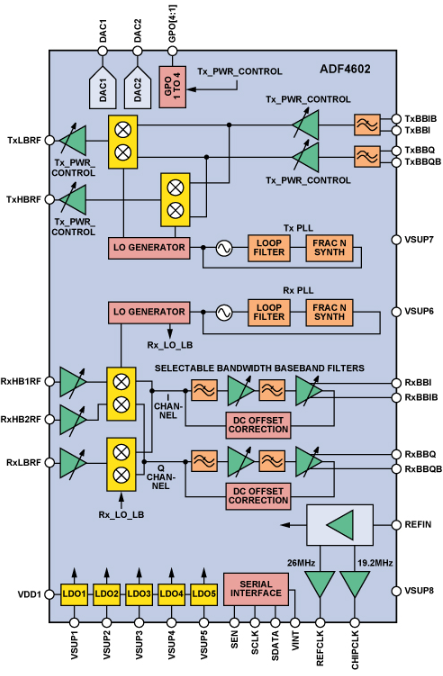

ADF4602(如圖3所示)是一款3G收發器,具有無與倫比的集成度和非常適合高性能3G家庭基站的特性集。該接收器基于直接變頻架構,是高度集成的寬帶CDMA (W-CDMA)接收器的理想選擇,通過完全集成所有級間濾波器來減少物料清單(BOM)。接收基帶濾波器提供可選帶寬,支持接收W-CDMA和GSM-EDGE無線電信號。可選帶寬與多頻段LNA輸入結構相結合,允許GSM/EDGE信號作為UMTS家庭基站的一部分進行監控。

ADF4602內置兩個完全集成的可編程頻率合成器,用于生成發射和接收本振(LO)信號。該設計采用小數 N 分頻架構,可實現低噪聲和快速鎖定時間。所有必要的組件,包括環路濾波器、VCO和諧振電路組件,都完全集成在發射和接收頻率合成器中。VCO 以兩倍的高頻段頻率和四倍的低頻段頻率運行,從而最大限度地降低了 VCO 在所需頻率下的泄漏功率和 VCO 的調諧范圍要求。VCO采用多頻段結構,覆蓋寬工作頻率范圍。該設計結合了頻率和幅度校準,以確保振蕩器始終以最佳性能運行。完全獨立的校準在200 μs PLL鎖定時間內進行,無需用戶輸入。片內VCO輸出被饋送到調諧緩沖級,然后饋送到正交發生電路。調諧緩沖器確保在VCO傳輸中產生最小的電流和LO相關噪聲。正交發生器產生驅動調制器和解調器所需的高精度相位信號。已采取特殊預防措施,在發射鏈和接收鏈之間提供頻分雙工(FDD)系統所需的隔離。

圖3.ADF4602原理框圖

接收器前端包括三個高性能、單端、低噪聲放大器(LNA),使該器件能夠支持三頻段應用。兩個適合 1800 MHz 至 2170 MHz 的高頻段工作,而一個適合 824 MHz 至 960 MHz 的工作。 級間RF濾波完全集成,確保外部帶外阻塞信號在混頻器級之前得到適當的衰減。單端 50 Ω輸入結構簡化了接口,并減少了小尺寸單端雙工器所需的匹配組件。出色的器件線性度可確保各種SAW和陶瓷濾波器雙工器的良好性能。

高線性度解調器電路用于將RF信號轉換為基帶同相和正交分量。包括兩個解調器部分:一個針對高頻段LNA輸出優化,另一個針對低頻段優化。高頻段和低頻段輸出組合在一起,直接驅動到基帶低通濾波器的第一級,從而減少基帶放大之前的最大阻塞信號。接收器頻率合成器部分從VCO分配系統向混頻器提供正交LO驅動。可編程分頻器允許在高頻段和低頻段使用相同的VCO。通過精心設計和布局解調器和VCO分配電路,實現了出色的90°正交相位和幅度匹配。

基帶部分包括分布式增益和濾波,旨在提供最大54 dB增益和60 dB增益控制范圍。通過精心設計,通帶紋波、群延遲、信號損耗和功耗保持在最低水平。過濾器校準在制造過程中進行,從而實現高度的準確性和易用性。兩個可選 7千-提供階次基帶濾波器:一個具有 W-CDMA 的 1.92 MHz 截止頻率,另一個具有 100 kHz 的 GSM 截止頻率。

在W-CDMA模式下,ADF4602能夠提供102 dB增益,90 dB增益控制范圍分布在整個接收信號鏈中。RF前端包含30 dB的控制范圍:LNA為18 dB,混頻器跨導級為12 dB。兩個基帶有源濾波器級均提供18 dB增益控制范圍,步長為6 dB。這導致總增益控制范圍為36 dB,步長為三個12 dB。可變增益放大器 (VGA) 以 24dB 步長實現 1dB 增益控制范圍。為了簡化編程并確保最佳的接收機性能和動態范圍,只需對所需的總接收增益進行編程;ADF4602解碼增益設置,并在各個模塊之間自動分配增益。

該發射器采用創新的直接變頻調制器,可實現高線性度和低噪聲,同時無需外部發射SAW濾波器。用于I和Q通道的差分直流耦合基帶接口支持1.05 V至1.4 V的寬輸入共模電壓(VCM)。允許的最大信號擺幅為550 mV峰值,對應于I或Q通道上1.1 V p-p的差分范圍。在正交調制器之前,基帶輸入的信號通過 2德·-訂購截止頻率為 4 MHz 的巴特沃茲濾波器,以抑制帶外雜散。校準技術可在頻率和環境條件下保持準確的 I/Q 平衡和相位,確保在所有條件下都能以良好的裕量滿足 3GPP 載波泄漏、EVM 和 ACLR 要求。ADF4602在163 MHz失調和–190 dBm輸出功率下可實現–8 dBm/Hz寬帶本底噪聲,同時滿足TS25.104對EVM和ACLR的要求。輸出匹配至50 Ω,以便與功率放大器進行簡單連接。

AD9863 混合信號前端基帶收發器

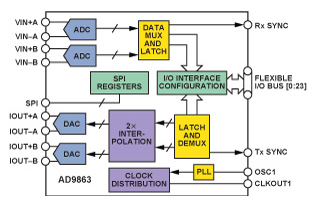

AD9863是面向通信市場的MxFE集成轉換器系列成員,非常適合低成本、高性能家庭基站應用。它集成了雙通道 12 位模數轉換器和雙通道 12 位 TxDAC 數模轉換器。ADC針對50 MSPS或更低的采樣進行了優化。DAC的工作速度高達200 MHz,包括一個可旁路的2×或4×插值濾波器。AD64采用9863引腳LFCSP封裝,尺寸僅為9 mm×9 mm ×0.9 mm。此處重點介紹AD9863,但MxFE系列的其他成員(AD9860、AD9861和AD9862)為設計人員提供了選擇控制電路性能和輔助轉換器的靈活性。 ?

圖4.AD9863 MxFE框圖

靈活的雙向 24 位 I/O 總線可容納各種商用基帶 ASIC 或 DSP。在半雙工系統中,接口支持 24 位并行傳輸或 12 位交錯傳輸。在全雙工系統中,該接口支持12位交錯ADC總線和12位交錯DAC總線。靈活的 I/O 總線減少了引腳數量和封裝尺寸。對于頻分雙工(FDD)W-CDMA,AD9863可同時工作發射和接收通道。這需要使用全雙工模式 — 一條 12 位交錯 Rx 數據總線和一條 12 位交錯發射數據總線。

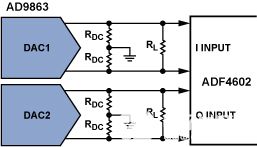

DAC內核將12位數據轉換為兩個互補差分電流輸出,使用電阻網絡將其提供給ADF4602,如圖5所示。對于 120.1V 共模電壓,RDC 設置為 2 Ω,RL設置為 63 Ω,以實現 1V p-p 差分輸入擺幅。

圖5.AD9863和ADF4602之間的簡單接口。

DAC包含可編程的精細增益和直流失調控制,可用于補償I和Q通道之間的失配,以抑制LO饋通并提高EVM性能。10位直流失調控制可獨立使用,為任一差分引腳提供高達±12%的失調,從而允許校準任何系統失調。

ADC輸入由一個2 kΩ差分輸入電阻和一個開關電容電路組成。輸入可以自偏置至中間電源,也可以編程為接受外部直流偏置。因此,建議將ADF4602接收基帶輸出直接連接到AD9863 ADC輸入。ADC輸入滿量程電平為2 V p-p差分。

家庭基站時鐘解決方案

家庭基站需要一個非常精確的參考時鐘(±0.1 ppm),以滿足3GPP規范。實現這種非常精細的時鐘控制的方法不在本文的討論范圍之內,但存在許多可能性,包括通過監控接收器的GSM宏蜂窩同步、GPS同步和IEEE 1588精密定時協議。在某些情況下,家庭基站供應商可以實現上述方法的組合。最終,參考時序控制電路將調節參考頻率源。在ADI評估板上,這款26 MHz VCTCXO用作ADF4602的基準電壓源。延遲鎖相環 (DLL) 產生 19.2 MHz,是 3.84 MHz W-CDMA 芯片時鐘的倍數。該19.2 MHz時鐘用作AD9863的時鐘輸入。

AD9863具有多種變量的通用時鐘配置。ADC時鐘速率、DAC時鐘速率、PLL和插值器設置可通過軟件控制,從而優化功耗與性能以滿足要求。在推薦配置中,PLL乘法器設置為2×,PLL輸出頻率為38.4 MHz。ADC的時鐘頻率為該頻率的一半。在發射端,38.4MHz PLL輸出用于為DAC提供時鐘。發射插值設置為2×以抑制DAC鏡像。時鐘頻率的其他組合也是可能的。AD9863數據手冊提供了工作模式的完整說明。使用上述時鐘方案,家庭基站不需要任何離散頻率轉換PLL,這在宏蜂窩基站中很常見。集成了所有頻率轉換,幫助家庭基站滿足市場需求的價格點。

射頻放大器

為RF功率級選擇的放大器是采用InGaP工藝制造的低成本、高性能寬帶線性放大器。它們線性放大ADF4602的輸出,并補償RF雙工器和開關網絡中的損耗。ADL5542內置偏置和匹配功能;ADL5320需要外部匹配,采用行業標準塑料SOT-23封裝。兩個放大器均直接采用5 V電源軌供電,因此無需外部偏置電路。放大器的主要規格如表1所示。ADI RF放大器設計采用專有技術,具有出色的線性度與電源電流的關系。

表 1.ADF5542和ADL5320的主要指標 (@ 2 GHz)

|

規范 |

ADL5542 | ADL5320 |

| 獲得 |

19分貝 |

13.2分貝 |

|

P1分貝 |

18.9分貝 |

25.7分貝 |

|

輸出 IP3 |

37分貝 |

42分貝 |

|

噪聲系數 |

3.1分貝 |

4.4分貝 |

|

電源電流(5 V電源) |

97毫安 |

104毫安 |

發射輸出功率和干擾抑制

為了減輕干擾,家庭基站必須靈活、智能地設置其輸出功率,以應對多個以相同頻率工作的家庭基站彼此靠近的部署(例如,在公寓大樓中)。在這里,每個家庭基站都需要以較低的輸出功率進行傳輸,以避免同頻干擾。此外,家庭基站不會對在相鄰信道上運行的地理上相鄰的宏蜂窩基站造成干擾,因為這會給連接到宏蜂窩網絡的附近移動電話產生死點。因此,家庭基站將具有相鄰信道保護要求,迫使其測量相鄰下行信道中的功率,并根據預定公式設置自己的功率,以免阻礙宏基站信號。我

為了使家庭基站滿足所需的價位并便于客戶安裝,這些干擾緩解技術必須是自動化的,并且不得要求訓練有素的現場技術人員或家庭用戶輸入。此過程應在用戶首次打開框時自動啟動,此后定期更新。ADI設計中的頻段1監控接收器和ADF4602上的大發射動態范圍相結合,使家庭基站供應商無需外部輸入即可自動實現這些干擾抑制技術。監控接收器允許精確測量相鄰通道中的功率并相應地調整輸出功率。需要大約30 dB的總發射功率動態范圍。

無線電性能測量

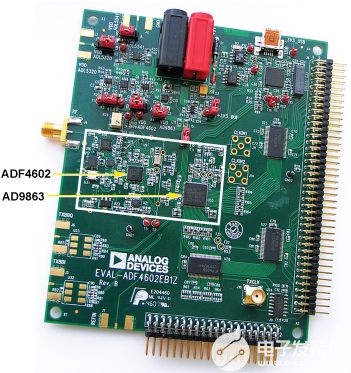

為了根據 TS25.104 無線電系統規范評估收發器芯片組,上述收發器產品線已納入評估板設計。如圖6所示的評估平臺可以對發送和接收鏈進行獨立測試,以及單個組件測試。該評估板包括圖1中框圖的功能以及電源調理功能。無線電部分包括ADF4602、AD9863、ADL5542、ADL5320、VCTCXO以及所有相關的前端開關和濾波器,在電路板上占用1英寸×2英寸的空間。請注意,該板尚未針對節省空間進行優化,因為它是為測試目的而配置的,但可以實現更緊湊的生產設計。下面列出了一些針對TS25.104規范的關鍵測試結果,以說明評估板上ADI芯片組的性能。

圖6.ADF4602/AD9863評估板

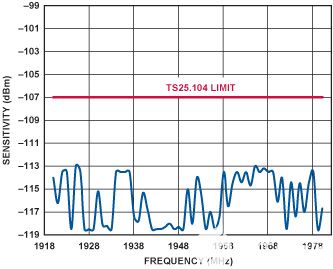

圖7顯示了頻段1接收器靈敏度測量結果。接收器靈敏度是衡量接收器檢測低電平信號的能力的指標,也是接收器噪聲系數的指標。在此測量中,使用12.2 kHz基準電壓源。ADF4602增益設置為80 dB。接收器靈敏度在整個頻段內比 TS25.104 規范高出 6 dB 或更多。

圖7.頻段 1 接收器靈敏度。

接收器的另一個關鍵規格是阻塞條件下的性能。阻塞測試模擬在相鄰通道中存在大量不需要的信號的情況下接收所需信號的能力。UL 12.2-kHz 參考信號設置為 –101 dBm,阻塞信號注入,直到 BER 為 10–3被測量。如表2所示,ADF4602在所有三種情況下都超過了TS25.104,并有一定的裕量。

表 2.接收器阻塞測試與 TS25.104 規范的比較摘要

|

接收器阻塞規格 |

TS25.104 規格限制 |

ADF4602評估板測試結果 |

|

相鄰通道選擇性 |

–38 分貝 |

–31 dBm(7 dB 裕量) |

|

10 MHz WCDMA 阻斷器 |

–30 分貝 |

–21 dBm(9 dB 裕量) |

|

20 MHz 帶外 CW 阻塞器 (1900 MHz) |

–15 分貝 |

–11 dBm(4 dB 裕量) |

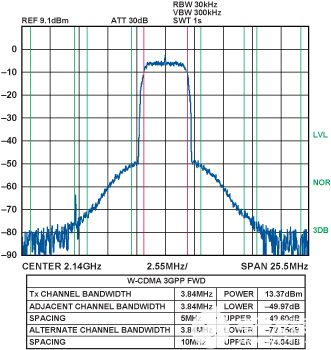

傳輸鏈質量的關鍵指標是相鄰信道泄漏比(ACLR)和誤差矢量幅度(EVM)。在這兩種情況下,這些測試都是組合發射鏈線性度的關鍵指標。表3匯總了ADI評估板上與TS25.104規格相比的測量結果。它還包括峰值代碼域誤差,這是一種 EVM 測量,可確保誤差在代碼域上均勻分布。第二在所有情況下,ADF4602評估板的裕量都超過了TS25.104規格。ACLR測量中使用的輸出頻譜圖如圖8所示。

表 3.變送器測試與 TS25.104 規范的對比摘要

|

變送器規格 |

TS25.104 規格限制 |

ADF4602評估板測試結果 |

|

誤差矢量幅度 (EVM) |

<12% |

4% |

|

峰值代碼域錯誤 (pkCDE) |

<–33 分貝 |

–46 分貝 |

|

相鄰通道(5 MHz) ACLR |

<–45 分貝 |

–49 分貝 |

|

備用信道 (10 MHz) ACLR |

<–50 分貝 |

–72 分貝 |

圖8.W-CDMA 頻段 1 信號的 ACLR 測量,輸出功率為 13 dBm。

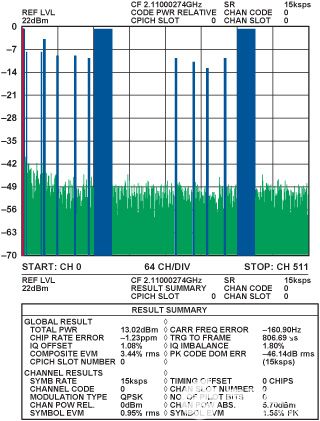

圖9顯示了典型家庭基站配置的發射EVM圖,涉及兩個HSDPA通道和多個語音/數據通道。復合 EVM 低于 4%。對該電路的評估表明,EVM主要由調制器輸入端的I/Q失調電壓引入的LO泄漏影響,這是直接變頻發送器的一個特性。如上所述,可以使用AD9863直流失調控制來校準這些失調。

圖9.典型家庭基站配置的 EVM 測量。

結論

新興的家庭基站應用對無線電設計人員提出了獨特的挑戰,即在保持基站性能的同時最大限度地降低成本。ADI 3G家庭基站芯片組由集成無線電收發器ADF4602、MxFE基帶收發器AD9863以及ADL5542和ADL5320射頻放大器組成,使家庭基站設計人員能夠以緊湊的外形滿足TS25.104規范。

審核編輯:郭婷

-

收發器

+關注

關注

10文章

3338瀏覽量

105541 -

路由器

+關注

關注

22文章

3641瀏覽量

112813 -

無線電

+關注

關注

58文章

2114瀏覽量

115823

發布評論請先 登錄

相關推薦

Analog Front End for 3G Femto Base Stations Brings Wireless Connectivity Home

150塊ST NUCLEO-F412ZG開發套件等你帶回家活動發群截圖

完整3G移動基站電源防雷解決方案

基于3G毫微微基站模擬前端的家庭無線連接

Femto基站及其射頻方案

K歌新潮流 “錢柜”帶回家雷客無線點歌機風靡市場

3G基站現場無線測試指南

3G無線基站技術及標準化

3G蜂窩Femto基站的開發和部署

通過Femto基站的3G信號改善改善本地無線覆蓋

為什么需要使用Femto基站3G蜂窩Femto基站單芯片收發器的設計資料說明

3G Femto基站的模擬前端將無線連接帶回家

3G Femto基站的模擬前端將無線連接帶回家

評論