編者注:擴頻時鐘是一個非常好的器件或者功能,這是對于EMC工程師而言的,但是對于SI工程師來講,這可能是導致某些抖動增大問題的根源。在早期做項目的時候,就曾遇到過這類的爭執。

EMI是電子產品設計工程師不可繞開的一個話題。很多工程師在設計時都會遇到如何減小EMI的影響,使產品能正常的工作或者上市。

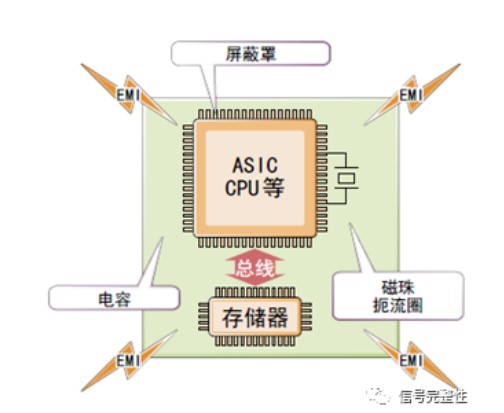

當然,解決EMI問題的方法非常多,比如做好電路匹配、做好隔離、屏蔽、減緩信號邊沿變化速率等等。

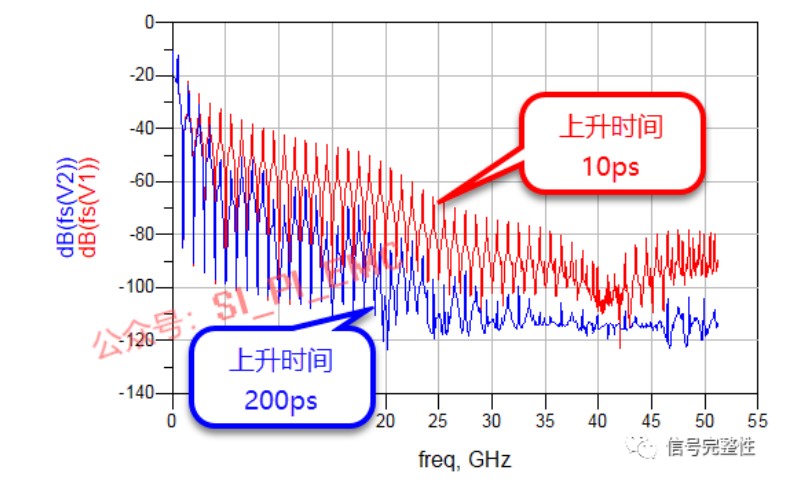

減緩邊沿變化速率的方法有使用端接的方法、減小信號的驅動能力、使用擴頻時鐘等。

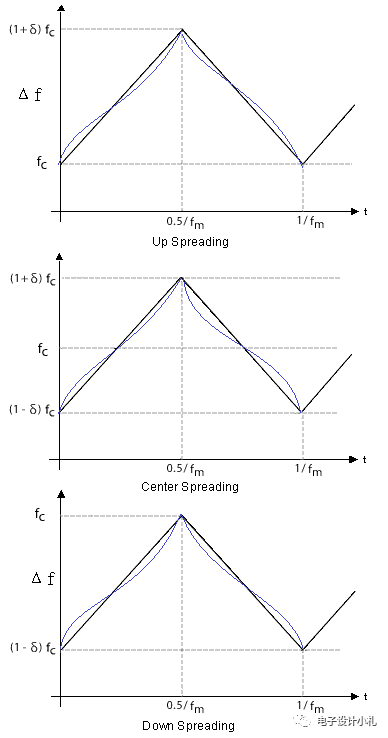

本文主要分享的是擴頻時鐘。擴頻時鐘(SSC:Spread Spectrum Clock)是為了防止數字信號或者時鐘由于頻譜在某個頻點上功率過高而引起的EMI問題,所以對時鐘或者數據的周期進行周期性調制(三角波調制)。SSC的單位是ppm(百萬分之一個時鐘或者一個數據的周期),該值表示最大的時鐘周期或者數據周期為UI*(1+Xppm)。

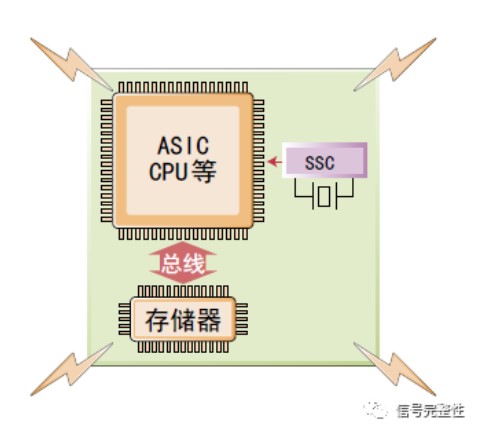

以前使用SSC都是外部器件,一般在電路上加上SSC器件,如下圖所示:

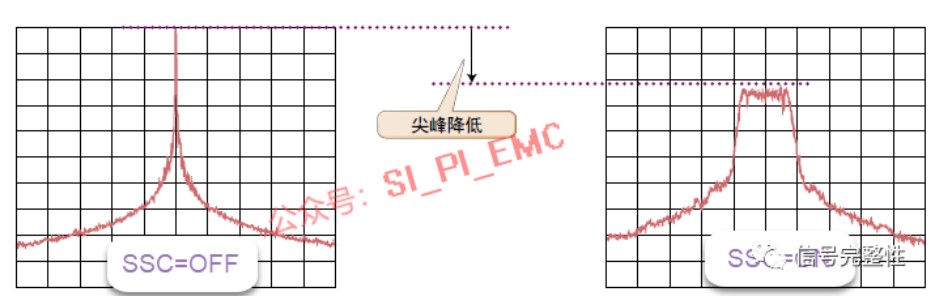

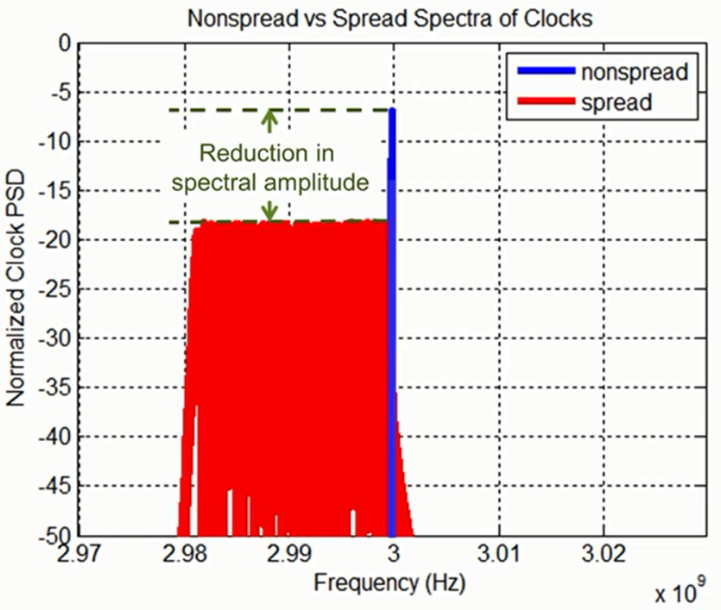

當使用SSC之后,其EMI輻射能量會顯著降低,并且波峰更加的寬平:

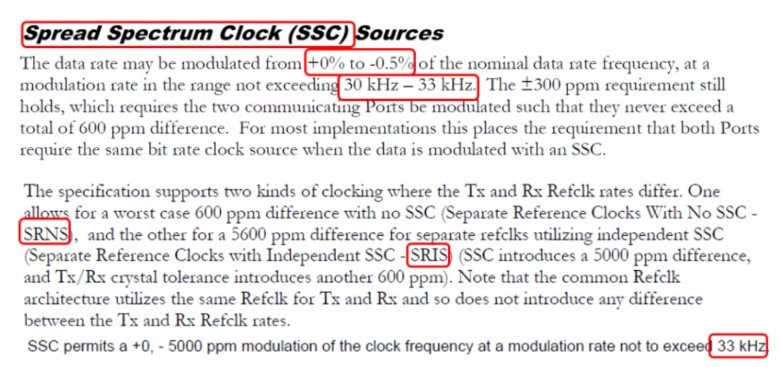

現在很多總線,如USB3.0、QPI、PCIE、SATA、SAS等信號都支持SSC功能,并不需要在外部添加額外的SSC器件。使用SSC功能可以大幅降低無用的輻射,從而減少旁路電容、扼流圈、磁珠以及屏蔽罩等其他抑制干擾組件的使用,這樣能有助于實現產品快速上市,并且能使產品小型化。

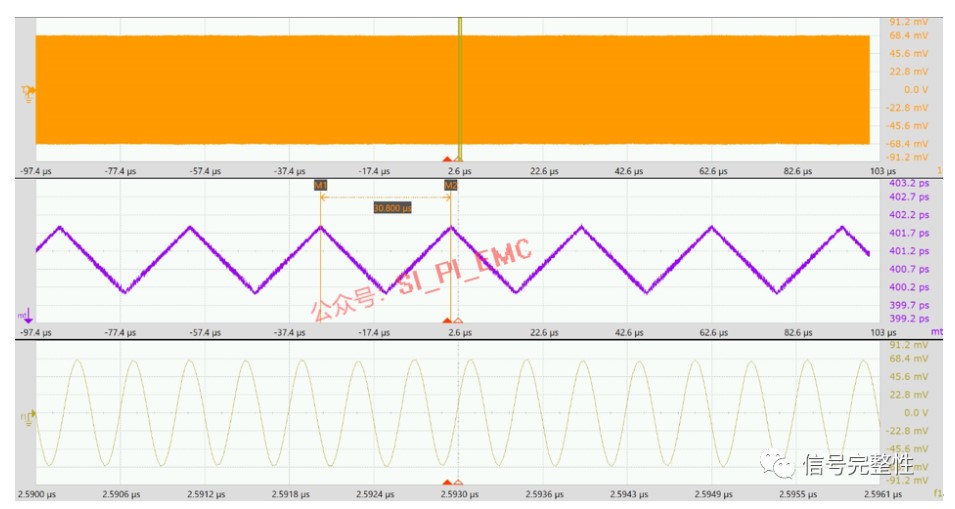

在某些高速串行總線測試時,也會針對SSC項進行測試,如下圖則為SB3.0 5Gbps 使用CP1 碼型測量SSC 的結果:

當然,為什么要針對性的測試呢?其中一個重要原因就是SSC確實能抑制EMI的影響,但是會導致信號的抖動增加。如果抖動過大或者超過總線規范要求時,這就有可能導致信號的誤碼增加,進而影響到電子產品系統的穩定性。所以在產品設計過程中,要平衡EMI的表現和SI的性能。

審核編輯:劉清

-

emi

+關注

關注

53文章

3582瀏覽量

127353 -

SAS

+關注

關注

2文章

521瀏覽量

32834 -

擴頻時鐘

+關注

關注

0文章

8瀏覽量

10585 -

ssc

+關注

關注

0文章

24瀏覽量

11178

原文標題:擴頻時鐘(SSC):用好了,它是解決問題的利器;用不好,它就是問題的根源!

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于時鐘擴頻技術的行車記錄儀EMI抑制的設計與應用

控制板級時鐘分配期間出現的EMI對時鐘的影響

EMI問題可以通過高速PCB來控制解決嗎

擴頻時鐘發生器

擴頻時鐘發生器

擴頻時鐘發生器

PowerXR EMI降低技術利用擴頻時鐘抖動

通過使用展頻IC解決EMI時鐘問題

時鐘EMI超標實驗案例與整改

利用擴頻時鐘來降低EMI

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發生器數據表

擴頻時鐘SSC可以某個頻點上功率過高而引起的EMI問題嗎

擴頻時鐘SSC可以某個頻點上功率過高而引起的EMI問題嗎

評論