AD1859在單芯片上提供業界功能最完整的16/18位立體聲數字音頻播放子系統。它將串行數字輸入數據轉換為濾波、緩沖、低失真、增益控制的立體聲模擬輸出。其異步主時鐘數字鎖相環(DPLL)允許其接受來自各種來源的數據,時鐘速率為28 kHz至52 kHz(使用外部27 MHz晶體),抑制采樣時鐘抖動并大大簡化了接口。

它是許多應用的理想選擇,包括數字有線電視和直播衛星機頂解碼盒、視頻 CD 播放器、CD-I 播放器、高清電視、數字音頻廣播接收器、數字音頻工作站、多媒體計算機以及各種形式的 CD 和數字磁帶播放器。

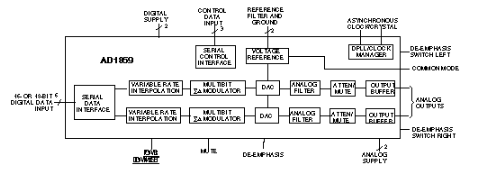

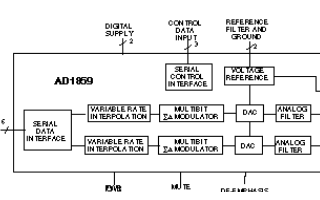

單芯片AD1859包括(圖1)可變速率過采樣數字插值濾波器、具有抖動功能的創新型多位Σ-Δ型調制器、耐抖動數模轉換器(DAC)、開關電容和連續時間模擬濾波器、模擬輸出驅動電路以及采用28引腳SOIC或SSOP封裝的片內直流基準電壓源。片內音量控制(節省系統成本)包括立體聲衰減器和靜音,完全通過SPI兼容串行控制端口編程?。

圖1

作為AD1859具有特殊優勢的典型應用,MPEG音頻要求三種不同的采樣速率:32、44.1和48 kHz。對于典型的Σ-Δ音頻DAC,設計人員必須提供一個外部時鐘電路來合成與這三個采樣頻率中的每一個相關聯的“主時鐘”。AD1859是首款具有異步主時鐘的音頻DAC,簡化了這一任務。只需要一個 27 MHz 時鐘(外部提供或使用外部 27 MHz 晶體在片上生成);AD1859的鎖相環可自動適應不同的輸入采樣速率,從而顯著節省系統成本。DPLL 將在 100 到 200 毫秒內鎖定到任何新的采樣率(應用于左右時鐘引腳);高于和低于采樣頻率 15Hz 的抖動分量在每倍頻程 6dB 時被抑制(例如,高于或低于采樣速率 150Hz 的抖動降低 20dB)。

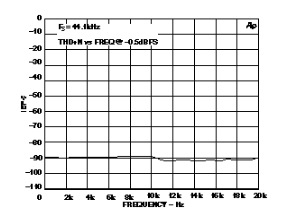

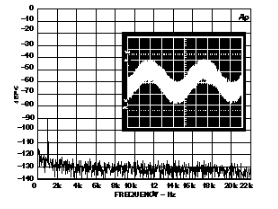

保證的性能特征包括使用A重量濾波器的最小動態范圍為88dB(無濾波器為85.7dB),以及音頻頻段(84 Hz至0 kHz)上的最大總諧波失真和噪聲(THD+N)為-0063dB(20.20%)。圖2是-0.5 dBFS幅度下THD+N與頻率的典型關系圖。圖3是-90 dB、1 kHz音調的FFT,并附有時域圖,展示了在這種低電平下不受諧波、雜散和量化效應的影響,這是模擬系統的典型特征,但很難通過數字方式實現。

圖2

AD1859的另一個獨特特性是創新的多位Σ-Δ調制器(見側欄),有助于抑制時鐘抖動,從而增強系統可聽性優勢,降低帶外能量,從而節省系統成本。

圖3

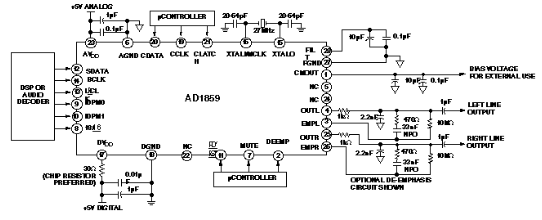

通過靈活的串行數據輸入端口與AD1859的接口非常簡單,該端口允許與各種ADC、DSP、AES/EBU接收器和采樣速率轉換器無縫互連。多功能串行數據輸入端口可配置為左對齊,I2S 對齊、右對齊和 DSP 串行端口兼容模式。該芯片接受 MSB 優先、二進制補碼格式的 16 位或 18 位音頻數據。AD1859支持連續可變采樣速率和基本線性(在±0.1%)以內的相位響應。在模擬輸出級可選擇去加重功能,只需添加幾個外部組件即可實現改進的采樣率不變降噪。(圖4)

圖4

省電模式(48mW vs. 330mW)可在器件處于非活動狀態時最大限度地降低功耗。整個立體聲數字音頻播放子系統采用+5 V單電源供電,溫度范圍為-40°C至+105°C;它采用 28 引腳 SOIC 和 SSOP 封裝。

AD1859性能的關鍵

AD1859具有極佳的保真度和低電平線性度,大大降低了電路復雜性,可輕松與DSP(數字信號處理器)和ADC(模數轉換器)接口,并降低數字音頻播放系統的功耗和成本。

它與傳統設備有兩個關鍵區別。首先是其獨特的DPLL(數字鎖相環)時鐘管理器。這是一款異步采樣速率管理器,可自動調整輸入采樣頻率,并允許AD1859采用與其自身主時鐘不同的頻率進行時鐘計時。它基于ADI公司開發的專利異步采樣率轉換技術(Analog Dialogue 28-1,1994,第9-11頁)。到目前為止,還沒有其他音頻DAC具有此功能。其他音頻DAC(數模轉換器)需要一個調諧良好的高頻主時鐘,其運行速度是預期音頻采樣率的256或384倍。這種高頻同步時鐘的生成和管理對板級設計人員來說非常繁重。

外部異步時鐘振蕩器可用于提供AD1859的主時鐘;但是,AD1859內置一個片內振蕩器,因此設計人員只需提供廉價的石英晶體或陶瓷諧振器作為外部時基。AD1859的板載DPLL將在大約1 ms內鎖定到主時鐘頻率的512/1至1024/100之間的任何輸入采樣速率。晶體時基或MCLK輸入上的抖動被抑制(憑借片內開關電容濾波器),以及輸入LRCLK輸入上的抖動達到音頻DAC前所未有的水平。

AD1859的第二個與眾不同特性是其獲得專利的多位Σ-Δ調制器,其帶外噪聲能量顯著低于競爭IC。較低的帶外噪聲能量減少了對DAC后濾波的需求,因此所有必要的DAC后濾波(可選的模擬去加重除外)都集成在芯片上。多位Σ-Δ調制器的另一個特性是其對數字基板噪聲的高抗擾度,進一步提高了音頻信號的完整性。

什么是多位Σ-Δ調制器?在基本方法中,典型的Σ-Δ調制器具有兩個量化級別,DAC必須平均脈寬調制的滿量程方波;但在AD1859中,使用了17級量化,平均濾波器的輸入可以被認為是對1級階梯的16/17滿量程元件進行平滑處理的簡單得多的任務。此外,AD1859以輸入采樣速率的128倍對輸入信號進行采樣,是傳統采樣速率的兩倍。額外的量化水平和更高的過采樣率意味著輸出頻譜包含的帶外噪聲能量水平要低得多;允許更簡單的DAC后重建濾波器。其降低的過渡帶陡度和衰減要求可降低相位失真并提高保真度。

有缺點嗎?傳統上限制多位Σ-Δ轉換器性能的問題是用于對量化電平求和的無源電路元件的非線性。設計師發明了一種革命性的架構來克服這個問題1.

該芯片的其他有趣功能包括使用具有三角概率分布函數的抖動來進一步降低量化噪聲;片內低通濾波由二階開關電容濾波器和一階模擬連續時間濾波器組成。除了濾除噪聲外,它還減少了任何殘留的主時鐘抖動的影響。

審核編輯:郭婷

-

芯片

+關注

關注

450文章

49614瀏覽量

417058 -

濾波器

+關注

關注

158文章

7591瀏覽量

176542 -

接收器

+關注

關注

14文章

2441瀏覽量

71521

發布評論請先 登錄

相關推薦

電視節目立體聲播出方案探討

單聯電位器構成的立體聲平衡控制器電路分析簡述

采用數字輸入D類音頻放大器的高性能立體聲音頻子系統

單芯片藍牙立體聲耳機解決方案:BC57F687A05

請問我可以僅使用單輸出立體聲輸出嗎?

TPA2050D4 模擬輸入音頻子系統 集成立體聲D類功率放

影院數字立體聲自同步系統的設計

參量立體聲簡介

LM4934 BOOMER 音頻功率放大器系列3D音頻子系統與立體聲揚聲器,OCL/SE立體聲耳機,耳機和單聲道電平輸出

基于STK4141II的立體聲功放電路

單芯片數字立體聲子系統

單芯片數字立體聲子系統

評論