隨著低功耗手持設(shè)備變得越來越普遍,混合使用5 V、3.3V、2.5 V和1.8 V器件的印刷電路板變得很普遍,這使得JTAG鏈的設(shè)計成為一項具有挑戰(zhàn)性的任務(wù)。設(shè)計人員必須確定JTAG鏈的工作電壓以及放置不同電壓的器件的順序。本文比較了設(shè)計多電壓JTAG鏈的幾種方法,提供了一些制作魯棒、無差錯設(shè)計的技巧和技術(shù)。

菊花鏈,或通過JTAG端口連接多個DSP、FPGA、CPLD和其他邏輯器件,允許使用單個JTAG連接器控制它們。菊花鏈通常用于具有多個JTAG器件的電路板,菊花鏈連接TDI和TDO引腳以形成串行路徑。鏈的輸入是第一個設(shè)備的TDI;鏈的輸出是最后一個設(shè)備的 TDO。所有器件的TRST、TCK和TMS引腳并聯(lián)連接。菊花鏈可以設(shè)計為允許繞過鏈中的一個或多個設(shè)備以進行調(diào)試,方法是提供可以根據(jù)所需目標設(shè)備安裝或移除的跳線。理論上可以菊花鏈連接的設(shè)備數(shù)量是無限的,但在具有大約八個以上的設(shè)備的鏈中經(jīng)常發(fā)生時序問題和間歇性崩潰,尤其是在時鐘速率較高的情況下。

為了滿足JTAG時序要求,當鏈路中有超過四個器件時,應(yīng)將緩沖器放置在TCK和TMS上以保持信號完整性,并且每個緩沖器驅(qū)動不超過四個器件。例如,具有六個設(shè)備的鏈需要兩個用于TCK的緩沖區(qū)和兩個用于TMS的緩沖區(qū)。驅(qū)動器應(yīng)該是高速的(低傳播延遲),具有足夠的強度來驅(qū)動四個或更多設(shè)備。

硬件工程師可能需要菊花鏈連接不具有相同 I/O 電壓的設(shè)備。在單個鏈中連接所有器件可能不是最佳解決方案,因此設(shè)計人員應(yīng)考慮對鏈進行分區(qū),以滿足專有調(diào)試工具的要求。可能需要電平轉(zhuǎn)換器來適應(yīng)多個電壓電平,并且必須保持信號完整性。設(shè)計和測試的復(fù)雜性顯著增加,需要IEEE 1149.1專業(yè)知識來集成和測試系統(tǒng)。本文介紹了實現(xiàn)多電壓JTAG鏈的兩種方法。

每個電壓系列的單獨JTAG鏈

當多個器件具有相同的I/O電壓時,建議使用這種方法,將所有具有相同JTAG I/O電壓的器件放在一個鏈中,每個電壓使用單獨的鏈。每個鏈都支持其類別中的所有設(shè)備,消除了其他設(shè)備無法正常工作的可能性,并減少了其他供應(yīng)商必須與JTAG鏈接口時的混亂。圖1顯示了具有相同I/O電壓器件的JTAG鏈。在這種情況下,不需要電壓轉(zhuǎn)換器(VT)。

圖1:具有相同I/O電壓器件的JTAG鏈

多電壓JTAG鏈

有時最好將所有JTAG器件放在一個鏈中。當每個電壓系列中沒有足夠的器件來構(gòu)建單獨的JTAG鏈時,建議使用這種方法。要成功連接JTAG鏈中兩個具有不同電壓的器件,必須滿足以下要求:

VOH最小驅(qū)動器的(最小高輸出電壓)必須大于接收器的VIHmin(最小輸入高壓)。

卷.max驅(qū)動器的(最大輸出低電壓)必須小于接收器的VILmax(最大輸入低電壓)。

驅(qū)動器的輸出電壓不得超過接收器的I/O電壓容差。

表1顯示了不同電壓標準的常見最小和最大電壓。有關(guān)更具體的數(shù)據(jù),設(shè)計人員應(yīng)參考器件的數(shù)據(jù)手冊。

表 1:典型 I/O 標準及其相關(guān)的最小和最大電壓

|

I/O Standard |

VIL (min) |

VIL (MAX) |

VIH (MIN) |

VIH (MAX) |

VOL (MAX) |

VOH (MIN) |

|

LVTTL |

-0.3 | 0.8 | 2.0 | 3.45 | 0.4 |

VCCO-0.4 |

|

LVCMOS33 |

-0.3 | 0.8 | 2.0 | 3.45 | 0.4 |

VCCO-0.4 |

|

LVCMOS25 |

-0.3 | 0.7 | 1.7 |

VCCO+0.3 |

0.4 |

VCCO-0.4 |

|

LVCMOS18 |

-0.3 |

35% VCCO |

65%VCCO |

VCCO+0.3 |

0.45 |

VCCO-0.45 |

|

LVCMOS15 |

-0.3 |

35% VCCO |

65%VCCO |

VCCO+0.3 |

0.45 | VCCO-0.45 |

多電壓JTAG鏈設(shè)計指南

將最高電壓的設(shè)備放在鏈的開頭,下一個最高電壓,依此類推,直到最后放置最低電壓的設(shè)備。按順序?qū)⒆罡唠妷褐糜谧畹碗妷篔TAG信號,可以通過下一個器件的輸入正確解釋一個器件TDO輸出上的邏輯高電平。

驗證每個設(shè)備是否能夠承受來自后續(xù)設(shè)備的最大電壓。例如,如果第一個器件是 3.3V 器件,下一個器件是 1.8V 器件,請確保 1.8V 器件的輸入電壓至少為 3.6 V。

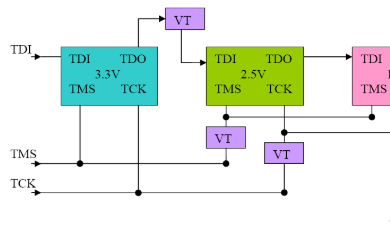

驗證仿真器是否可以正確解釋來自最低電壓設(shè)備的 TDO。在示例中,確保 VOH最小的 1.8V 器件大于 VIH最小的 3.3V 器件。如果沒有,則應(yīng)使用高速電壓轉(zhuǎn)換器將TDO轉(zhuǎn)換為仿真器的正確電壓。VT不應(yīng)該注冊(時鐘)信號,因為這會將信號延遲一個時鐘,導(dǎo)致JTAG鏈失效。ADI公司的雙向邏輯電平轉(zhuǎn)換器ADG3304包含四個雙向通道,可用于多電壓數(shù)字系統(tǒng)應(yīng)用。圖 2 顯示了具有 3.3V、2.5V 和 1.8V I/O 電壓的器件,其中電壓較低的器件的 I/O 可以承受前一個器件的較高電壓。TDO使用VT將電壓從1.8 V提升至3.3 V。

圖 2:JTAG 鏈中具有不同 I/O 電壓的三個器件

當?shù)蛪浩骷荒艹惺芮爸闷骷母邏簳r,應(yīng)對所有JTAG信號使用高速電壓轉(zhuǎn)換器。仿真器應(yīng)用作除TDO以外的所有電壓轉(zhuǎn)換器的輸入。不要級聯(lián)電壓轉(zhuǎn)換器,因為這會增加傳播延遲。圖3顯示了較低電壓部分無法承受較高電壓I/O的情況,因此每個信號都需要VT。

圖 3:三個具有不同 I/O 電壓的器件,帶有用于 JTAG 信號的電壓轉(zhuǎn)換器

如果只有一個器件不能承受前一個器件的I/O電壓,則只需要該器件的電壓轉(zhuǎn)換器。例如,當JTAG鏈中的I/O電壓為3.3 V、2.5 V和1.8 V時,1.8 V器件具有2.5 V容限I/O,因此2.5 V器件可以使用1.8 V信號。在圖 4 中,2.5V 器件沒有 3.3V 容限 I/O,但 1.8V 器件具有 2.5V 容限,因此 VT 僅用于 2.5V 部分。

圖 4:三個具有不同 I/O 電壓的設(shè)備。1.8V 器件具有 2.5V 兼容 I/O

如果約0.4 V的壓降足以將電壓電平從較高電壓調(diào)整到較低電壓電平,則可以使用具有快速恢復(fù)時間的肖特基二極管代替電壓轉(zhuǎn)換器。安森美半導(dǎo)體的1SS383T1G肖特基二極管具有0.48 V的正向壓降和25 pF的容性負載。Diodes Inc. 的 SD103ATW 是三個完全隔離的肖特基二極管,正向壓降電壓約為 0.3 V,容性負載為 50 pF,也可用于此應(yīng)用。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1620文章

21510瀏覽量

598951 -

連接器

+關(guān)注

關(guān)注

98文章

13845瀏覽量

135096 -

JTAG

+關(guān)注

關(guān)注

6文章

393瀏覽量

71433

發(fā)布評論請先 登錄

相關(guān)推薦

是否有可能擁有3.3V和2.5V JTAG鏈?

有什么辦法能成功編程JTAG鏈上的任何設(shè)備嗎?

如何調(diào)試JTAG鏈與非xilinx器件?

多個MCU使用的菊花鏈是怎樣通過JTAG連接的呢

IMX8m Plus邊界掃描檢查鏈失敗的原因?

PE多鏈路JTAG/BDM Kinetis編程報錯怎么解決?

T1024 codewarrior無法正確配置JTAG鏈怎么解決?

淺談多電壓JTAG鏈設(shè)計實現(xiàn)

XJTAG邊界掃描—JTAG鏈調(diào)試器

SPI、UART、RGMII、JTAG接口的低電壓轉(zhuǎn)換

構(gòu)建多電壓JTAG鏈

構(gòu)建多電壓JTAG鏈

評論