作者:Mike Curtin and Paul O'Brien

為了提高現代無線電的靈敏度和選擇性,需要最大限度地減少相位噪聲和參考雜散,并縮短鎖定時間。本文概述的電路改善了本振(LO)的性能。

相位噪聲是LO信號純度的量度。它是通過在給定載波偏移處的1 Hz帶寬中輸出基波功率與噪聲功率的比值來確定的。結果以 dBc/Hz 表示。

由于頻率合成器中的內部開關,輸出中可能會出現雜散頻率元件(雜散)。在整數N分頻頻率合成器中,它們通常是由于鑒頻鑒相器(PFD)頻率引起的;在小數N分頻器件中,它們可能是合成器架構性質的結果。在整數N分頻鎖相環(PLL)中,它們稱為參考雜散。

鎖定時間是指將輸出從一個頻率切換到另一個頻率所需的時間,這是許多系統中的一個重要規范。一般來說,當輸出穩定在最終所需頻率的一定百分比或百萬分之一 (ppm) 以內時,或者已鎖定到最終相位的指定度數內,我們說輸出被切換或已鎖定到新頻率。

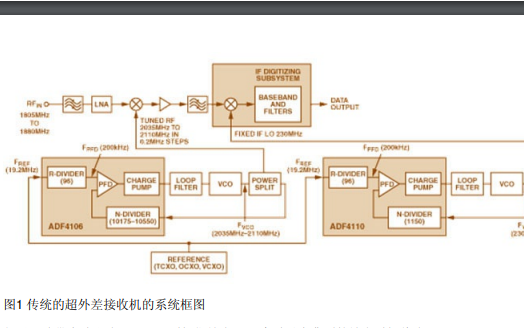

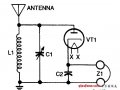

傳統接收器實現

圖1顯示了最流行的接收器架構(超外差接收器)的一般框圖。此處顯示的系統是專為滿足移動電話 DCS1800 標準而設計的接收器的典型系統。對于此標準,接收 (Rx) 頻段為 1805 MHz 至 1880 MHz。

在圖1中,RF輸入施加于RF濾波器,然后是低噪聲放大器(LNA)。然后,信號通過具有調諧LO輸入的混頻器混頻至中頻(IF)。隨后進行額外的濾波,最終混頻器使用單頻LO將固定IF降至基帶。

調諧RFLO以干凈穩定的基準頻率開始,然后是ADF4106 PLL頻率合成器和壓控振蕩器(VCO)。基準電壓源由溫控 (TCXO)、壓控 (VCXO) 或恒溫箱控制 (OCXO) 晶體振蕩器提供。PLL頻率合成器的R分頻器將此參考條件設置為等于整數N分頻系統中通道間距的值,或小數N分頻系統中通道間距的倍數。PFD 比較環路輸出,FVCO,除以N,R分頻器的輸出,環路通過驅動VCO使PFD輸出趨于零FVCO = F聚苯乙烯×·N變化以改變LO輸出頻率,從而調諧無線電。

LO的相位噪聲取決于許多因素:參考噪聲;頻率合成器(R分頻器、N分壓器、PFD和電荷泵)中的噪聲;N 的值;以及合成器 PFD 的工作頻率。

LO(dB)的相位噪聲可以用以下公式來描述:

PN = PN合成器+ 20 對數 N + 10日志 F聚苯乙烯

哪里:

PN合成器是頻率合成器的相位噪聲貢獻(在相應的數據手冊中給出,單位為dB)

20 log N 是合成器中 N 值引起的附加噪聲

10日志 F聚苯乙烯是頻率合成器PFD頻率引起的噪聲貢獻。

*有關更詳細的說明,請參閱《模擬對話》,第 6 卷,第 35 期,6 年 2001 月至 <> 月,“使用新的寬帶整數 N 分頻 PLL 頻率合成器設計直接 <> GHz 本地振蕩器”。

基準雜散電平取決于:PFD設計、PFD電荷泵部分的泄漏、PLL環路帶寬和VCO靈敏度。鎖定時間取決于:PFD頻率和PLL環路帶寬。

在接收器中,如果IF選擇為230 MHz,調諧RF必須以2035 kHz步長從2110 MHz變為200 MHz(使用高端注入)。使用整數N分頻架構來做到這一點,需要200 kHz的PFD頻率,N值將在10175(2035 MHz)到10550(2110 MHz)之間變化。

使用最好的市售元件(ADF4106 PLL頻率合成器),該系統的預期帶內相位噪聲為–85.6 dBc/Hz。 此類系統中的典型基準雜散在88 kHz時為–200 dBc,在90 kHz時為–400 dBc。

圖1.傳統超外差接收器的框圖。

使用20 kHz的環路帶寬時,10度相位誤差的典型鎖定時間為250 μs。

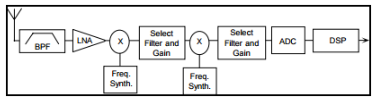

替代接收器實現

ADI公司現已推出新型高帶寬PLL頻率合成器ADF4107。其RF級能夠在高達7.0 GHz的頻率下工作,而PFD頻率能夠在高達104 MHz的頻率下工作。這種高帶寬能力可用于實現新型接收器架構,如圖2所示。在這里,每級的LO來自更高的頻率,該頻率是所需頻率的整數倍。此外,調整是在 IF 部分中完成的。這允許使用非常高的倍數,以改善整體相位噪聲和鎖定時間。

固定射頻

在圖2中,固定頻率RF LO將信號向下轉換為IF頻段,并且通道在IF頻段進行調諧。再次以DCS1800為例,我們可以選擇1520 MHz的固定RF LO。這可以通過除以6080從4 MHz信號得出,如圖2所示。

圖2.替代接收器框圖

RF LO的相位噪聲為:

–219 + 20 對數 950 + 10 對數 (6.4 × 106) – 20 log 4

= –219 + 59.5 + 68 – 12

= –103.5 dBc/Hz

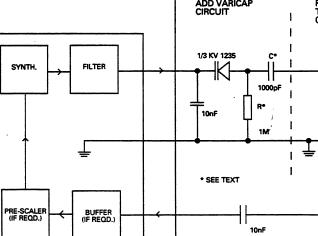

基準雜散將出現在距載波6.4 MHz的偏移處,并且非常小(< –90 dBc),因為(a)由于12分頻電路將產生4 dB的衰減,以及(b)由于這是一個固定頻率LO,環路帶寬可以降低(例如20 kHz)。簡單的 20 dB/十倍頻程衰減將進一步衰減雜散。

在 200 kHz、400 kHz、600 kHz 和 800 kHz 下不會有雜散;鎖定時間不是問題,因為固定RF部分不會進行調諧。

調諧中頻

繼續以DCS1800為例,圖2顯示了調諧的IF,從285 MHz到360 MHz,步長為200 kHz。為了實現這一點,使用3.2 MHz的PFD頻率,以4560.5760 MHz步長產生從3 MHz到2 MHz的初始LO。將這些頻率除以 16 得到所需的 285 MHz 至 360 MHz,步長為 200 kHz。

調諧IF的最差情況相位噪聲為:

–219 + 20 對數 1800 + 10 對數 (3.2 × 106) – 20 對數 16

= –219 + 65 + 65 – 24

= –113 dBc/Hz

參考雜散將出現在與載波偏移 3.2MHz 處。通過選擇500 kHz的環路帶寬,3.2 MHz的雜散將低于–90 dBc。在DCS系統中,雜散降低的重要頻率為200 kHz、400 kHz、600 kHz和800 kHz。但是,在建議的配置中,這些頻率下不會存在雜散,因為我們在3.2 MHz的高PFD頻率下工作。

當環路帶寬設置為500 kHz,PFD頻率設置為3.2 MHz時,鎖相將在不到10 μs的時間內實現10度以內。頻率鎖定響應如圖3所示。

圖3.優化的 IF 的鎖定時間。

篩選注意事項

所考慮的兩種架構本質上都是超外差,具有兩個下變頻階段。過濾在每個階段都至關重要。

在圖1中,LNA之前的RF濾波器抑制非常強的帶外干擾源。IF濾波器可以是窄帶(GSM中為200 kHz),以抑制帶內干擾源。

在圖2中,RF濾波器與圖1相同。但是,圖2中的IF濾波器不能是窄帶。它必須通過整個頻段,因為調諧尚未發生。這意味著作為基帶處理的一部分,帶內干擾源必須在鏈的稍后階段進行濾波。ADI公司提供多個IF至基帶接收器。其中包括AD6650、AD6652、AD9870和AD9874。在分析圖2的架構時,應仔細考慮它們。

結論

以更高的PFD頻率(最終LO頻率的整數倍)操作PLL內核可改善相位噪聲、輸出基準雜散和鎖定時間。此外,調諧IF架構可提供更高的性能,因為整數倍可以更高。但是,需要仔細考慮過濾要求。

本提案中使用的示例適用于整數N分頻PLL,即ADF4107,但配置不限于此。使用這種具有小數N分頻架構的配置來實現類似的增益也是非常可行的。

審核編輯:郭婷

-

濾波器

+關注

關注

160文章

7749瀏覽量

177730 -

頻率合成器

+關注

關注

5文章

219瀏覽量

32336 -

無線電

+關注

關注

59文章

2132瀏覽量

116327

發布評論請先 登錄

相關推薦

什么是頻率合成器

怎么利用7GHZ頻率合成器實現IF調諧無線接收機?

TEA5757TEA5759自調諧無線電接收器STR相關資料推薦

利用7GHz頻率合成器實現高靈敏度IF調諧無線接收機

利用7GHZ頻率合成器實現快速鎖定、高靈敏度的IF調諧無線接收機

利用7GHZ頻率合成器實現快速鎖定、高靈敏度的IF調諧無線接收機

如何使用頻率合成器實現無線設備的靈敏度和可選擇性

【世說芯品】ADI公司低抖動頻率合成器支持GSPS數據轉換器方案實現優異性能

采用7GHz頻率合成器實現快速鎖定、高靈敏度調諧中頻無線電接收器

采用7GHz頻率合成器實現快速鎖定、高靈敏度調諧中頻無線電接收器

評論