芯片中的功耗

芯片的功耗可分為三大類。這些是:動態功率、短路損耗和泄漏功耗。下面將詳細討論這些類別及其組成部分。請注意,除非另有說明,以下描述僅適用于NMO——PMO也可以得到類似的解釋。“MOS”通常指MOSFET和CMOS。

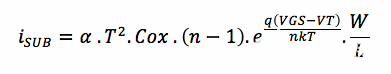

1.漏電功耗:如今,功耗的這一部分最受關注。并非所有泄漏消耗的成分都存在或主導四分之一微米及以上的節點,因此,它對總功耗的貢獻可以忽略不計。然而,隨著技術進步導致MOS的縮小,量子力學效應開始出現,并導致許多這些泄漏電流組件。這是能量耗散的分量,它在很大程度上影響了芯片在待機操作中的操作,因為其他元件在此期間會卡住發揮。因此,要在芯片中實現低功耗目標,必須尋找可能發揮作用的各種泄漏元件來源。泄漏消耗的主要來源如下:

弱反轉電流/次閾值電流:MOS的亞閾值區域是VG工作的區域≈VT和VDS》0(在nMOS環境中)。在該區域,電壓不足以為MOS開始導電構建完整的表面通道。然而,一些電子可能會獲得足夠的能量來從源頭穿越到漏極。此電流稱為亞閾值電流。該電流的近似值可以從下面的等式中理解:

圖1:各種漏電流

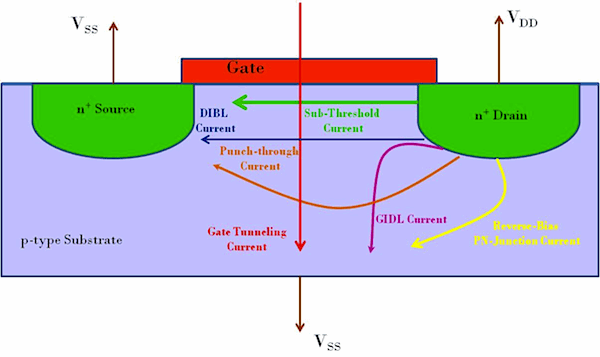

結反向偏置電流:在擴散區和基板邊界之間形成一些寄生二極管。這些寄生蟲傾向于將一些少數電流從漏極漂移到基質。此外,在耗盡區域中產生的一些電子 - 空穴對有助于電流流向基板。這種凈電流被稱為結反向偏置電流。這種電流與摻雜密度有直接關系,并且往往隨著摻雜的增加而增加。

圖2:反向偏置PN結電流

漏極誘導勢壘降低(DIBL):隨著漏極電壓的增加,它會影響發生局部電位積聚的漏極區域周圍的耗盡區域。這導致耗盡區域寬度的增加和排水區域周圍表面電位的增加。在長通道MOS中,源與漏極有一定距離,對源區域沒有太大影響。因此,源和通道之間的電位不會改變。然而,隨著技術節點的縮小,漏極和源極之間的距離減小。因此,由于漏極處的電壓,源區也開始受到影響。這導致耗盡寬度的增加和耗盡通道源側附近表面電位的增加。因此,對于給定的柵極電位,電位勢壘降低,更多的電子開始從源側移動到漏極側。這稱為排水誘導的障礙降低。這導致由于載波可用性的提高而導致關斷電流的增加。

穿孔電流:穿通電流是DIBL的一種極端形式。當漏極電壓超過一定水平時,耗盡區會延伸到阱中深處。結果,柵極電壓失去了對通過MOS的電流的控制,大量電流開始流過MOS。該電流與VDS(漏源極電壓)呈二次關系變化。這是決定MOS尺寸和氧化層厚度減小時工作電壓變化范圍的因素之一。隨著MOS縮小,源節點和漏節點之間的距離減小,因此,相同的VDS現在將在漏節點和源節點之間產生更大的電場。這種高電場可以誘導穿通電流。因此,隨著MOS尺寸的縮小,降低電源電壓變得至關重要。

柵極感應漏極泄漏(GIDL):假設漏極連接到電源,柵極連接到接地或負電源。這將導致在柵極下方的排水區域產生電場。此字段將在排水管中創建一個耗盡區域。這導致排水溝附近的場擁擠和高場效應開始發生,例如雪崩倍增和帶隧道。結果,少數載流子在閘門下方的排水管中排放。由于基底處于較低電位,因此在排水耗盡區域附近積聚的少數載流子被掃到基底。該電流稱為柵極誘導漏極漏電流。該電流受施加的電壓和柵極氧化物厚度的高度影響。

柵極隧穿電流:隨著我們將技術縮小到深亞微米級,柵極下氧化物的厚度也會減小。在當今的技術中,這是在1-2nm厚度的范圍內。大量摻雜的通道和超薄氧化層在氧化區域產生非常高的電銼,約為MV/cm。因此,電流載體可以通過氧化物區域隧道傳輸,從而產生柵極電流。施加的電壓量越大,載流子通過氧化層隧道的機會就越大。該電流不僅相當于柵極端子的泄漏電流,而且還會減少流經漏極的電流。這可能會妨礙設備的性能。為了應對這種電流,使用多硅柵極代替金屬柵極 。

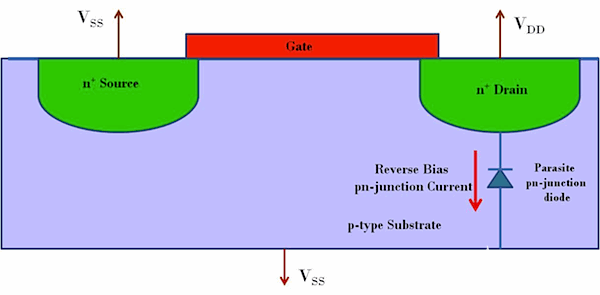

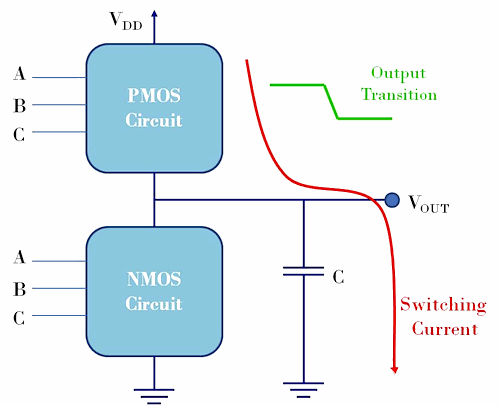

短路功耗:這是器件功耗的另一個組成部分。當電路輸入端發生邏輯變化時,它可能會改變其輸出狀態。在此轉換期間,某些MOS將從 OFF 狀態變為飽和狀態,而其他一些MOS將遵循相反的路徑。由于輸入在兩種邏輯狀態之間切換需要一些有限的時間,因此在此過渡階段,會出現一小段時間,其中NMOS和PMOS都在導電,并且它們都沒有處于OFF狀態。在此期間,一些電流流過它們,這被稱為短路電流。該電流不有助于任何內部電容器(結、互連和擴散電容)充電,因此會導致純功率損耗。

考慮輸入A的低到高轉換。當電平達到VTN時NMOS開始導通。此時,PMO仍處于導通狀態,直到輸入達到(VDD-|VTp |)水平,其中VTn和VTp分別是nMOS和PMO的閾值電壓。當NMO或PMO進入截止階段時,傳導停止,短路電流路徑中斷。類似的路徑也適用于輸入的下降過渡,即當nMOS仍在進行時,PMO被打開。如果輸入的上升和下降時間較高或負載電容較低,則該電流會變得相當大。為了抵消這種損失,輸入上升和下降的延遲會減少,輸出端的電容會增加。

圖3:CMOS逆變器中的短路電流

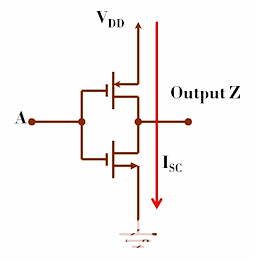

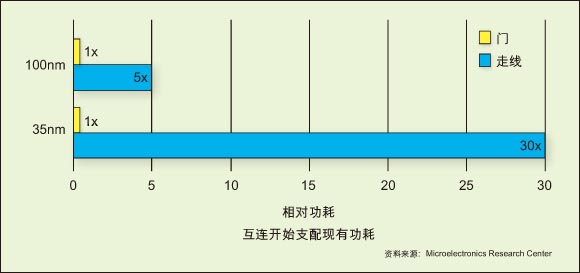

動態能耗:動態能耗是由于輸入中的切換而導致單元切換的消耗。因此,這也被稱為開關能量。當電池的狀態從邏輯高電平更改為邏輯低電平或反之亦然時,各種內部電容器(結電容、互連電容和擴散電容)會相應地充電或放電。從電源中汲取能量來為這些電容器充電,稱為動態功率。這種能耗曾經是泄漏電流微不足道的技術中四分之一節點(250μm)技術中最主要的消耗。然而,隨著技術的縮減,功能電流減小,漏電元件增加數倍。但是,我們盡一切努力將開關功耗降至最低,以降低應用的整體能耗。

圖4:CMOS電路中的開關電流

如果CMOS單元中的所有寄生電容都集中到負載電容中,那么,如果輸出電平從VDD變為接地,則總能耗為CVDD2。其中,一半的能量存儲在負載電容器中,其余一半的能量被耗散。同樣,當輸出改變回地面時,也會發生類似的能量耗散。因此,這種開關能耗與VDD和開關頻率直接相關。因此,降低電源電壓是降低動態功耗的一種方法。然而,VDD的減少會導致電池變慢,因此,有效地降低了操作的最大頻率。此外,頻率的降低會導致相同的操作需要更多的時間。平均開關能耗為::Pav= f·C·V2其中,f是操作頻率。該功耗完全獨立于輸入和輸出信號的上升和下降時間。

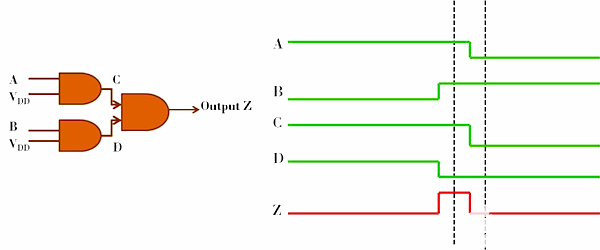

開關能耗的另一個組成部分是由于動態危險和毛刺引起的損失。由于進入或進入電路內部的各種輸入的路徑中的不平衡延遲,電路中可能會出現毛刺。考慮電路,如下所示。

圖5:故障產生、電路和時序圖

考慮兩個輸入在邏輯上的情況,如VDD所示,并且信號A和B的轉換具有一定的延遲,如相鄰時序圖中所示。由于A和B到達之間的延遲不平衡,輸出信號Z在短時間內被斷言為1。這種轉變被稱為小故障/危險。另一方面,如果A在斷言B之前下降,則輸出不會出現任何小故障,因為在斷言其他輸入之前,輸出和門的一個輸入會切換到零。因此,以這樣一種方式滿足時間要求,即消除或最小化此類故障。然而,在某些情況下,這種行為可能是有意停止電路中的競爭條件。為此,并非所有輸入都同時切換。在無法完全消除此類故障的情況下,可以在輸出端放置邏輯來吸收此類故障,以阻止其向以下邏輯的傳播,例如,在路徑中添加一些緩沖區來吸收此類故障,并平衡路徑的定時。

縱觀各種功耗源及其原因,隨著MOS擴展的推進,實現低功耗設計變得越來越具有挑戰性。當我們跨越技術節點時,新的參與者開始在這個舞臺上扮演關鍵角色,為這個低功耗的故事帶來了新的轉折。我們的下一篇文章將討論實現低功耗設計所采用的各種步驟和方法。并非所有這些方法都可以用于特定設計;但是,人們可能必須走鋼絲才能平衡功率與性能。

來源:中深源科技

審核編輯 :李倩

-

電流

+關注

關注

40文章

6765瀏覽量

131909 -

MOS

+關注

關注

32文章

1248瀏覽量

93514 -

IC芯片

+關注

關注

8文章

246瀏覽量

26197

發布評論請先 登錄

相關推薦

電磁爐常用IC芯片中文英文資料

如何控制IC的功耗

什么是ic設計 ic設計和芯片設計區別

芯知識 | 語音芯片中的聲音播放提示IC內置看門狗的作用介紹

IC芯片中的功耗

IC芯片中的功耗

評論