內(nèi)存帶寬是當(dāng)下阻礙某些應(yīng)用程序性能的亟需解決的問題,現(xiàn)在你可以通過地選擇芯片來調(diào)整 CPU 內(nèi)核與內(nèi)存帶寬的比率,并且您可以依靠芯片制造商和系統(tǒng)構(gòu)建商進(jìn)一步推動它。

如果 CPU 在內(nèi)存帶寬和某些情況下的內(nèi)存容量方面不受限制,那么考慮一下 HPC 和 AI 計算會是什么樣子是很有趣的。或者更準(zhǔn)確地說,如果內(nèi)存相對于計算而言不是那么昂貴。或許,我們可以對前者做點什么,我們會臉色發(fā)青,也許會死于等待對后者發(fā)生的事情,正如我們上周簡要談到的那樣。

有時候,你所能做的就是做一個止血帶,即使你不能立即永久性地解決手頭的問題,也要試著繼續(xù)運動。或者腳,或者傷口所在的地方。這讓我們思考,現(xiàn)在的服務(wù)器購買者如何通過服務(wù)器CPU和系統(tǒng)制造商的一些適度調(diào)整,至少可以使每個核心的內(nèi)存帶寬更加平衡。

正如去年的圖靈獎得主、行業(yè)名人Jack Dongarra在主題演講中恰當(dāng)?shù)刂赋龅哪菢樱瑤资陙恚闆r一年比一年糟糕。

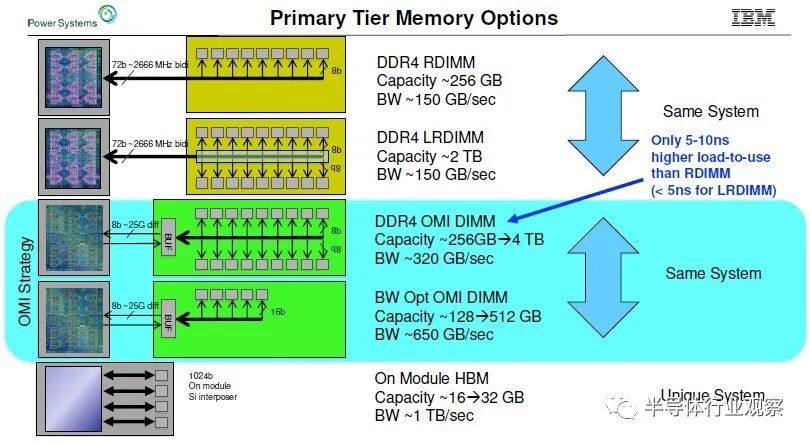

我們考慮這個問題已經(jīng)有一段時間了,早在 2019 年 8 月,IBM 就對 Power10 處理器進(jìn)行了預(yù)覽,并且預(yù)期(但從未交付過)高帶寬 Power9'——這是 Power9 “prime”,而不是打字錯誤——系統(tǒng)藍(lán)色巨人在 2019 年 10 月與我們談到了我們對具有高內(nèi)存帶寬的系統(tǒng)的興趣。(我們稱它為 Power E955,這樣它就有了一個名字,盡管它從未推出過。)IBM 展示了它的 OpenCAPI 內(nèi)存接口 (OMI) 以及它隨 Power10 機器一起提供的內(nèi)存,但這張圖表概括了 IBM 的內(nèi)容相信它可以在各種技術(shù)的電源芯片插座上做:

IBM 的 OMI 差分 DDR 內(nèi)存,它使用串行接口和 SerDes,本質(zhì)上與處理器上用于 NUMA、NVLink 和 OpenCAPI 端口的“Bluelink”信號相同,與普通的并行 DDR4 接口有很大不同,具體DDR 協(xié)議,無論是 DDR4 還是 DDR5,都位于存儲卡上的緩沖芯片上,而從存儲卡到 CPU 的接口是一種更通用的 OMI 協(xié)議。

這種早在 2019 年就在開發(fā)中的 OMI 內(nèi)存提供了大約 320 GB/秒的每個插槽和從 256 GB 到 4 TB 的每個插槽的容量。通過帶寬優(yōu)化版本,將內(nèi)存模塊數(shù)量減少四分之一,并為每個插槽提供 128 GB 至 512 GB 的 DDR4 容量,IBM 可以將 Power9 芯片上的內(nèi)存帶寬提高到 650 GB/秒,并且借助預(yù)計在 2021 年推出的 Power10 服務(wù)器,它可以使用時鐘速度更快的 DDR5 內(nèi)存將速度提高到 800 GB/秒。

同時,對于預(yù)計在 2020 年交付的 Power9 系統(tǒng),IBM 估計如果它使用 HBM2 堆疊內(nèi)存,它可以提供 16 GB 到 32 GB 的容量,并提供大約 1 TB/秒的每個插槽帶寬。這是每個插槽的大量內(nèi)存帶寬,但內(nèi)存容量并不是很大。

無論出于何種原因——我們認(rèn)為無論它們是什么,它們都不是好產(chǎn)品,但這可能與藍(lán)色巨人與當(dāng)時的代工合作伙伴 Globalfoundries 的技術(shù)和法律困難有關(guān)——Power9 系統(tǒng),很可能是四路機器每個插座中都帶有雙芯片模塊,從未面世。

但早在 2022 年 7 月,“帶寬野獸”的想法就被重新命名為 Power E1050,作為 Power10 中端系統(tǒng)陣容的一部分。

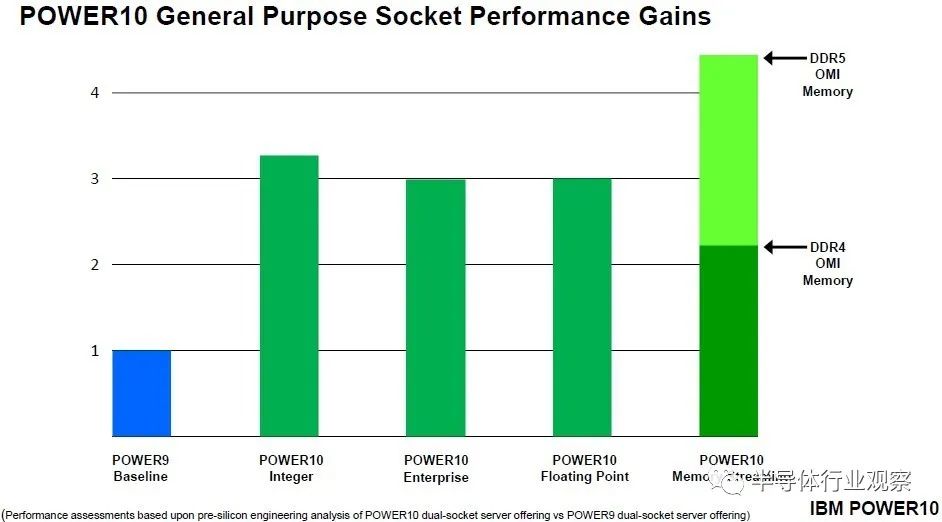

當(dāng)“Cirrus”Power10 處理器規(guī)格于 2020 年 8 月公布時,IBM 表示該芯片每個內(nèi)核的峰值內(nèi)存帶寬為 256 GB/秒,每個內(nèi)核的持續(xù)內(nèi)存帶寬為 120 GB/秒。Power10 芯片上有 16 個內(nèi)核,但為了在 IBM 的新代工合作伙伴三星的 7 納米工藝上獲得更好的產(chǎn)量,最多只有 15 個內(nèi)核處于活動狀態(tài)。關(guān)于去年 7 月推出的入門級和中端 Power10 機器、4、8、10 和 12 核在 SKU 堆棧中可用,而 15 核變體僅在可擴(kuò)展到 16 插槽的高端“Denali”Power E1080 系統(tǒng)中可用。目前尚不清楚這些峰值和持續(xù)內(nèi)存帶寬數(shù)據(jù)是否適用于 DDR5 內(nèi)存,但我們懷疑是這樣。IBM 確實交付了使用基于 DDR4 內(nèi)存的 OMI 內(nèi)存的 Power E1050(和其他 Power10 機器),并在其演示中表示配備 DDR5 內(nèi)存的 Power10 的內(nèi)存流性能將是 DDR4 內(nèi)存的 2 倍。

以上比較針對的是單芯片 Power10 模塊。對于雙芯片模塊,將它們加倍,然后針對保持在與單芯片模塊相同的熱包絡(luò)內(nèi)所需的降檔時鐘速度進(jìn)行調(diào)整。

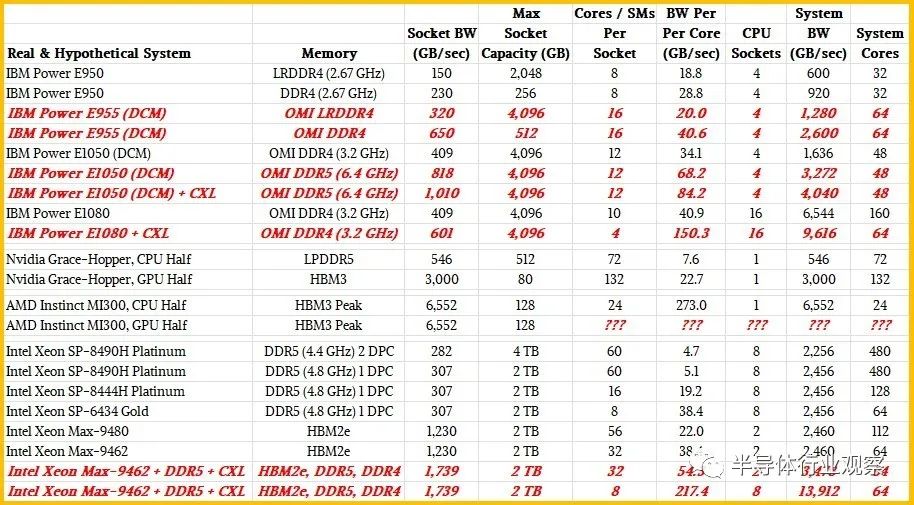

采用 Power E1050 機器,服務(wù)器最多有四個 Power10 DCM,總共有 96 個核心。這八個小芯片共有八個 OMI 內(nèi)存控制器,支持多達(dá) 64 個差分 DIMM,DDR4 內(nèi)存運行頻率為 3.2 GHz,并在內(nèi)核之間提供 1.6 TB/秒的總帶寬。也就是說,在系統(tǒng)中 96 個核心的峰值時,每個 Power10 核心的內(nèi)存帶寬為 17 GB/秒。

首先,讓我們回到核心技術(shù)。Power E1050的臃腫配置使用了12核Power10芯片,但有一款48核的改型只使用了6核芯片。(是的,Power10內(nèi)核的成品率只有37.5%。)這使得每核帶寬翻了一番,達(dá)到34 GB/秒。如果你改用運行在6.4 GHz的DDR5內(nèi)存,這是昂貴的,而且價格并不合理,那么你可以獲得每核高達(dá)68 GB/秒的內(nèi)存帶寬。

現(xiàn)在,理論上,如果CXL內(nèi)存擴(kuò)展器可用,您可以進(jìn)一步推動這個真正的Power E1050,您可以在CXL內(nèi)存上的每個插槽消耗PCI-Express 5.0帶寬的56個通道中的48個,添加6個x8 CXL內(nèi)存擴(kuò)展器,每個擴(kuò)展器以32 GB/秒的速度產(chǎn)生另外192 GB/秒的內(nèi)存帶寬(當(dāng)然,還有一些附加延遲)。這使得你的總帶寬達(dá)到1.8 TB/秒,每核帶寬達(dá)到38 GB/秒。如果IBM使每個Power10芯片上的內(nèi)核數(shù)更小,那么每個內(nèi)核的內(nèi)存帶寬就可以調(diào)高。如果每個芯片有4個內(nèi)核,每個系統(tǒng)有32個內(nèi)核,那么每個內(nèi)核的內(nèi)存帶寬最高可達(dá)57.1 GB/秒。轉(zhuǎn)到DDR5內(nèi)存+ CXL內(nèi)存,每個核心可以達(dá)到84 GB/秒。

01進(jìn)入混合計算引擎

請注意,沒有人說這很便宜。但對于某些工作負(fù)載,這可能是一個比將代碼移植到GPU或等待CPU-GPU混合計算引擎(AMD的Instinct MI300A, Nvidia的Grace-Hopper, Intel的Falcon Shores)上市更好的答案。雖然這些處理器每個核心都有很高的內(nèi)存帶寬,但內(nèi)存容量將受到限制,因此比IBM Power10和英特爾“Sapphire Rapids”Max系列CPU(混合HBM 2e/DDR5內(nèi)存)的性能要有限得多。

英偉達(dá)Grace芯片擁有72個核心和16組LPDDR5內(nèi)存,總?cè)萘繛?12 GB,每個插槽的內(nèi)存為546 GB/秒。計算出來每個核的內(nèi)存帶寬為7.6 GB/秒。Hopper GPU擁有132個流多處理器(相當(dāng)于CPU的核心),其HBM3堆疊內(nèi)存的帶寬最高可達(dá)3000 GB/秒。(在H100加速器上,有5個堆棧產(chǎn)出80gb。)計算出來,每個GPU“核心”的帶寬為22.7 GB/秒,這只是給你一個參考框架。如果您將Grace上的所有LPDDR5內(nèi)存視為一種類似cxl的內(nèi)存,則可以將CPU-GPU復(fù)合物的內(nèi)存容量提高到總共592 GB,并將聚合內(nèi)存帶寬提高到3,536 GB/秒。根據(jù)您的意愿在該綜合體中分配核心和SMs。您可以將GPU視為CPU核心的非常昂貴的快速內(nèi)存加速器,計算出每個Grace核心的內(nèi)存帶寬為49.3 GB/秒,每個Hopper SM的內(nèi)存帶寬為26.9 GB/秒。

上面提到的Power10系統(tǒng)就在這個范圍內(nèi),沒有太多的工程方法。

對于AMD Instinct MI300A,我們知道它有128 GB的HBM3堆疊內(nèi)存,分布在8個組、6個GPU和2個12核Epyc 9004 CPU芯片上,但我們不知道帶寬,也不知道MI300A包上的6個GPU芯片集合上的短信數(shù)量。我們可以對帶寬做一個有根據(jù)的猜測。HBM3以每引腳6.4 Gb/秒的速度運行信令,最多可達(dá)16個通道。根據(jù)堆疊的DRAM芯片數(shù)量(從4個到16個)和它們的容量(每個堆棧從4 GB到64 GB),您可以獲得不同的容量和帶寬。

使用16 Gb DRAM,最初的HBM3堆棧預(yù)計每個堆棧提供819 Gb /秒的帶寬。看起來AMD可能會使用8個16gb芯片堆棧,每個堆棧有8個芯片,這將提供128 Gb的容量,并將產(chǎn)生6552 Gb /秒的總帶寬,以去年4月HBM3規(guī)范宣布時的預(yù)期速度。我們認(rèn)為MI300A封裝上的Epyc 9004芯片有16個內(nèi)核,但其中只有12個用于提高產(chǎn)量和可能的時鐘速度,當(dāng)這些Epyc內(nèi)核達(dá)到HBM3內(nèi)存時,每個內(nèi)核的內(nèi)存帶寬將達(dá)到驚人的273 GB/秒。

很難說這六個GPU芯片上有多少短信,但與之前的AMD和Nvidia GPU加速器相比,每條短信的帶寬可能會非常高。但是,同樣,每個計算引擎的總內(nèi)存為128 GB并不是很大的容量。

而且,為了抑制我們的熱情,由于熱的原因,AMD可能不得不削減DRAM堆棧和/或HBM3內(nèi)存速度,因此可能達(dá)不到我們預(yù)期的帶寬數(shù)字。即使是每個CPU核心帶寬的一半,這也會令人印象深刻。同樣,對于只使用cpu的應(yīng)用程序,GPU是一個非常昂貴的附加組件。

任何CXL內(nèi)存可能掛在這個處理器上以增加額外的容量,這將在這方面有所幫助,但不會對每個核心或SM的帶寬增加太多。

我們對未來的英特爾獵鷹海岸CPU-GPU混合處理器的了解還不夠多,根本無法進(jìn)行任何計算。

02在CPU和NUMA拯救HBM嗎?

這讓我們想到了英特爾的藍(lán)寶石Rapids與HBM2e內(nèi)存,它也有一種模式,同時支持HBM2e和DDR5內(nèi)存。我們之所以對Sapphire Rapids感興趣,不僅是因為它在某些變體中支持HBM2e堆疊內(nèi)存,還因為它在其他變體中也具有八路NUMA可伸縮性。

我們認(rèn)為可以允許創(chuàng)建一個八路,hbm功能的系統(tǒng),同時使用DDR5和CXL主存。讓我們從頭開始,從普通的Sapphire Rapids Xeon SP CPU開始。

據(jù)我們所能估計,Sapphire Rapids Xeon SP上的8個DDR5內(nèi)存通道可以在一個插座上提供略高于307 GB/秒的內(nèi)存帶寬。如果每個通道有一個DIMM,運行頻率為4.8 GHz,則最大容量為2tb。使用每個通道兩個內(nèi)存,每個插槽的容量可以翻倍,達(dá)到4 TB,但運行速度較慢的4.4 GHz,每個插槽只能產(chǎn)生282 GB/秒的內(nèi)存帶寬。(后一種情況是內(nèi)存容量大,而不是內(nèi)存帶寬大。)在Xeon SP-8490H上,每個通道有一個內(nèi)存,60個內(nèi)核運行在1.9 GHz,計算出來每個內(nèi)核的帶寬只有5.1 GB/秒。如果你使用Xeon SP-8444H處理器,它只有16個核心,但運行在更高的2.9 GHz,所以你可以恢復(fù)掉核時失去的一些性能,每個核心的帶寬為19.2 GB/秒。

好吧,如果你想提高插座上每個核心的內(nèi)存帶寬,你可以切換到Xeon SP-6434,它有8個內(nèi)核,運行頻率為3.7 GHz。在4.8 GHz DDR5速度下,每核帶寬將增加一倍,達(dá)到38.4 GB/秒。這個處理器上活動的UPI鏈路少了一個,因此雙插座服務(wù)器上的耦合效率會低一些,而且延遲和帶寬也會低一些。這與使用3.2 GHz DDR4內(nèi)存的六核Power10芯片大致相同,類似于Grace Arm服務(wù)器CPU上的每個核從其本地LPDDR5內(nèi)存中看到的情況。

現(xiàn)在,讓我們談?wù)勊{(lán)寶石急流HBM變體。頂部的bin Max系列CPU有56個核,四個HBM2e堆棧有64gb的容量和1230gb /秒的總帶寬。計算出來,每個核的內(nèi)存帶寬為22 GB/秒。低倉部分有32個核,相同的1230 GB/秒內(nèi)存,或每個核38 GB/秒。如果在插座上添加DDR5內(nèi)存,則可以再增加307 GB/秒,如果添加CXL內(nèi)存擴(kuò)展器,則可以再增加192 GB/秒。所以現(xiàn)在32個核心的內(nèi)存總量達(dá)到了1729 GB/秒,也就是54 GB/秒。

現(xiàn)在,讓我們將其發(fā)揮到極致,利用NUMA互連將8個Sapphire Rapids HBM插座(英特爾不允許這樣做)連接在一起,并將每個插座在4 GHz下運行的內(nèi)核數(shù)降至8個內(nèi)核。這將產(chǎn)生64個運行頻率為4 GHz的內(nèi)核,比藍(lán)寶石Rapids 60核至強SP-8490H更具魅力。但是現(xiàn)在,將HBM、DDR5和CXL內(nèi)存全部添加進(jìn)來后,這8個插槽的內(nèi)存帶寬總計為13,912 GB/秒,每個核的總帶寬為217.4 GB/秒。

我們確信,這不會是一個便宜的盒子。但話說回來,Power E1050也不是。

如果IBM將Power E1080的核心撥下來,并添加CXL擴(kuò)展器,它可以通過16個插槽獲得一些東西,這將是連接到這16個插槽的OMI內(nèi)存的6544 GB/秒,再加上PCI-Express 5.0總線上的6個CXL內(nèi)存模塊的3,072 GB/秒,總共9,616 GB/秒。你想要多少核?每個Power10 SCM有4個內(nèi)核,即64個內(nèi)核,計算出來每個內(nèi)核的主存帶寬為150 GB/秒。

關(guān)鍵是,有一種方法可以構(gòu)建專注于每個核心更好的內(nèi)存帶寬的服務(wù)器節(jié)點,因此適合加速某些類型的HPC和分析工作負(fù)載,甚至可能是部分AI訓(xùn)練工作負(fù)載。你的計算能力會比內(nèi)存容量或內(nèi)存帶寬的限制更大,你必須非常小心,不要因為沒有足夠的內(nèi)核從內(nèi)存中提取數(shù)據(jù)和向內(nèi)存中插入數(shù)據(jù)而使昂貴的內(nèi)存負(fù)擔(dān)過重。

順便說一下,我們不太確定這種帶寬野獸方法如何加速人工智能訓(xùn)練——也許只在預(yù)訓(xùn)練的模型上進(jìn)行修剪和調(diào)整。我們有一種預(yù)感,即使是GPU在GPU核心時延和附加的HBM2e和HBM3堆疊內(nèi)存帶寬之間也存在不平衡,因此它們無法在接近峰值計算效率的任何地方運行。

我們充分認(rèn)識到,這一切都不便宜。但GPU加速的機器也不是。但是,對于某些工作負(fù)載來說,更好地平衡計算、內(nèi)存帶寬和內(nèi)存容量可能比將內(nèi)存分割成碎片并將數(shù)據(jù)集分散到幾十個CPU上更好。不可否認(rèn),您確實需要以不同的方式加速這些工作負(fù)載——并跨內(nèi)存層次結(jié)構(gòu)對它們進(jìn)行編程——以突破極限。

這就是思想實驗的作用。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19160瀏覽量

229121 -

IBM

+關(guān)注

關(guān)注

3文章

1749瀏覽量

74626 -

DDR

+關(guān)注

關(guān)注

11文章

711瀏覽量

65228 -

HPC

+關(guān)注

關(guān)注

0文章

311瀏覽量

23684 -

電源芯片

+關(guān)注

關(guān)注

42文章

1078瀏覽量

76925

原文標(biāo)題:內(nèi)存帶寬瓶頸如何破?IBM的方法!

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

HBM4需求激增,英偉達(dá)與SK海力士攜手加速高帶寬內(nèi)存技術(shù)革新

前端總線與內(nèi)存頻率怎么配

三星電子突破瓶頸,HBM3e內(nèi)存芯片獲英偉達(dá)質(zhì)量認(rèn)證

成都匯陽投資關(guān)于跨越帶寬增長極限,HBM 賦能AI新紀(jì)元

集成32GB HBM2e內(nèi)存,AMD Alveo V80加速卡助力傳感器處理、存儲壓縮等

NuLink PHY技術(shù):突破計算芯片內(nèi)存瓶頸

英偉達(dá)H200帶寬狂飆

美光科技開始量產(chǎn)HBM3E高帶寬內(nèi)存解決方案

人工智能與機器學(xué)習(xí)計算中的內(nèi)存挑戰(zhàn)

新型內(nèi)存技術(shù)助力存儲網(wǎng)絡(luò)變革,將替代DRAM

SK海力士加大高帶寬內(nèi)存生產(chǎn)投入

示波器帶寬與探頭帶寬的關(guān)系揭秘

DDR6和DDR5內(nèi)存的區(qū)別有多大?怎么選擇更好?

深度解析HBM內(nèi)存技術(shù)

內(nèi)存帶寬瓶頸如何破?

內(nèi)存帶寬瓶頸如何破?

評論