之前介紹了用ModlSim獨立仿真帶ISE IP核的仿真工程,本次介紹用ModelSim獨立仿真帶Vivado IP核的仿真工程。整體步驟基本一樣,只是do文件分成了兩個文件。使用工具Vivado2017.2 && Modelsim 10.5。

操作步驟

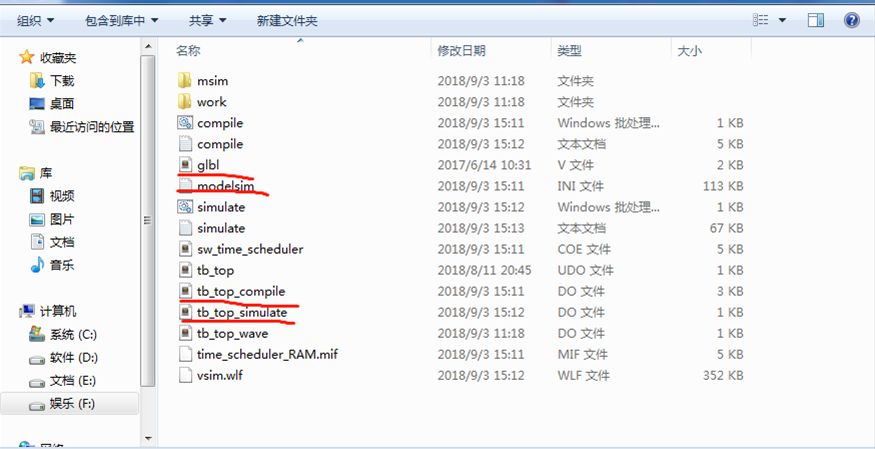

1、找到Vivado調用Modelsim仿真時自動產生的仿真文件,如下圖紅線所示。

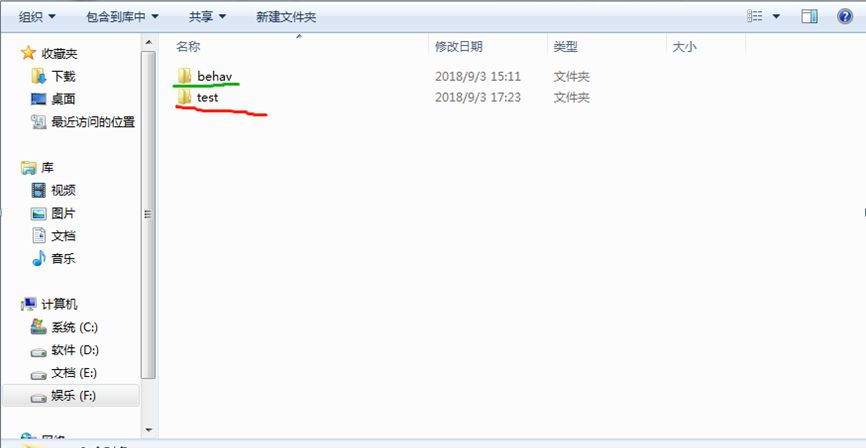

2、在behave文件夾同級路徑下新建立一個文件夾,本實例中為test。

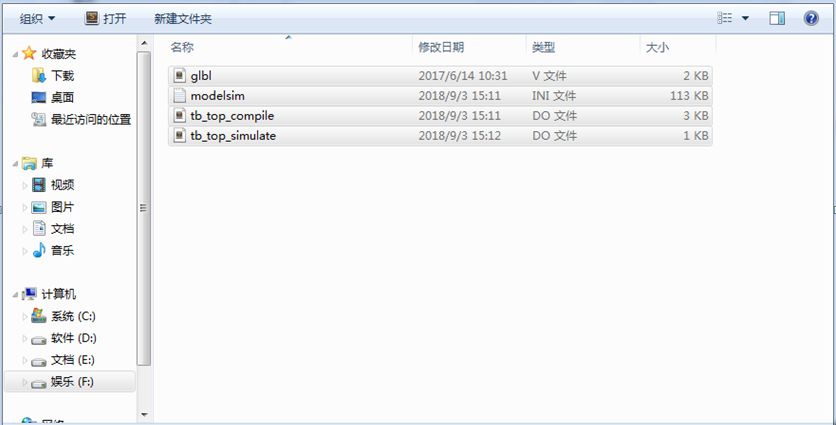

3、將所需的仿真文件復制到新文件夾中。

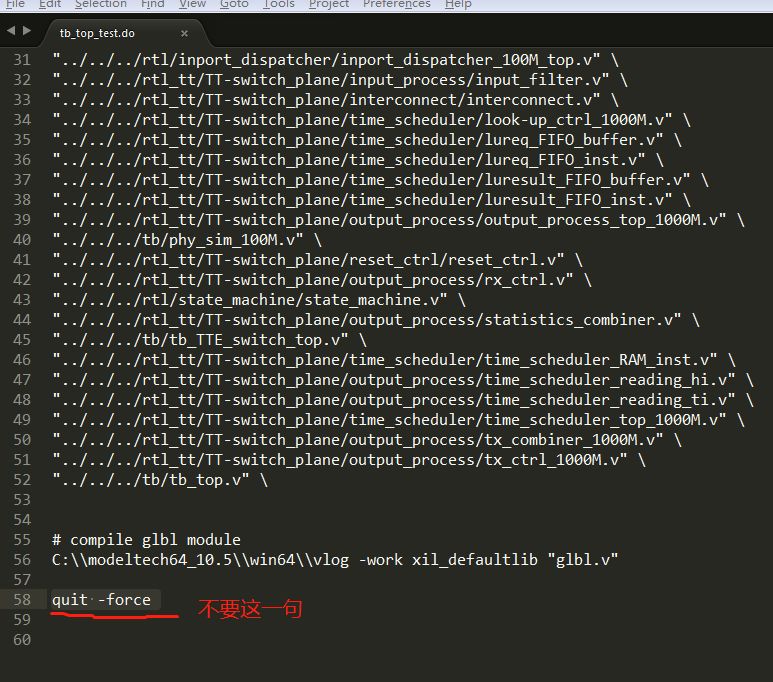

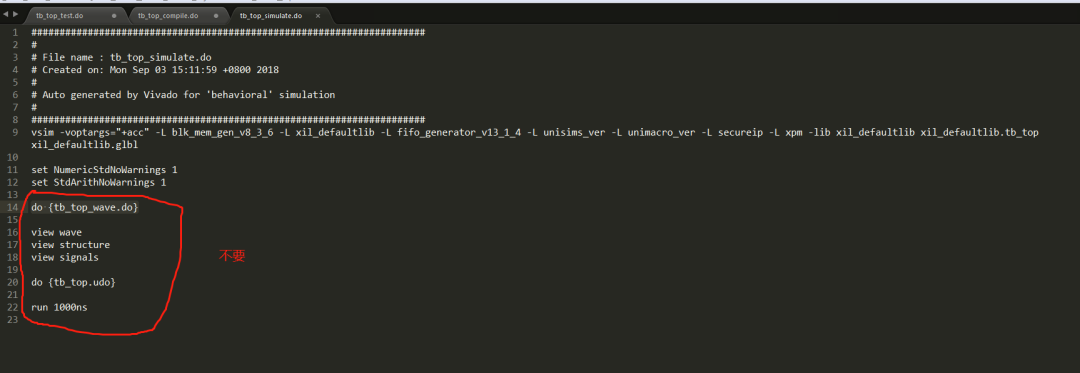

4、將兩個.do文件的內容合并成一個文件。

我采取的辦法是新建一個.do文件,即tb_top_test.do,然后用sublime打開tb_top_compile.do,將除quit –force語句的其他所有內容復制進tb_top_test.do,然后用sublime打開tb_top_simulate.do,將除do {tb_top_wave.do}和接下來的語句的其他所有內容復制進tb_top_test.do,然后保存tb_top_test.do。

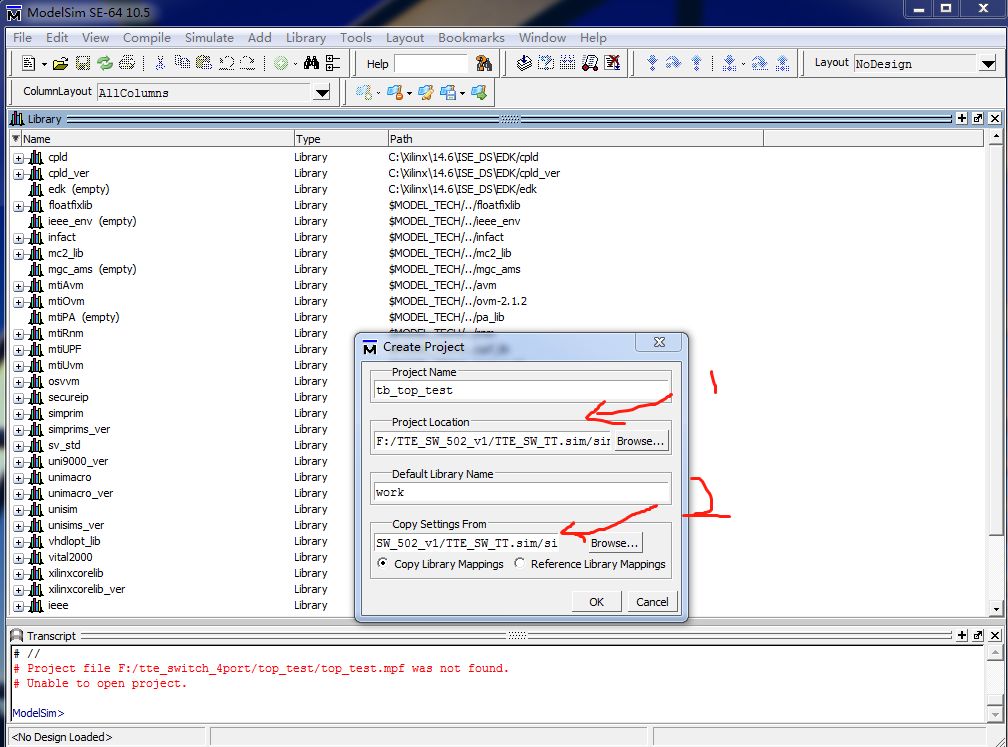

5、打開modelsim,新建工程,在Project_location選步驟3新建的文件夾,Copy_SettingsFrom選擇該文件夾下的modelsim.ini文件,然后點擊OK.

6、點擊close

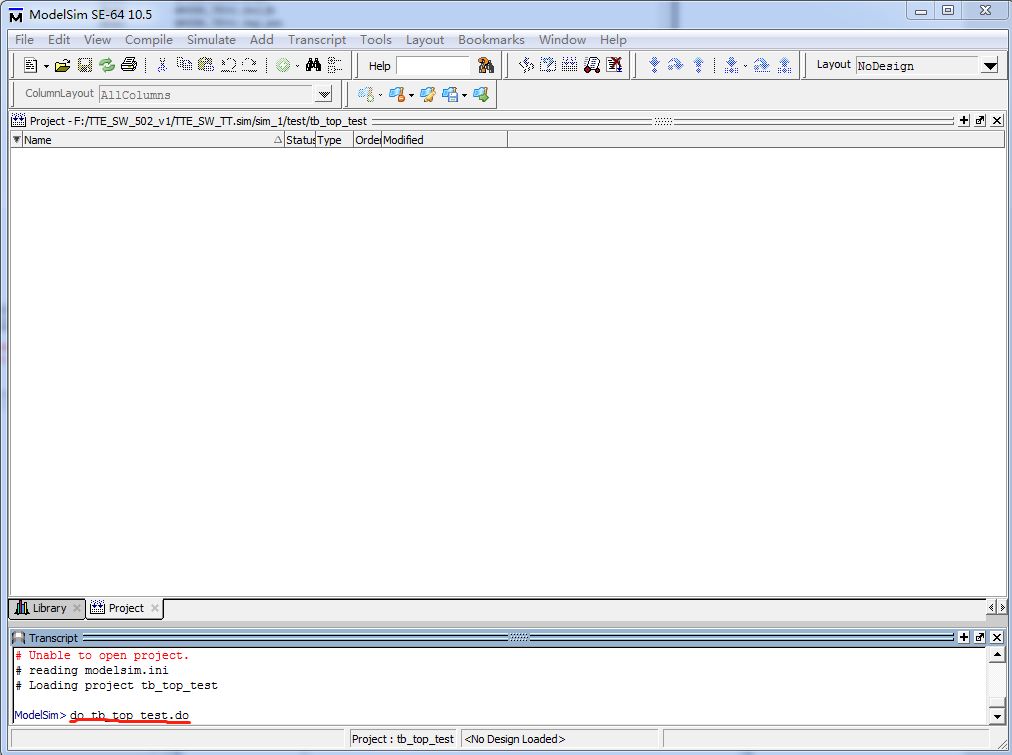

7、運行步驟4所生成的.do文件

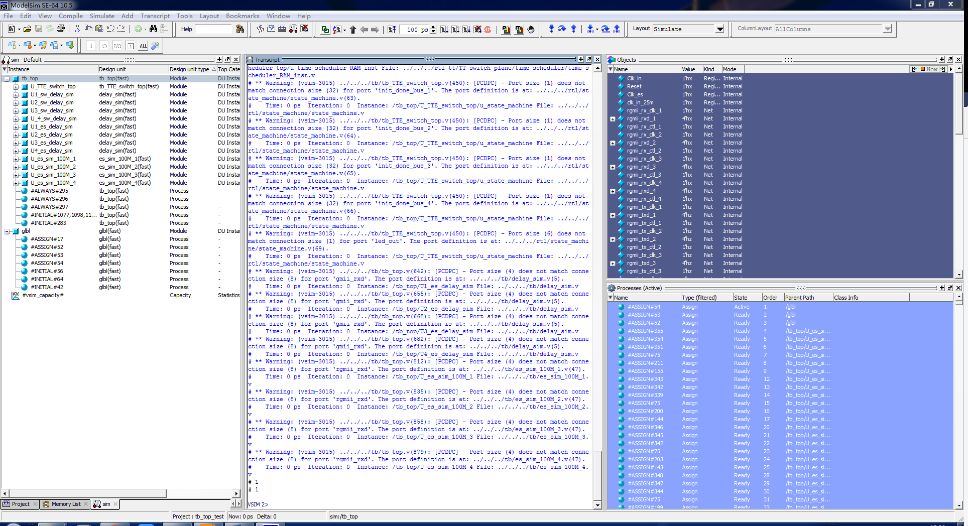

8、運行后會出現下圖所示的界面,將信號添加進波形圖。

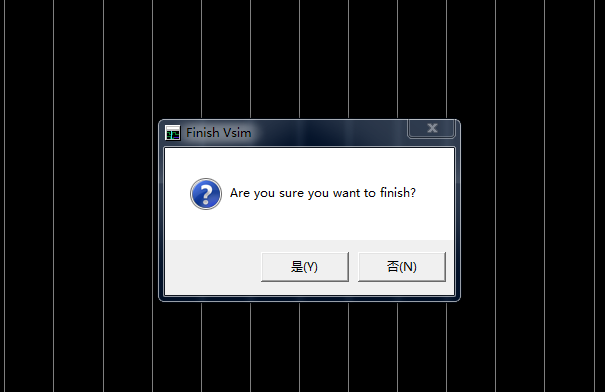

9、在波形界面進行仿真,第一次運行出現下圖所示界面,點擊否(這個界面可能多次彈出,點否就行了)。

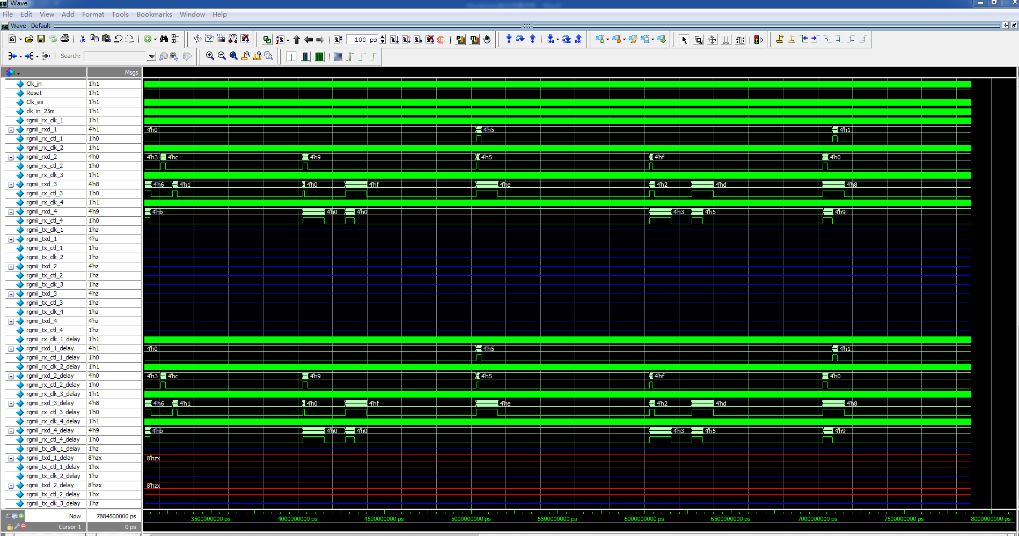

10、再進行仿真,即可得到波形圖

審核編輯:劉清

-

ModelSim

+關注

關注

5文章

174瀏覽量

47122 -

Vivado

+關注

關注

19文章

808瀏覽量

66324

原文標題:用Modelsim獨立仿真帶Vivado IP核的仿真工程

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何用Python實現Vivado和ModelSim仿真自動化?

modelsim 仿真 altera IP核(ROM,RAM實例

基于vivado平臺和modelsim的仿真和應用測試

VCS獨立仿真Vivado IP核的一些方法總結

淺析modelsim 自動化 高效獨立仿真含vivado IP核的工程

Vivado與ModelSim的聯合仿真操作

使用VCS仿真Vivado IP核時遇到的問題及解決方案

VCS獨立仿真Vivado IP核的一些方法總結

介紹用ModelSim獨立仿真帶Vivado IP核的仿真方案

介紹用ModelSim獨立仿真帶Vivado IP核的仿真方案

評論