1 運(yùn)行平臺

硬件:CXD301數(shù)字信號處理板

系統(tǒng):win7/64;win7/32;win10/64

軟件:ISE/ModelSimSE/Verilog/Matlab

2 主要功能及性能指標(biāo)

3.2.1主要功能

1)產(chǎn)生基帶原始數(shù)據(jù)

2)幀同步信號提取

3.2.2主要性能指標(biāo)

1) 發(fā)送端

系統(tǒng)時(shí)鐘:50MHz

基帶數(shù)據(jù)碼率:195.3125kbps

數(shù)據(jù)內(nèi)容:幀長16位,幀同步字長7位,同步字為1011000

2) 接收端

系統(tǒng)時(shí)鐘:發(fā)送端送來的數(shù)據(jù)時(shí)或信號,195.3125kbps

同步方式:具有搜索、校驗(yàn)、同步三種狀態(tài):幀長、幀同步字、搜索容錯(cuò)位數(shù)、校核容錯(cuò)位數(shù)、同步容錯(cuò)位數(shù)可通過修改程序參數(shù)快速設(shè)置。

3 程序結(jié)構(gòu)框圖說明

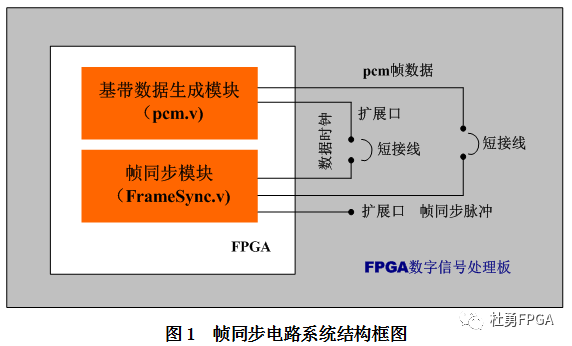

幀同步電路系統(tǒng)主要由基帶數(shù)據(jù)生成模塊(pcm.v)、幀同步模塊(FrameSync.v)模塊組成。

基帶數(shù)據(jù)生成模塊生成的原始數(shù)據(jù)(1.5625Mbps)送至開發(fā)板上擴(kuò)展口,經(jīng)短接線由第35腳送回FPGA芯片;數(shù)據(jù)生成的同步時(shí)鐘信號也經(jīng)擴(kuò)展口硬件環(huán)回至幀同步模塊。為便于測試環(huán)路同步及失步狀態(tài),輸入端設(shè)計(jì)了一個(gè)數(shù)據(jù)選擇控制邏輯,通過按鍵控制輸入數(shù)據(jù)。

審核編輯:劉清

-

數(shù)字信號處理

+關(guān)注

關(guān)注

15文章

557瀏覽量

45795 -

FPGA芯片

+關(guān)注

關(guān)注

3文章

246瀏覽量

39780 -

按鍵控制器

+關(guān)注

關(guān)注

0文章

8瀏覽量

6415

發(fā)布評論請先 登錄

相關(guān)推薦

插值法幀同步ISE/Verilog/CXD301介紹

插值法幀同步ISE/Verilog/CXD301介紹

評論