作者:Roger Zemke and Hassan Malik

LTC?1450 和 LTC1450L 是完整的單電源軌至軌電壓輸出、12 位 DAC,采用 24 引腳 SSOP 和 PDIP 封裝。它們包括一個輸出緩沖放大器、一個基準(zhǔn)和一個雙緩沖并行數(shù)字接口。這些DAC采用專有架構(gòu),保證最大DNL誤差為0.5LSB。內(nèi)置上電復(fù)位功能可確保DAC的輸出初始化為零電平。

軌到軌緩沖輸出可供應(yīng)或吸收 5mA 電流,同時拉至正電源電壓或地的 300mV 以內(nèi)。空載時,輸出擺幅在任一電源軌的幾毫伏以內(nèi),當(dāng)驅(qū)動負載至供電軌時,輸出擺幅為40Ω。

低功耗、5V 或 3V 單電源供電

LTC1450 僅從一個 400.4V 至 5.5V 電源吸收 5μA 電流。DAC可配置為0V至4.095V或0V至2.048V輸出范圍。它有一個 2.048V 內(nèi)部基準(zhǔn)。

LTC1450L 采用一個 250.2V 至 7.5V 電源吸收 5μA 電流。該器件可配置為 0V 至 2.5V 或 0V 至 1.22V 輸出范圍。它具有一個 1.22V 內(nèi)部基準(zhǔn)。

獨立性能的靈活性

LTC?1450 / LTC1450L 是完全獨立的 DAC,無需外部組件。基準(zhǔn)輸出、基準(zhǔn)輸入和增益設(shè)置引腳為用戶提供了更大的靈活性。

圖1顯示了這些DAC通常如何使用。REF HI 與 REF OUT 相關(guān)聯(lián),REF LO 和 X1/X2 接地。

圖 1a. 字節(jié)/并行輸入、內(nèi)部/外部基準(zhǔn)、上電復(fù)位和增益選擇提供了應(yīng)用靈活性。

圖 1b.專利架構(gòu)保證了出色的 DNL。

四象限乘法DAC應(yīng)用

圖 2 示出了配置為單電源 1450 象限乘法 DAC 的 LTC4L。它使用一個 5V 電源,僅使用一個外部元件,即一個從 REF OUT 接地的 5k 電阻。(LTC1450 可以以類似的方式使用。

圖2.內(nèi)部基準(zhǔn)、REF LO/REF HI 引腳、增益調(diào)整和寬電源電壓范圍允許采用 4V 單電源進行 5 象限乘法。

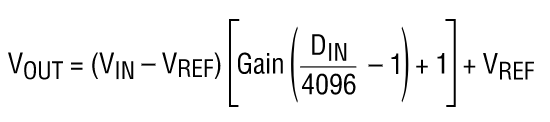

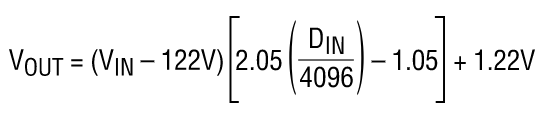

乘法DAC允許用戶以數(shù)字方式改變交流輸入信號的幅度和極性,其電壓以1.22V基準(zhǔn)電壓提供的失調(diào)信號地為中心。傳遞函數(shù)如下式所示。

對于 LTC1450L 增益 = 2.05 和 V裁判= 1.22V

表 1 顯示了 VOUT 與 VIN、VREF 和 DIN 的函數(shù)關(guān)系的表達式。圖3顯示了一個12.5kHz、2.3VP-Ptriangle波輸入信號以及零電平和滿量程DAC代碼的相應(yīng)輸出波形。

| DAC寄存器中的二進制數(shù)字輸出代碼 | 模擬輸出 (V外) | ||

| MSB | 低音水平 | ||

|

1111 |

1111 | 1111 |

(4094/4096)(五在– V裁判) + V裁判 |

|

1100 |

0001 | 1001 |

0.5(V在– V裁判) + V裁判 |

|

1000 |

0011 | 0010 |

V裁判 |

|

0100 |

0100 | 1011 |

–0.5(V在– V裁判) + V裁判 |

| 0000 | 0110 | 0110 | –1.0(V在– V裁判) + V裁判 |

| 0000 | 0000 | 0000 | –1.05(V在– V裁判) + V裁判 |

圖3.零電平和滿量程DAC設(shè)置的輸出波形中顯示了干凈的四象限乘法。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

184文章

17215瀏覽量

247826 -

放大器

+關(guān)注

關(guān)注

143文章

13437瀏覽量

212216 -

dac

+關(guān)注

關(guān)注

43文章

2227瀏覽量

190446

發(fā)布評論請先 登錄

相關(guān)推薦

具有軌到軌輸出的四路4.5ns單電源3V/5V比較器

MAX5232, MAX5233 3V/5V、10位、串行電

AD5380:40通道、3V/5V單電源、14位電壓輸出DAC 數(shù)據(jù)手冊

AD5383:32頻道,3V/5 V,單片機,12位,能/DAC數(shù)據(jù)Sheet

AD7715:3V/5V,450微A,16位Sigma-Delta ADC數(shù)據(jù)Sheet

LT1719:4.5 ns單/雙電源3V/5V比較器,帶軌對軌輸出數(shù)據(jù)表

LT1720/LT1721:雙/四,4.5 ns,單電源3V/5V比較器,帶軌對軌輸出數(shù)據(jù)表

LT6020/LT6020-1:雙微功耗、5V/μ精密軌對軌輸出放大器產(chǎn)品手冊

LT1713/LT1714:單/雙,7 ns,低功耗,3V/5V/±5V軌對軌比較器數(shù)據(jù)表

AD5320:2.7 V至5.5 V,140μA,SOT-23數(shù)據(jù)表中的軌至軌輸出12位DAC

3V和5V 12位軌到軌微功耗DAC兼具靈活性和性能

3V和5V 12位軌到軌微功耗DAC兼具靈活性和性能

評論