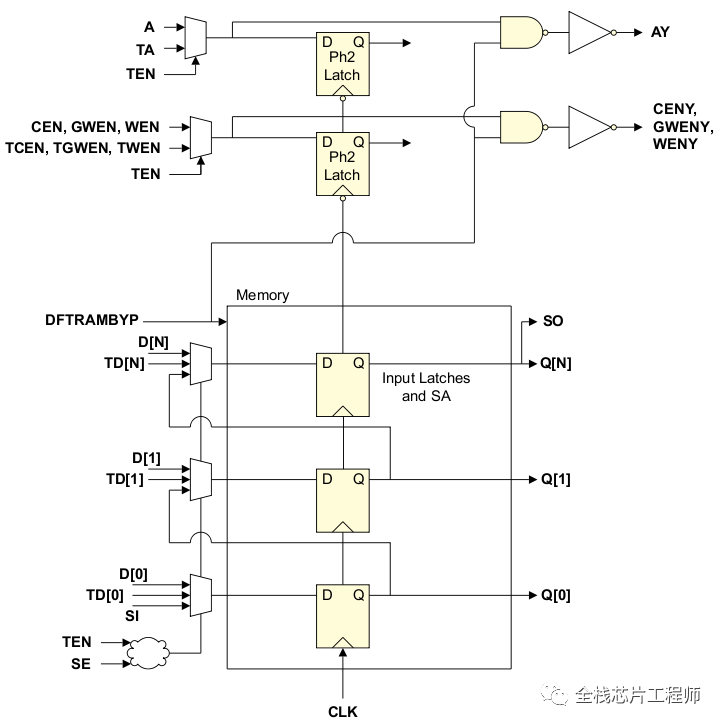

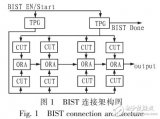

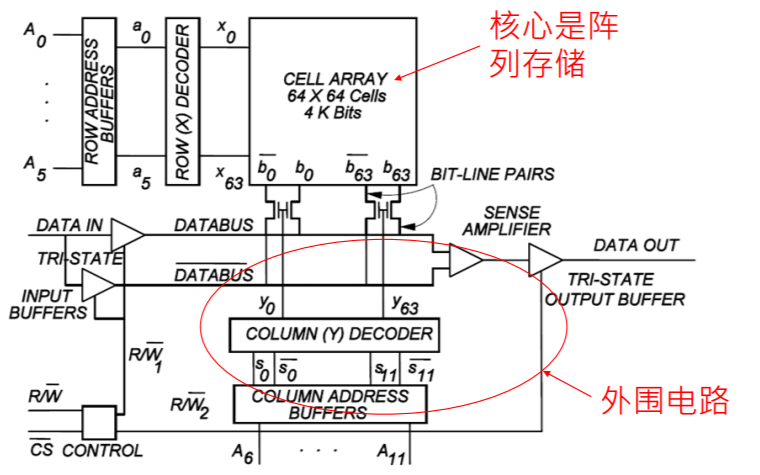

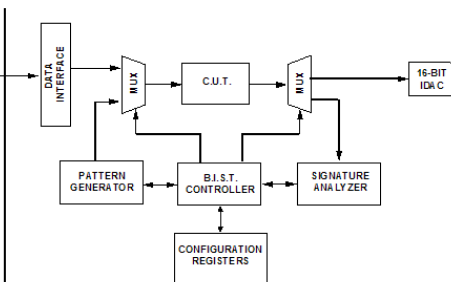

SRAM的MBIST測試結構如下:

SRAM的MBIST測試波形:

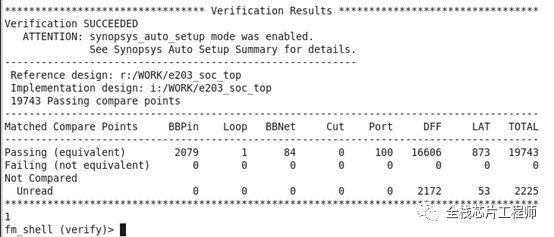

SRAM BIST電路完成插入后,需要做一個formal check,保證Mbist插入后,logic function不發生錯誤改變。Formal check需要注意常量設置,具體參見知識星球的詳細解釋。

此處分享2個經典問題:

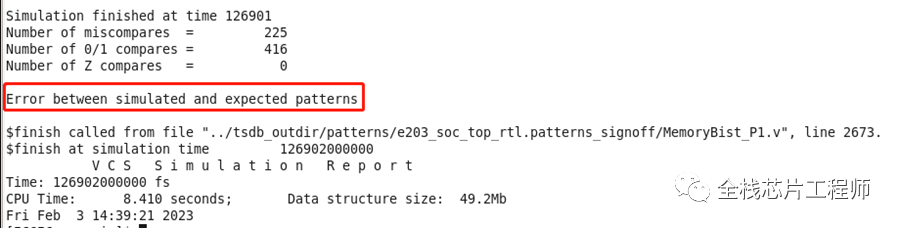

定位1:

通過trace TDO信號,一直追蹤到SRAM的Q端,發現Q端數據輸出是X態,通過分析發現本質上還是時鐘問題,什么問題呢?

就是SRAM MBIST_CLK延時下來剛好和SRAM測試地址TADDR的跳變完全對齊了,造成了SRAM的memory model的建立/保持時間違例,SRAM model在timing違例情況下Q端輸出為X態。下文具體內容請移步知識星球查看。

歡迎加入【全棧芯片工程師】知識星球,手把手教你設計MCU、圖像傳感器、ISP圖像處理,從算法、前端、DFT到后端全流程設計。

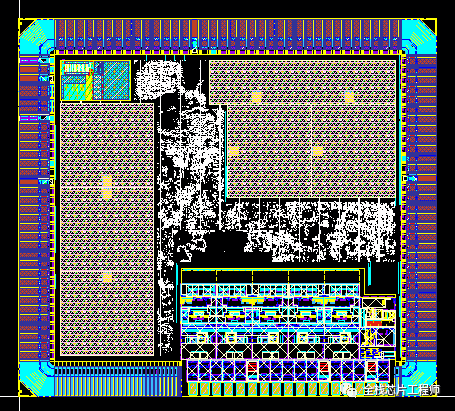

實戰MCU+ISP圖像處理芯片版圖

實戰ISP圖像算法效果

審核編輯 :李倩

-

芯片

+關注

關注

454文章

50460瀏覽量

421981 -

mcu

+關注

關注

146文章

17019瀏覽量

350375 -

圖像傳感器

+關注

關注

68文章

1886瀏覽量

129464

原文標題:MCU芯片的Memory Bist設計實戰(一)

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于BIST利用ORCA結構測試FPGA邏輯單元的方法

DFT和BIST在SoC設計中的應用

數字BIST的基本原則

ZC706 BIST編譯在Linux上失敗

S32K BIST當sw調用api Bist_Run() 以啟動bist時,mcu重置了怎么處理?

基于LFSR優化的BIST低功耗設計

針對FPGA可編程邏輯模塊的離線BIST測試方法

Memory芯片的測試資料詳細說明

RISC-V MCU開發實戰 (二):SD初應用

MCU芯片的Memory Bist設計實戰(一)

MCU芯片的Memory Bist設計實戰(一)

評論