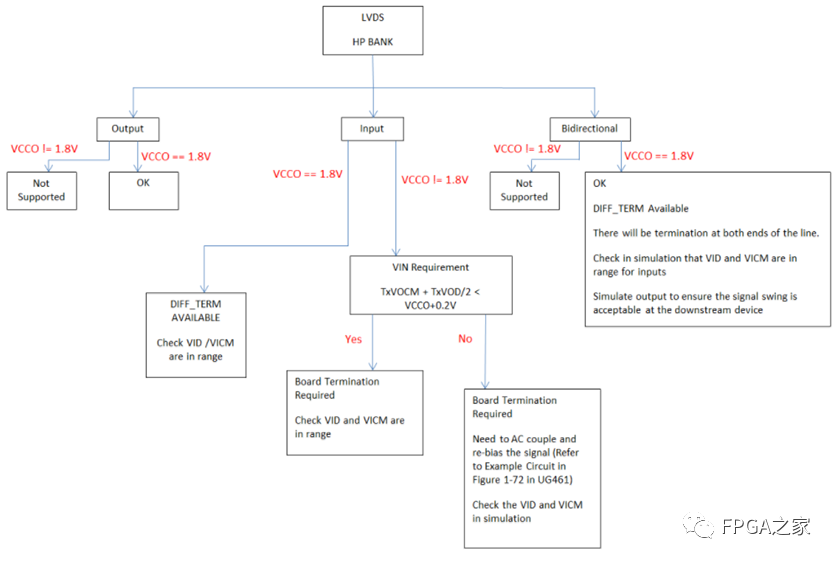

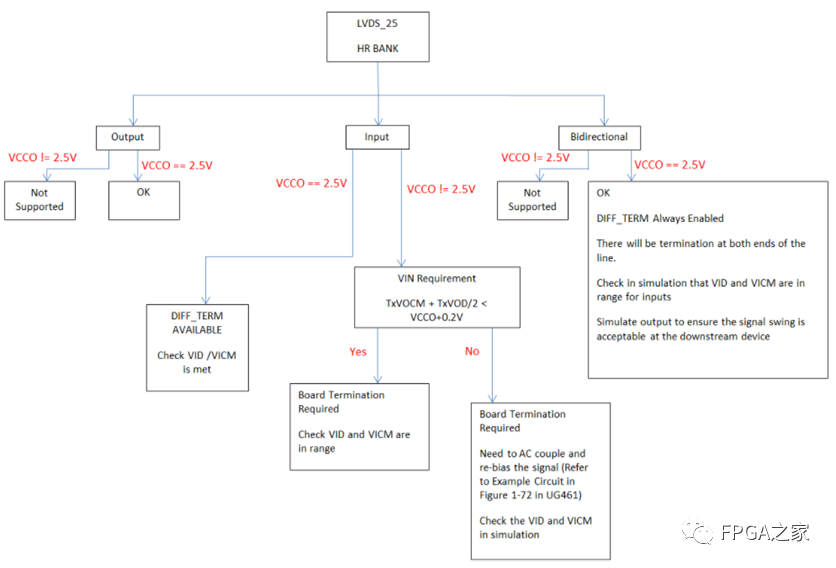

很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電平)連接到了VCCO=2.5V或者3.3V的Bank上,于是產生了關于FPGA引腳與LVDS(以及LVDS-33,LVDS-25)信號相連時兼容性的問題,該專題就解決一下這類問題。總的來說,只要按照下面圖 1和圖 2流程進行判斷即可。

這里補充一點知識,Xilinx的FPGA從7系開始分HR IO Bank和HP IO Bank,其中HR(High Range)Bank支持1.2V,1.5V,1.8V,2.5V以及3.3V供電;而HP(High Performance)Bank只支持1.2V,1.5V,1.8V供電,不再支持2.5V和3.3V供電。

針對LVDS的兼容性,圖 1和圖 2已經可以解決絕大多數問題了,這里做一些補充和解釋。

很明確的結論:作為輸入引腳時,VCCO不等于1.8V的Bank有可能可以連接LVDS電平標準輸入;VCCO不等于2.5V的Bank有可能可以連接LVDS_25電平標準輸入。但是作為LVDS輸出引腳時, 相應Bank的VCCO必須與電平標準的電壓相匹配。

VCCO是IO Bank的Output Driver的驅動電源,Input Receiver中部分功能是由VCCAUX供電的。這就解釋了為什么作為輸入引腳時,電平標準可以與VCCO不匹配。當然Input Receiver也受到VCCO的影響,見第3條。

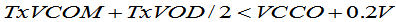

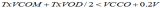

當LVDS作為輸入引腳時,判斷是否可以使用的第一條原則是,作為輸入信號的絕對電平不能超過VCCO+0.2V這個絕對電壓門限,否則有可能損壞引腳的Input Receiver。這是圖 1和圖 2中都做了

判斷的根本原因。

判斷的根本原因。

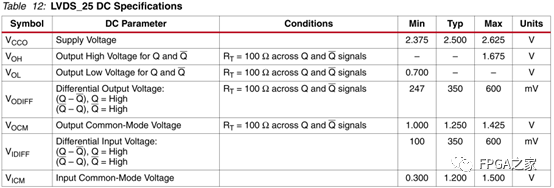

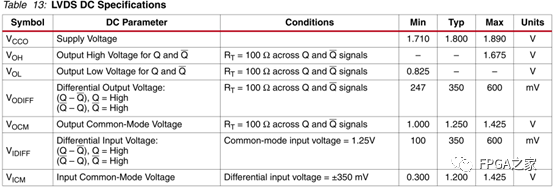

當LVDS作為輸入引腳時,判斷是否可以使用的第二條原則就是對比信號輸入與Xilinx相關器件的LVDS的共模電壓以及峰峰值的指標是否滿足。例如Kintex系列的器件需要查閱DS182中的相關參數,如下圖所示。

當LVDS作為輸入引腳時,如果相應Bank的VCCO與對應的電平標準不匹配,即使可以使用,但DIFF_TERM功能一定不可使用。

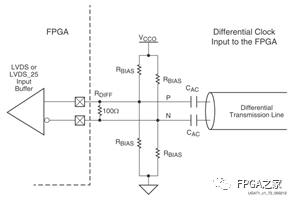

當LVDS作為輸入引腳時,如果確實沒有辦法滿足圖 1和圖 2的條件時,可以使用AC耦合的解決方案。其原理在于所謂的電平不匹配都是共模電壓不匹配,如果使用如圖 5所示的電路,其中AC耦合電容將DC電壓阻斷,也就是TX端的共模電壓不會傳到RX端,RX端只能接收到差分的輸入信號,而RX端的共模電壓通過RBIAS進行調節,以滿足RX端接收到的絕對電壓不會超過VCCO+0.2的要求。

Xilinx FPGA中的LVDS current-mode driver是真正的電流驅動器,不是電壓模擬型的驅動器。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602044 -

Xilinx

+關注

關注

71文章

2164瀏覽量

121044 -

信號

+關注

關注

11文章

2781瀏覽量

76651 -

lvds

+關注

關注

2文章

1039瀏覽量

65714 -

開發板

+關注

關注

25文章

4959瀏覽量

97217

原文標題:FPGA與LVDS信號兼容性分析方法

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

系統的電磁兼容性分析模型及設計方法

電磁兼容性主要的幾種整改方法

基于JavaScript瀏覽器兼容性測試方法

一文看懂電磁兼容性原理與方法及設計

openEuler Summit 2021-兼容性分論壇:OSV認證體系實踐探索及Android版本兼容性認證分析

FPGA與LVDS信號兼容性分析方法

FPGA與LVDS信號兼容性分析方法

評論