隨著半導體工藝的不斷發展,器件特征尺寸逐漸減少,激發單粒子翻轉(Single Event Upset, SEU)效應所需的能量閾值呈幾何級下降趨勢。例如,65 nm工藝下器件發生電平翻轉需6500個電荷,16 nm工藝下器件電平翻轉僅需1000個電荷 。

雖然電平錯誤翻轉引發的軟錯誤不會對電路造成永久性的破壞,但是由于發生的能量閾值較低,所以在所有單粒子效應造成集成電路工作失效的事件中,電平錯誤翻轉效應引起的事件占有比例最高,為40%。

由此可見,軟錯誤已經成為先進工藝下大規模數字集成電路在輻射環境中最為主要的失效模式,這極大地限制了集成電路在一些可靠性較高的領域尤其是富含高通量低能粒子的航天航空場景中的應用。為促進航空航天事業的快速發展,需要對集成電路功能軟錯誤的敏感性進行充分的研究和評估。

在所有的評估手段中,空間環境實測的方式獲得的數據最為準確,但航天器的發射次數和載荷都是有限的,實驗機會少且價格昂貴。因此,更多的評估手段被開發出來,主要有輻照測試,軟件仿真和現場可編程門陣列(Field Programmable Gate Array, FPGA)模擬等技術路線 。

輻照測試可以精確控制輻射強度和時間,相比空間試驗有著良好的可控性和靈活性。但是搭建輻照測試環境的開銷依然非常龐大,具備輻照測試條件的單位也極少。此外,輻照測試需要批量測試,在測試過程中也極可能損傷芯片,且芯片出錯后也很難定位敏感節點,故一般只用于成品芯片的性能測試和最終測試。

軟件仿真通過數學分析方法,將真實情況下單粒子效應對電路造成的影響轉化為故障產生概率,故障持續時間和故障節點位置等故障模型參數,最后將故障注入到電路中 。

軟件仿真的優勢在于模擬單粒子效應的靈活性,可從工藝級、器件級、晶體管級、門級和行為級各個層次對單粒子效應進行建模、仿真和分析。但隨著電路規模的增加,軟件仿真計算過程的時間開銷也在顯著增加,諸如開關級模擬的時間爆炸問題 。

相對于軟件仿真技術,FPGA模擬單粒子翻轉效應的實現成本更低,評估速度更快,更適合用于快速評估集成電路對單粒子翻轉效應的敏感程度。具體實現方式主要有FPGA重配置注入故障,掃描鏈注入故障和旁路電路注入故障3種。

FPGA重配置注入故障是基于FPGA的重配置功能,在運行過程中,動態修改FPGA的配置信息以實現注入故障。掃描鏈注入故障是復用可測性設計的掃描鏈結構,將故障寫至掃描鏈的入口,控制掃描鏈的數據進行串行移動,將故障準確寫入待評估的寄存器中。旁路電路注入故障的實現原理和掃描鏈注入故障的實現原理類似,也是在原有的電路結構上添加附加電路,然后對電路注入故障以模擬單粒子翻轉效應,但是消除了掃描鏈注入故障速度慢的缺點。

FPGA重配置注入故障、掃描鏈注入故障和旁路電路注入故障由于實現方式不一樣,在評估速度、敏感點定位精度和使用電路規模等性能上也各有優劣。本文總結了FPGA重配置注入故障技術,討論了掃描鏈注入故障技術,描述了旁路電路注入故障技術,對比了3種注入故障技術并對各類技術的發展方向進行了展望。

2

** FPGA重配置注入故障**

FPGA的配置信息包含了各類邏輯資源的配置狀況、電壓標準、連線情況和用戶設計的使用情況 ^[14]^ 。借助配置控制指令,即可通過專用的配置讀寫接口(Internal Configuration Access Port,ICAP)訪問FPGA的配置信息 ^[15]^ ;同時也能將其中某一位數據進行翻轉(如0到1或1到0),再把修改后的配置信息寫回FPGA以實現故障注入;最后持續讀取配置信息還可監控故障注入后對電路造成的影響。

基于重配置的故障注入流程如圖1所示,按照配置范圍的大小,FPGA重配置技術可以進一步分為全局重配置和部分重配置 ^[16-17]^ 。全局重配置對整個FPGA芯片進行重新配置。在配置過程中,FPGA由于原始配置信息被清除而處于非正常工作狀態,直到配置信息重新完整寫入,FPGA才能正確工作。因此,從時間軸上看,FPGA工作是不連續的。全局重配置的優勢在于配置過程的實現十分簡單,不需要分析待測電路所使用的硬件資源,同時其電路評估速度比軟件仿真要快幾個數量級。

全局重配置的方式也存在重大缺陷,由于每次故障注入時都需要重新配置全部信息,會引入一定的時間開銷,而且時間開銷和配置信息的大小成正比。以Xilinx Zynq 7020為例,配置文件的大小為32.5 Mbit,在工作頻率為100 MHz時,單次配置全部配置信息所需時間為32 ms ;如果對32.5 Mbit里每個比特位均進行一次故障注入測試,總計時間為284 h。

部分重配置則克服了以上缺陷,可選擇部分配置信息進行重配置,未重配置的電路不受影響,對應的功能仍然可以正常運作。由于部分重配置大幅減少了讀寫的配置信息,可顯著縮短重配置時間。

文獻[19]使用Xilinx Virtex系列FPGA作為測試平臺,當以全局重配置模式對電路注入故障時,完成單次配置需要169.738 ms。而如果只修改和待測電路相關的8 frame配置信息,僅需0.424 ms。此外,對于FPGA設計的電路,FPGA的利用率一般不會達到100%,未使用的空閑配置位無需被注入故障,這可以進一步減少時間開銷 ^[20]^ 。

基于重配置的故障注入技術的主要優勢是基于FPGA的內部功能實現,因此不會對待測電路造成影響,不會產生額外的硬件資源開銷,實現成本極低,可適用于大規模電路,且電路評估速度也較為理想。但也存在不足之處,主要體現在3個方面。

其一是待評估的FPGA必須具備重配置功能,限制了FPGA硬件的選擇范圍。其二是每次執行故障注入時,需要訪問、修改和重寫配置信息,使得上位機和待評估FPGA之間會進行大量的數據交互,相對于FPGA電路的運行時間,交互過程產生的時間開銷要高的多。以Xilinx Virtex系列FPGA為例,理論上配置全部比特位所需時間為9.9 ms,但實際通過計算機并口傳輸配置數據的過程需要20 s 。

部分重配置減少了信息交互的數據量,提高了評估效率,但整體測試的時間開銷中數據交互過程仍占有較大比例。其三是主流FPGA的配置信息是加密的,雖然FPGA重配置技術能夠在電路中注入故障,但是電路出現故障后,由于無法解析主流FPGA的配置信息,所以很難定位到具體的電路節點,給加固設計帶來了困難。

3

掃描鏈注入故障

掃描鏈源于可測性設計。在可測性設計中,首先將寄存器替換為掃描寄存器,然后將多個掃描寄存器相連以形成掃描鏈結構,最后以移位寄存器的工作方式將測試激勵寫入掃描鏈的首端,或者將測試響應從掃描鏈的末端讀出 。

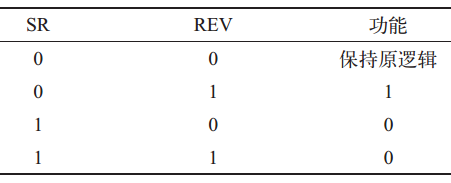

可視作在普通寄存器結構上添加了一個2選1數據選擇器。掃描寄存器有兩個工作模式,工作模式的切換由信號Scan_en決定。當Scan_en不使能時,掃描寄存器為正常工作模式,此時功能等同于常規的D寄存器,采樣輸入端D的電平并輸出。當Scan_en使能時,寄存器切換為掃描模式,此時可通過Scan_in輸入故障數據以模擬單粒子翻轉效應 。

將當前掃描寄存器的輸出端Q和下一級掃描寄存器輸入端Scan_in連接起來,就構成了掃描鏈。掃描鏈結構如圖3所示,基于掃描寄存器的結構和工作原理可推導出,Scan_en不使能時,電路正常工作。Scan_en使能時,可以通過移位將故障數據串行輸入到任意寄存器的Scan_in端,最終實現對任意寄存器注入故障以模擬單粒子翻轉效應。

在實現掃描鏈注入故障電路時,掃描鏈的結構不是固定的,不同的掃描鏈電路產生的資源開銷和故障注入速度也不同。文獻[23]設計了3種不同的掃描鏈電路來實現故障注入,其中開銷最大的電路和開銷最小的電路資源開銷相差近3倍,但單次故障注入時間減少了數微秒,雖然速度區別不大,但在大規模電路測試中能節約的時間開銷極為可觀。因此測試人員可根據測試平臺提供資源(寄存器和數據選擇器等)的大小和實際可達到的注入速度權衡使用合適的掃描鏈電路。

掃描鏈技術的優勢在于可適用于任意規模電路的測試,也可用于ASIC電路的評估,同時不受FPGA測試平臺的限制。故障注入速度最快可達到微秒級別,相對于重配置技術有了進一步的提高。由于掃描鏈的插入對象可以是任意觸發器,因此故障注入后電路敏感節點的定位精度也較高。其最主要的缺陷是會產生額外的資源開銷,且額外開銷會隨著電路規模的增大而增加。此外,為了能夠正確定位電路對單粒子翻轉效應的敏感區域,串行移位時鐘的頻率還不能較高,這樣使得掃描鏈串行移位的時間開銷顯得頗為可觀,需要在掃描鏈長度和評估速度上做出折衷。

最后,值得指出的是,掃描鏈技術在故障數據傳輸過程中存在和重配置技術一樣的問題。文獻[24]中提到所設計掃描鏈的單次故障注入速度為1 μs左右,但受串口傳輸的限制,每次故障激勵數據的下發需要3.84 ms,因此接口的傳輸速率成為制約速度的主要因素。文獻[22]中每次注入故障時需要主機和FPGA進行故障數據交互過程,頻繁地通信導致故障注入速度偏慢。文獻[23]針對數據通信過程進行了優化,將測試電路所需的故障激勵數據一次性全部發送到FPGA的存儲區,隨后FPGA內部自動執行全部測試過程,主機和FPGA只需在起始階段通信一次,減小了數據通信的時間開銷,故障注入速度相對于文獻[22]提高了2個數量級。

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598956 -

半導體

+關注

關注

334文章

26331瀏覽量

210054 -

電平

+關注

關注

5文章

352瀏覽量

39717 -

器件

+關注

關注

4文章

294瀏覽量

27717

發布評論請先 登錄

相關推薦

單粒子翻轉引起SRAM型FPGA的故障機理闡述

單粒子翻轉效應的FPGA模擬技術 (上)

單粒子翻轉效應的FPGA模擬技術 (上)

評論