2022年,集成電路半導體行業最熱的頭條是“EDA被全面封鎖”。如何突破EDA封鎖,成為行業發展的關鍵詞,也是群體焦慮。在全球市場,有人比喻EDA是“芯片之母”,如果沒有了芯片,工業發展和社會進步將處處受制,EDA的重要性也上升到了戰略性高度。盡管國際封鎖形勢嚴峻,但睿智的中國科技人擅于把危機化為機會,從《加快自動研發應用,讓工業軟件不再卡脖子》,到《破解科技卡脖子要打好三張牌》,即一要打好“基礎牌”,提升基礎創新能力;二要打好“應用牌”,加強對高精尖國貨的應用;三是要打好“人才牌”,讓人才留得住、用得上、有發展……,各種政策、舉措和實際行動,處處彰顯了我們中國科技的發展韌性。

我們EDA探索頻道,今天迎來了第9期的精彩內容——控制閾值電壓,下面就跟著小編一起來開啟今天的探索之旅吧~

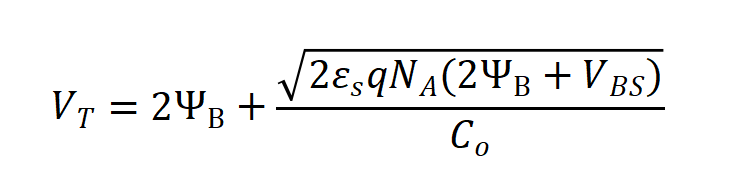

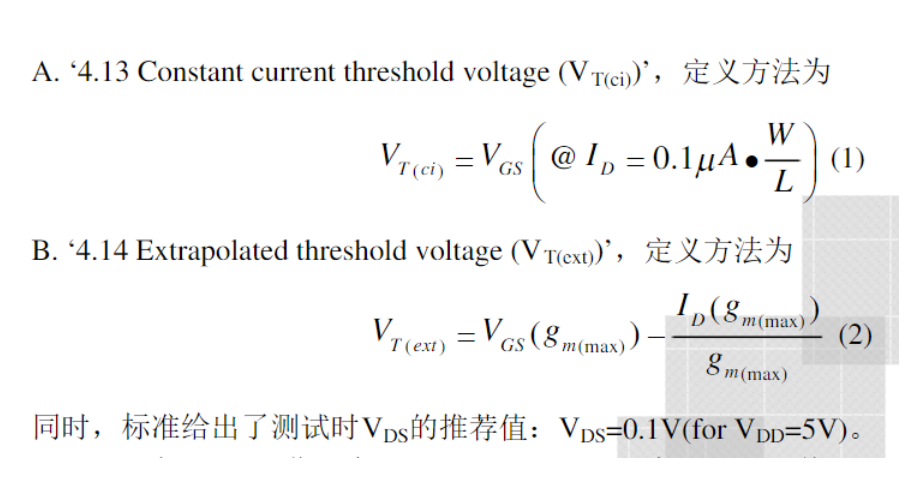

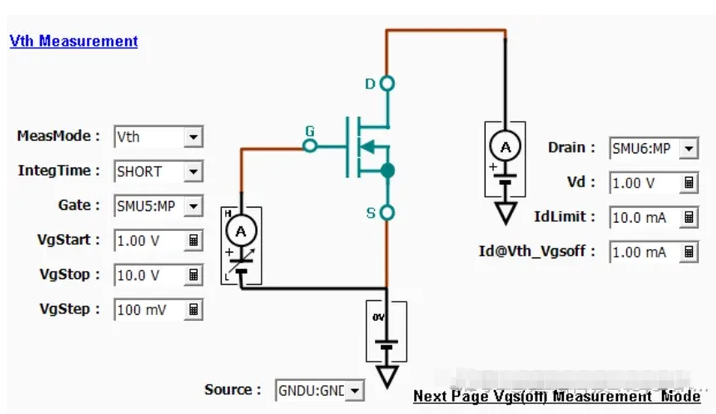

MOSFET的最重要參數之一便是閾值電壓,理想的閾值電壓由以下公式給出。

然而,當我們考慮到固定氧化物電荷的影響和功函數的差異時,就會出現一個平帶電壓移動。

此外,襯底偏壓也能影響閾值電壓。當在襯底和源極之間施加反向偏壓時,耗盡區被加寬,實現反轉所需的閾值電壓也必須增加,以適應更大的Qsc。

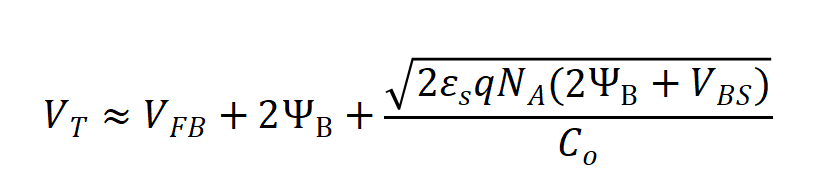

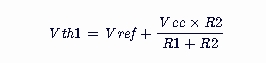

考慮到這些因素,得到的閾值電壓表達式為:

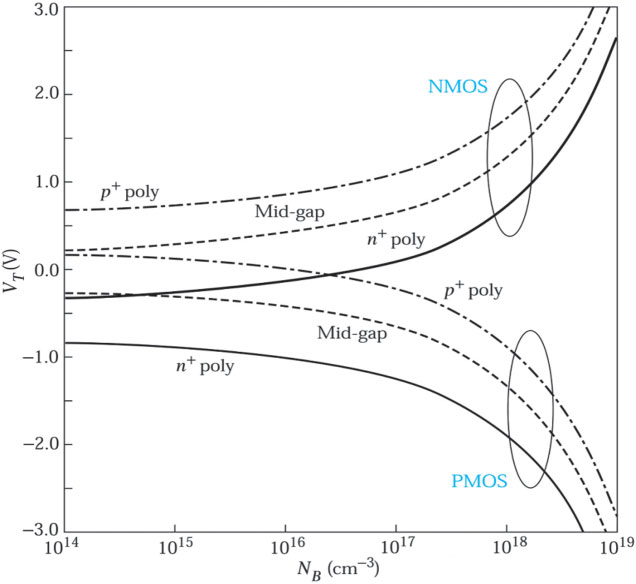

圖:NMOS與PMOS管在不同柵極條件下的計算結果。柵氧化層為5nm, VBS=0, Qf=0

引自S.M.Sze“SemiconductorDevicesPhysicsandTechnology”

上圖是一個計算結果,對應的是不同柵極的NMOS和PMOS的閾值電壓與襯底摻雜的關系。本征的多晶硅柵極相當于4.61eV的功函數。

精確控制集成電路中MOSFET的閾值電壓對電路的可靠性至關重要。通常情況下,閾值電壓是通過向溝道區的離子注入來調整的。例如,經過表面氧化層的硼注入通常被用來調整n溝道MOSFET的閾值電壓(帶p型襯底)。通過增大溝道的摻雜濃度來提升閾值電壓。由于離子注入的能量和劑量是可以精確控制的,可以由此實現對閾值電壓的精確控制。同理,向p型溝道注入少量的硼可以減少VT。

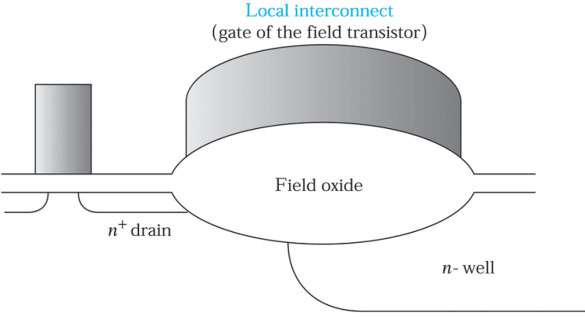

我們還可以通過改變氧化物的厚度來控制VT。隨著氧化層厚度的增加,n溝道MOSFET的閾值電壓變得更正,p溝道MOSFET的閾值電壓變得更負。這是由于在一定的柵極電壓下,氧化物越厚,相應的場強越小。這種方法被廣泛用于隔離在芯片上的晶體管。下圖顯示了隔離氧化層(也稱為場氧化層)在n+擴散區和n阱之間的橫截面。

圖:寄生的場區晶體管橫截面示意圖

引自S.M.Sze“SemiconductorDevicesPhysicsandTechnology”

n+擴散區是n型溝道區或者MOSFET的源區或漏區。MOSFET的柵極氧化物要比場氧化物薄得多。當電力線在場氧化層上形成時,就會產生一個寄生的MOSFET,也稱為“場區晶體管”,其n+擴散區和n阱區分別作為源極和漏極。

場區晶體管的VT通常比正常的薄柵氧化物的VT大一個數量級。在電路正常運行時,場效應晶體管不會被打開。因此,場氧化層在n+擴散區和n孔區之間提供了良好的隔離。

襯底偏壓也可以用來調整閾值電壓。源極和襯底可能不在同一電位上。在器件正常工作時,源和襯底之間的p-n結必須是零或反向偏壓。如果VBS為零,襯底的表面電位為2ψB。當施加反向襯底-源極偏壓(VBS>0)時,溝道中的電子電勢則會拉高到高于源極的電勢的水平。溝道中的電子將被橫向推到源極。如果要保持在強反型條件下溝道中的電子密度保持不變,柵極電壓必須提高到2ψB+VBS。

審核編輯 :李倩

-

MOSFET

+關注

關注

144文章

7088瀏覽量

212717 -

電壓

+關注

關注

45文章

5562瀏覽量

115586 -

閾值

+關注

關注

0文章

123瀏覽量

18472

原文標題:EDA探索丨第9期:控制閾值電壓

文章出處:【微信號:hzwtech,微信公眾號:鴻之微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

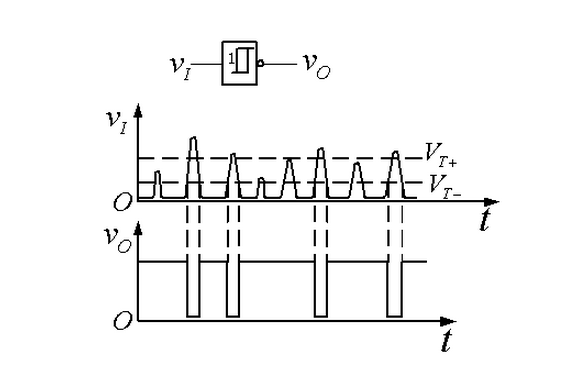

解答74HC14中正向閾值電壓和負向閾值電壓是什么/電壓為多少

MOS管閾值電壓的問題

如何解釋閾值電壓與溫度成反比這個現象?

閾值電壓的計算

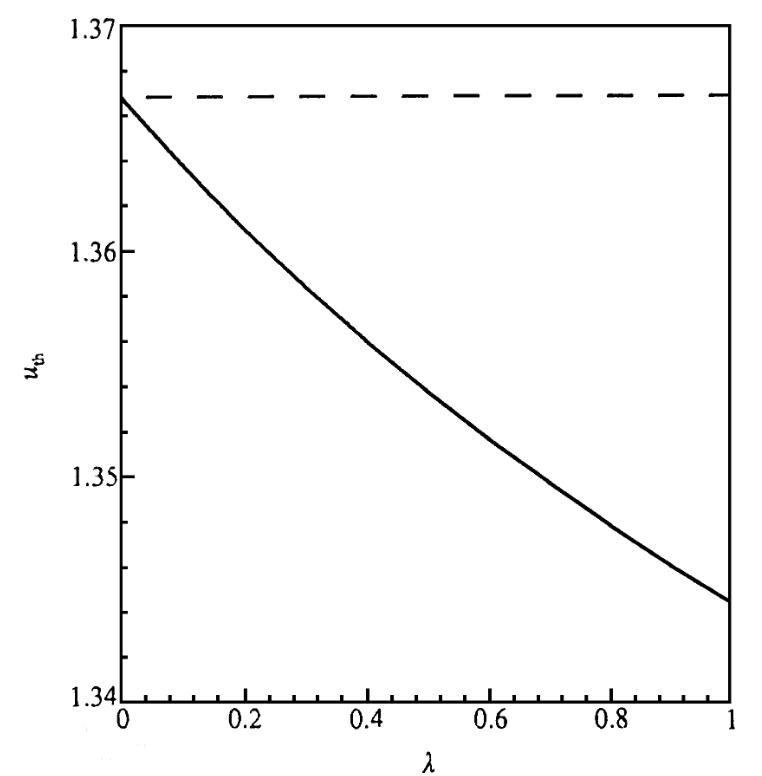

MOS管閾值電壓與溝長和溝寬的關系

如何突破EDA封鎖 卷起來的閾值電壓

NMOS晶體管的閾值電壓公式 nmos晶體管的閾值電壓與哪些因素有關

影響MOSFET閾值電壓的因素

什么是MOS管亞閾值電壓?MOSFET中的閾值電壓是如何產生的?

淺談影響MOSFET閾值電壓的因素

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

滯回比較器的閾值電壓如何確定?

控制閾值電壓

控制閾值電壓

評論