端口聲明

模塊定義包括一個(gè)端口列表,該列表用括號(hào)括起來。端口用于將數(shù)據(jù)傳入或傳出模塊。模塊可以有四種類型的端口:輸入、輸出、雙向輸入輸出和接口(input,output, bidirectional inout,和 interface)。輸入、輸出和輸入輸出端口是離散端口,其中每個(gè)端口通信一個(gè)值或用戶定義的類型。接口端口是復(fù)合端口,可以通信多個(gè)值的集合。本文介紹離散端口的語法和使用指南。后續(xù)將介紹接口端口。

可綜合端口聲明

端口聲明定義端口的方向、類型、數(shù)據(jù)類型、符號(hào)、大小和名稱(direction, type, data type, sign, size 和 name)。

- 端口方向用關(guān)鍵字input、output或inout聲明,

- port類型和數(shù)據(jù)類型可以是變量,也可以是之前介紹的任何網(wǎng)絡(luò)類型和數(shù)據(jù)類型。

- 端口標(biāo)志可以是有符號(hào)的,也可以是無符號(hào)的。

- 端口大小的范圍從1位寬到2^16(65536)位寬。在實(shí)踐中,工程師必須考慮FPGA技術(shù)將用于實(shí)現(xiàn)設(shè)計(jì)的尺寸限制。

端口在模塊端口列表中聲明,該列表用簡(jiǎn)單的括號(hào)括起來。端口可以按任何順序列出。一些工程師喜歡先列出輸入,然后列出輸出。其他工程師更喜歡先列出輸出,然后列出輸入。一些公司對(duì)端口的順序有嚴(yán)格的編碼風(fēng)格規(guī)則,而其他公司則將順序留給編寫模塊定義的工程師。對(duì)于縮進(jìn)的使用,工程師們?cè)诰幋a風(fēng)格上也有很大的不同,是否在同一行或單獨(dú)的行上列出多個(gè)端口,這些都沒有統(tǒng)一的標(biāo)準(zhǔn)。

SystemVerilog提供用于聲明端口列表和端口聲明的編碼樣式:組合樣式、傳統(tǒng)樣式和具有組合類型和大小的傳統(tǒng)樣式(combined-style, legacy-style and legacy-style with combined type and size)。

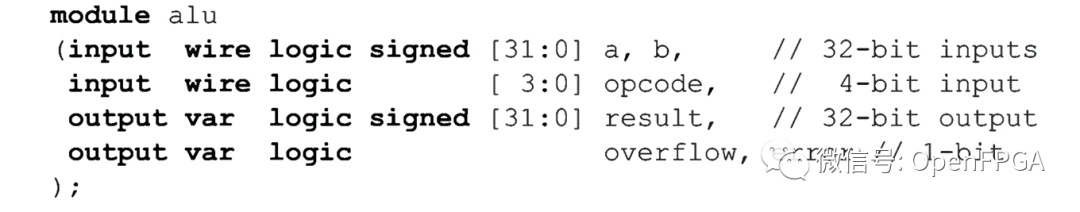

組合樣式端口列表,組合樣式端口列表將每個(gè)端口的完整聲明放在端口列表括號(hào)內(nèi)。大多數(shù)工程師都喜歡這種風(fēng)格。

請(qǐng)注意,每個(gè)端口聲明都用逗號(hào)分隔,并且列表中的最后一個(gè)端口在 右括號(hào)前沒有逗號(hào) 。

可以使用以逗號(hào)分隔的端口名列表聲明具有相同方向、類型、數(shù)據(jù)類型和大小的多個(gè)端口。通過組合相似端口的聲明,前面的端口列表可以簡(jiǎn)化為:

IEEE SystemVerilog標(biāo)準(zhǔn)將端口聲明的組合樣式定義為ANSI樣式的端口列表,因?yàn)樵摌邮筋愃朴诤瘮?shù)聲明的ANSI C樣式。這種類型的端口聲明作為Verilog2001標(biāo)準(zhǔn)的一部分添加到Verilog中。

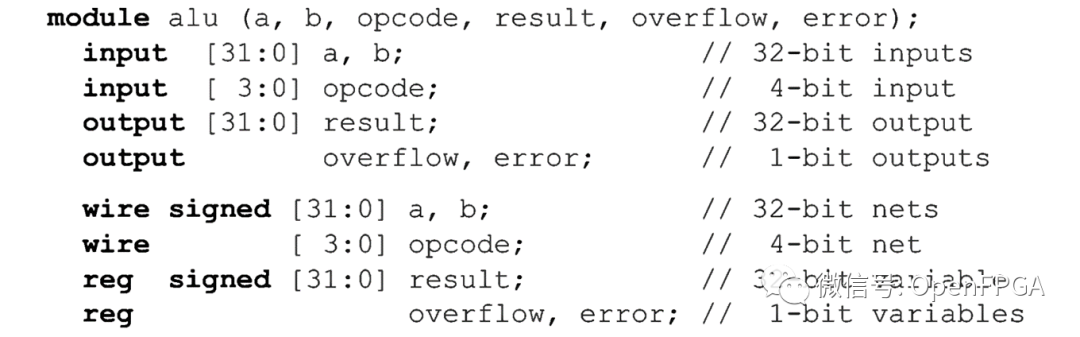

傳統(tǒng)樣式端口列表。 最初的Verilog-1995標(biāo)準(zhǔn)將端口列表和每個(gè)端口的類型、數(shù)據(jù)類型、符號(hào)和大小聲明分開。SystemVerilog標(biāo)準(zhǔn)將此分離樣式稱為非ANSI樣式端口列表。此樣式類似于原始的、ANSI C之前的函數(shù)聲明樣式。下面的示例使用Verilog-2001數(shù)據(jù)類型。SystemVeriIog邏輯類型也可用于傳統(tǒng)Verilog樣式的端口列表:

請(qǐng)注意,每個(gè)端口聲明都以分號(hào)結(jié)尾,但可以對(duì)具有相同方向和大小,或相同類型、數(shù)據(jù)類型和大小(例如端口a和b,或前面端口聲明中的overflow和error)的端口使用逗號(hào)分隔的端口名列表。

如果端口列表中的第一個(gè)端口上的端口方向、類型、數(shù)據(jù)類型、符號(hào)和大小都被省略,則整個(gè)端口列表將采用傳統(tǒng)的非ANSI樣式的端口列表。端口列表中的所有端口必須是組合的ANSI樣式或傳統(tǒng)的ANSI樣式。在同一端口列表中混合使用這兩種樣式是非法的。

具有組合方向和大小的傳統(tǒng)樣式端口列表。 Verilog-2001標(biāo)準(zhǔn)允許傳統(tǒng)樣式的端口列表將方向聲明和類型/數(shù)據(jù)類型聲明組合到單個(gè)語句中。

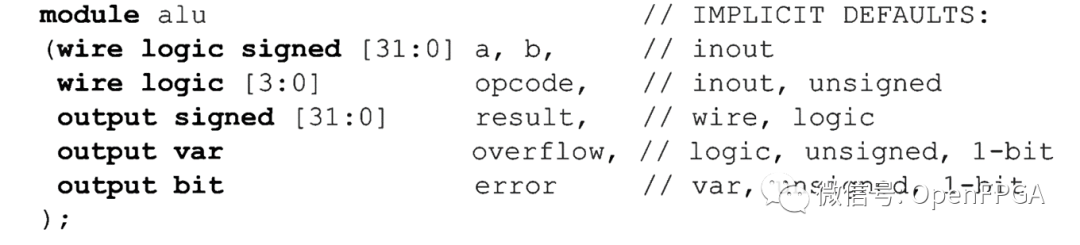

模塊端口默認(rèn)值 。每個(gè)端口的方向、類型、數(shù)據(jù)類型、有無符號(hào)和大小都有隱式默認(rèn)值。端口類型可以是網(wǎng)絡(luò)(如wire)或變量(如var)。端口數(shù)據(jù)類型可以是logic(4態(tài))或bit(2態(tài))。端口方向、類型、數(shù)據(jù)類型、有無符號(hào)和大小的默認(rèn)規(guī)則為:

- 未指定方向-模塊端口的默認(rèn)方向?yàn)閕nout,但僅在定義方向之前,一旦指定方向,該方向?qū)?yīng)用于所有后續(xù)端口,直到指定新方向。

- 未指定類型No type specified-未指定數(shù)據(jù)類型(如邏輯)時(shí),默認(rèn)類型端口為wire,指定數(shù)據(jù)類型時(shí),默認(rèn)類型為wire(輸入和輸入輸出端口)和var(輸出端口),并且可以使用'default_nettype編譯器指令更改wire。

- 未指定數(shù)據(jù)類型No data type specified-所有端口的默認(rèn)數(shù)據(jù)類型為logic(4態(tài))。

- 未指定有無符號(hào)No signedness specified-默認(rèn)有無符號(hào)是端口數(shù)據(jù)類型的默認(rèn)有無符號(hào),reg、logic、bit和time數(shù)據(jù)類型默認(rèn)為unsigned。byte、shortint、int、integer和longint數(shù)據(jù)類型默認(rèn)為signed。

- 未指定大小No size specified-默認(rèn)大小是端口數(shù)據(jù)類型的默認(rèn)大小。該條例;邏輯和位數(shù)據(jù)類型默認(rèn)為1位寬。

下面的代碼片段不是真實(shí)的RTL編碼樣式,但用于說明模塊端口聲明的隱式默認(rèn)值。

盡管前面代碼段中的端口聲明是可綜合的,但對(duì)于可綜合的RTL模型,不建議使用這種編碼樣式。

繼承的端口聲明。 端口的方向、類型、數(shù)據(jù)類型、有無符號(hào)或大小的顯式聲明可以由端口列表中的后續(xù)端口繼承。繼承的端口特征是“粘滯的”,因?yàn)樘卣鲿?huì)一直粘滯(保持有效),直到發(fā)生更改。

端口聲明繼承規(guī)則包括:

- 繼承的端口方向-顯式端口方向聲明在指定新方向之前保持有效,即使端口類型發(fā)生更改。

- 繼承的端口類型-在指定新的方向或類型之前,顯式端口類型聲明保持有效。

- 繼承的端口數(shù)據(jù)類型-在指定新的方向、類型或數(shù)據(jù)類型之前,顯式端口數(shù)據(jù)類型聲明保持有效。

- 繼承的端口有無符號(hào)-顯式端口有無符號(hào)聲明在指定新的方向或類型或數(shù)據(jù)類型或大小之前保持有效,

- 繼承的端口大小-在指定新的方向或類型或數(shù)據(jù)類型或大小之前,顯式端口大小聲明保持有效。

下面代碼段不是推薦的RTL編碼樣式,但說明了后續(xù)端口如何從模塊端口列表中先前的端口聲明繼承特征。

不可綜合的端口聲明

SystemVerilog具有幾種主要綜合編譯器不普遍支持的其他端口類型和聲明功能,包括:

- 模塊ref參考端口

- 模塊互連端口

- 輸入端口默認(rèn)值(如input logic [7:0] a=0)

- 輸出端口默認(rèn)值(如output logic [7:0] y=l

- 端口表達(dá)式(例如.b({c,d}))

- 具有隱式端口的外部模塊和嵌套模塊

一些綜合編譯器可能支持其中一些構(gòu)造,但本文中沒有討論它們,因?yàn)樵诒疚木帉憰r(shí),并非所有主要綜合編譯器都支持它們。這些構(gòu)造對(duì)于驗(yàn)證非常有用,并且超出了本文關(guān)于RTL建模的范圍。

模塊端口聲明建議

SystemVerilog為聲明模塊端口提供了相當(dāng)大的能力和靈活性,如本節(jié)所示。工程師應(yīng)對(duì)端口聲明采用一致的編碼風(fēng)格,以確保模型能夠自我記錄,更易于維護(hù),并且更易于在未來項(xiàng)目中重復(fù)使用。

最佳做法準(zhǔn)則3-9| 最佳做法準(zhǔn)則3-9 |

| ------------------------------------------------------------------------- |

| 對(duì)模塊端口列表使用ANSI-C樣式聲明。將輸入端口和輸出端口聲明為logic類型。 |

聲明模塊端口的一些最佳實(shí)踐編碼建議包括:

- 使用組合的ANSI-C樣式端口列表,以便所有端口信息都包含在端口列表中。

- 聲明每個(gè)端口的方向,而不是依賴默認(rèn)端口方向和繼承的(粘性)端口方向。

- 將所有端口數(shù)據(jù)類型聲明為logic數(shù)據(jù)類型。避免RTL模型中的2態(tài)數(shù)據(jù)類型-它們可能隱藏設(shè)計(jì)錯(cuò)誤。

- 不要聲明端口類型,允許語言推斷wire或var類型。輸入和輸出端口的隱式默認(rèn)類型適用于可綜合的RTL級(jí)別模型。例外:三態(tài)端口可以選擇性地聲明為三態(tài)類型。tri類型與wire相同,但顯式聲明有助于記錄端口應(yīng)為三態(tài)聲明,

- 在單獨(dú)的行上聲明每個(gè)端口。這允許添加注釋來描述每個(gè)端口的用法或假設(shè),例外情況:可以接受以逗號(hào)分隔的端口名稱列表,這些端口名稱都具有相同的方向、數(shù)據(jù)類型、大小和類似用法。

示例3-3說明了使用這些編碼準(zhǔn)則的模塊端口列表。

示例3-3:使用推薦編碼準(zhǔn)則的模塊端口聲明

`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords

module alu

(input logic signed [31:0] a, b, // ALU operand inputs

input logic [ 3:0] opcode, // ALU operation code

output logic signed [31:0] result, // Operation result

output logic overflow, // Set if result overflowed

output logic error // Set if operation errored

);

timeunit 1ns; timeprecision 100ps;

/////////////////////////////////////////////

// model functionality not shown //

/////////////////////////////////////////////

endmodule: alu

`end_keywords

傳統(tǒng)的Verilog考慮因素 。在SystemVeriIog之前,傳統(tǒng)的Verilog沒有l(wèi)ogic數(shù)據(jù)類型,對(duì)于隱式默認(rèn)端口類型有不同的規(guī)則。傳統(tǒng)的Verilog會(huì)為所有端口假定一種端口類型wire,除非該端口被顯式聲明為reg,這將推斷出一個(gè)變量。工程師必須小心地使用顯式端口聲明,以確保每個(gè)端口具有模塊內(nèi)功能的正確類型和數(shù)據(jù)類型。要使所有聲明正確,通常需要編譯代碼、檢查編譯錯(cuò)誤或更糟的情況、容易忽略的警告、修復(fù)錯(cuò)誤或警告,然后重新編譯。對(duì)功能建模方式的更改通常會(huì)導(dǎo)致新的編譯錯(cuò)誤,因?yàn)檫€需要更改端口數(shù)據(jù)類型。

SystemVerilog使端口聲明更加容易。只需將所有端口聲明為logic數(shù)據(jù)類型,并讓語言正確推斷出正確的網(wǎng)絡(luò)或變量類型。SystemVerilog幾乎在所有情況下都能正確推斷出網(wǎng)絡(luò)或變量。

-

接口

+關(guān)注

關(guān)注

33文章

8497瀏覽量

150834 -

輸出

+關(guān)注

關(guān)注

0文章

90瀏覽量

21814 -

端口

+關(guān)注

關(guān)注

4文章

955瀏覽量

32014 -

輸入

+關(guān)注

關(guān)注

0文章

21瀏覽量

5249

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA學(xué)習(xí)筆記---基本語法

【鋯石A4 FPGA試用體驗(yàn)】按鍵消抖例程存在的問題

【鋯石A4 FPGA試用體驗(yàn)】開發(fā)板資源(一)蜂鳴器

【鋯石A4 FPGA試用體驗(yàn)】開發(fā)板資源(六)電子時(shí)鐘(2)

【鋯石A4 FPGA試用體驗(yàn)】——小炮與鋯石A4的故事(6)——簡(jiǎn)易含1序列檢測(cè)器

【鋯石A4 FPGA試用體驗(yàn)】Qsys(四)Qsys系統(tǒng)添加到Quartus II工程中

用quartus編程遇見一個(gè)從未見過的錯(cuò)誤,也搜索不到解決辦法,望各位大神幫幫忙

vivado帶ip核的工程封裝

【FPGA】UART頂層模塊的實(shí)體聲明寫法

如何使用XC6LX45T在SP605基板上實(shí)現(xiàn)ADC?

在SpinalHDL的設(shè)計(jì)中集成現(xiàn)有RTL設(shè)計(jì)(IP)的渠道——BlackBox

在SpinalHDL中的代碼組織結(jié)構(gòu)如何實(shí)現(xiàn)Component參數(shù)化設(shè)計(jì)呢

在FPGA開發(fā)中盡量避免全局復(fù)位的使用?(5)

講解function任務(wù)的用法

什么是端口聲明

什么是端口聲明

評(píng)論