如果要評選電子工程師近20年來的最耳熟能詳的專業詞匯,眼圖和抖動作為孿生姊妹一定在前10之列。所以業界關于抖動的論述和文章也是時常見諸各種媒體和平臺。

本期我們將就抖動和抖動測試做一個專題介紹,包括如下主題:

01. 抖動研究的源起

02. 抖動測試和分析的基本方法和經典理論

03. 抖動測試的演進和新挑戰

04. 影響抖動測試結果和精度的因素

1. 抖動研究的源起

抖動測試最早在上個世紀80年代開始萌芽,HP公司電信網絡測試部門-蘇格蘭科技公司1982年在蘇格蘭推出了針對PDH(Plesiochronous Digital Hierarchy,準同步數字體系)的第一個抖動測量儀器,速率高達E3和DS3,之后在1984年推出首批140 Mb / s抖動測試儀之一。

在90年代推出針對SONET / SDH抖動測試產品和方案。事實上在同步數字傳輸體系(SONET/SDH)和通訊系統中引入抖動的概念主要用于評估數據包級的傳輸延時偏差。因此大家也可以看到經典抖動定義也來自于當年的業界巨擘貝爾實驗室。

進入90年代以后,隨著數字電路系統中的源同步時鐘總線的發展,由于外部同步時鐘頻率漸漸成為瓶頸開始轉向嵌入式時鐘的串行差分總線,非常典型的就是PCI總線同步時鐘頻率最高到133MHz就開始轉向PCIE1.0 2.5Gbps發展。由此對數字電路系統中的水平時間參數的測量也從傳統的Setup/Hold或Skew測量轉為水平方向Jitter的測量。

在今天,抖動測試除了是很多高速串行總線和標準的一致性測試眾多項目中的重要組成部分和內容,同時還是針對系統級傳輸性能評估的重要方法,以及探究系統問題根源的重要手段。因此對抖動進行深入的探索和研究無論何時都具有深刻的意義和價值。

2. 抖動測試和分析的基本方法和經典理論

在90年代,伴隨著數字電路和系統的串行差分化的同時以x86處理器為核心的軟硬件系統廣泛應用于各行業,當然也包括測試測量行業,示波器也開始全面武裝更強大的x86處理器和windows操作系統,隨之而來的是各種算法程序的全面發展和推進,這其中就包括了抖動測量算法和分離的經典理論。

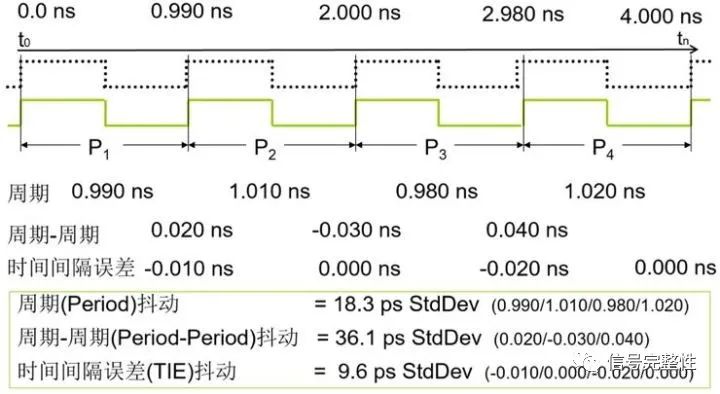

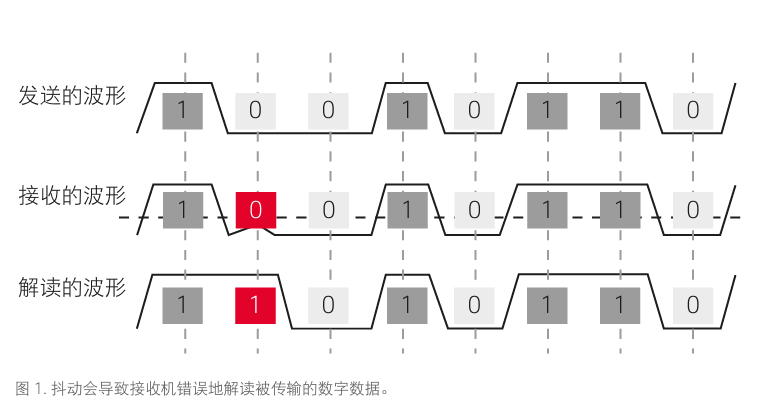

下圖顯示的是充斥于各種文獻的抖動測量中三種基本的抖動算法:

圖1 基本抖動算法示意圖

周期抖動算法比較簡單,以信號本身的每個周期值為樣本進行統計分析,可以反映所有樣本的平均值及個體與圓心即平均值偏差的情況,用于一般的時鐘信號的評估。

周期-周期抖動以兩個相鄰周期的周期差值為樣本進行統計分析,很明顯這是對信號周期的一階微分運算,這一指標對分析鎖相環的性能時有很高價值。由此還衍生出N周期—N周期抖動,比如針對DDR總線的時鐘測試中就有5/10個連續時鐘周期抖動的測試。

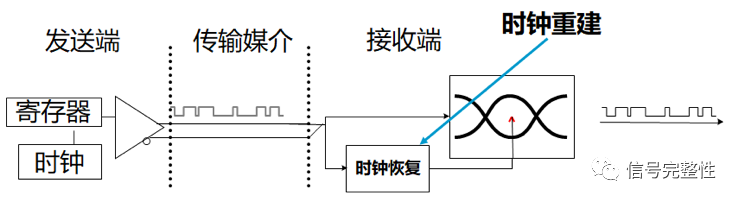

第三個度量方法,時間間隔誤差(Time Interval Error,簡稱TIE)抖動,有時也被稱作相位抖動(Phase Jitter),以每個周期點的累計時間值相對當前時間點的理想值偏差為樣本進行統計分析,這個時間偏差算法呈現累積效應,是一個積分運算,可以反映出信號的長期抖動,而這一理想位置則需要通過軟件時鐘恢復(實時示波器方法)或者通過外部輸入/硬件時鐘恢復(采樣示波器方法)得到一個參考時鐘作為運算的基準。

TIE抖動在今天的數字電路與通信系統中已經成為分析數據傳輸中的抖動指標和性能的最為通用的抖動度量方法。關于以上三個經典抖動算法定義和描述,推薦閱讀Ref [6]-- PCI ExpressTM Jitter Modeling Revision 1.0RD.

圖2 時間間隔誤差抖動測量方法示意圖

除了上述三個度量方法還有常用到的三個統計學參數:

平均值:相對絕對值的一個固定偏移或偏差,通常不重要因為可以修正。

RMS抖動:通常用于表征隨機抖動成分。

Peak-to-Peak抖動:可用于表征確定性(有界)和隨機(無界)抖動分量,另外必須在給定的BER下引用或考慮隨機(無界)抖動。小測驗:

在實時示波器進入windows時代前,業界的老師傅們經常用無限余輝累積觸發位置后的一個時鐘周期邊沿,然后用光標測量邊沿累積后的時間寬度值,如下圖示,請問這是哪種抖動?

A. 周期抖動 B. 周期-周期抖動 C. TIE抖動

圖3 實時示波器上經典抖動測量示意圖

思考:

采樣示波器在進行分析眼圖時也會得到一個抖動測量值,這又是什么抖動呢?

A. 周期抖動 B. 周期-周期抖動 C. TIE抖動

必須要說明的是,業界針對抖動的研究和分析其實最初是從采樣示波器開始。因為上個世紀90年代末采樣示波器相比實時示波器可以實現的帶寬更高(因為等效采樣無需高采樣率配套,且無需考慮普遍信號測試需求通常輸入信號幅度有限因此無衰減和放大器電路因而帶寬更高),同時高ADC位數提供的測量精度也更高,因此首先被用于高速芯片及一些器件如光模塊等串行數據的眼圖分析,并根據眼圖結果衍生出抖動分析和測量。

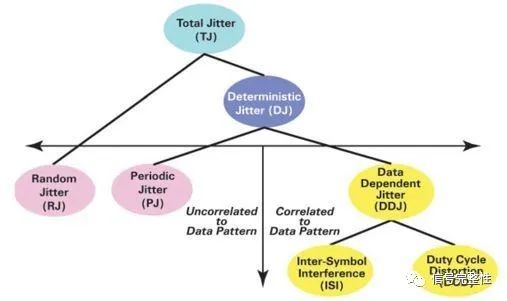

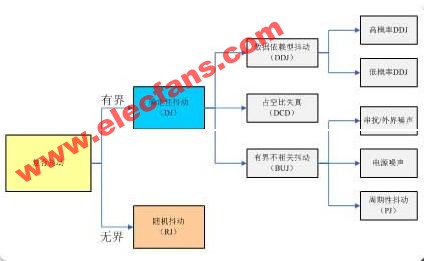

基于眼圖堆疊和測量結果,為了評估數字串行總線傳輸的總體性能因此引入抖動的分析和評估理論。采用的重要評價指標是特定誤碼率(通常是10E-12)水平下的總抖動Tj @ BER,因為 Eye Open= 1UI – Tj @BER。

那么如何得到總體抖動這一結果呢?

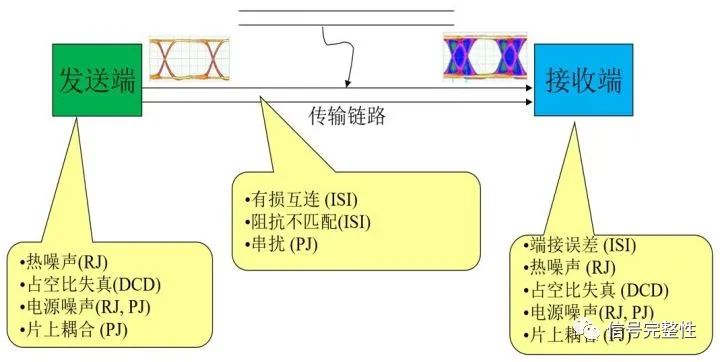

圖4 典型的串行傳輸鏈路中的抖動根源

一種方法是根據上圖中抖動根源按圖索驥分別測量得到Rj和各種Dj成分然后卷積得到給定誤碼水平下的抖動概率密度函數然后推算出Tj。顯然這一方法的可操作性不高尤其是早年基于采樣示波器疊加的眼圖結果進行抖動分析的狀況。

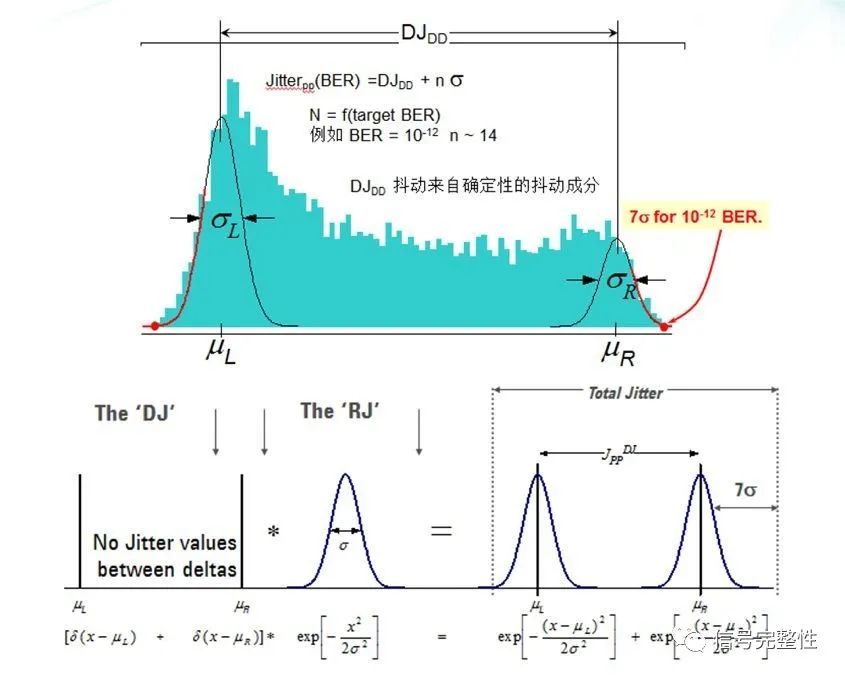

另一種方法就是雙狄拉克模型法(Dual-Dirac Model),通過測量和計算Rj(δ)與Dj(δδ)再根據如下公式:

Tj@BER = n x Rj +Dj

計算得到Tj@BER。通常10E-12誤碼水平時n=14 (因篇幅限制,本文不就n與BER關系做過多描述,參考Ref[1])。

雙狄拉克模型法有5個假設前提:

1. 總體抖動可以分解為Rj和Dj

2. RJ遵循高斯分布,可以用單個相關參數的術語進行完整描述,RJ的rms值分布,或等效地,高斯分布的標準偏差σ

3. Dj遵循有限和有邊界的分布

4. DJ遵循由兩個Dirac-delta函數形成的分布。兩個delta函數的時間延遲分離給出了雙狄拉克模型相關DJ,如下圖所示

5. 抖動是一種靜止現象或者可重復觀測。也就是說,測量了在適當的時間間隔內對給定系統的抖動后無論何時再啟動該時間間隔范圍的測量,都會給出相同的結果

雙狄拉克模型法基于眼圖左右交叉點的抖動直方圖,提供了最簡單的概率密度函數:交叉點分為兩個Dirac-delta函數,位于μL和μR(DJ主導區域),然后采用人為擬合快速過渡到RJ主導的尾部。有許多方法可以實現雙狄拉克模型,在所有這些模型中,估計總體抖動的主要問題是如何描述抖動分布尾部的問題,兩個標準偏差為σ的高斯分布的尾部由固定量DJ(δδ)= |μL - μR|分隔。

圖5 雙狄拉克模型分解RJ和DJ示意圖

有的時候還會經常看到另一個測量結果DJ(p-p),這個如何理解?

真實的DJ從不遵循簡單的雙狄拉克分布,因此期望從雙狄拉克模型中提取的DJ接近實際的峰峰值DJ是不合理的。DJ(δδ)是模型相關量,必須在假設DJ遵循由兩個Dirac-delta函數形成的分布的情況下導出,如圖5所示。

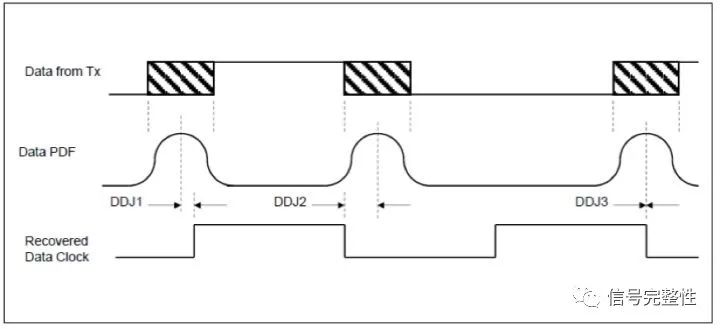

相比DJ(δδ)總是可以測量得到,而DJ(p-p)只能在特定情況下可測。比如當DJ僅由數據相關抖動(DDJ)組成時,可以通過比較重復數據碼型的平均跳變次數來測量。通常DJ(δδ)小于DJ(p-p)。因此總結,DJ(δδ)定義明確且可測,而DJ(p-p)僅能在特定情況下測量得到,而且對估計總體抖動沒有作用。

順便提一下,雖然DJ(p-p)無法測量且意義不大,但是DJ的子成分如DDJ(p-p)和ISI(p-p)卻是有界且可測,在實時抖動分析結果里經常可以看到。

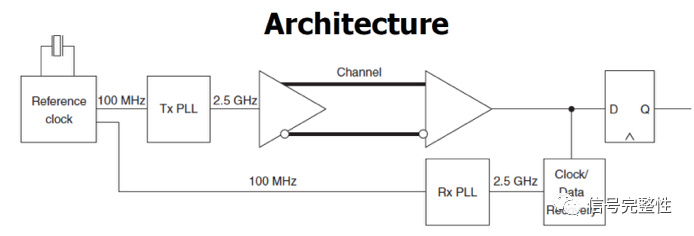

針對一個典型的包含發送端,傳輸鏈路以及接收端以及CLK的典型系統架構,比如PCIExpress:

圖6 典型的PCIExpress架構

通過分別測量和分析得到系統各單元的Rj標準偏差和Dj(δδ)后可以得到整個系統的抖動參數:

之后就可以得到整個系統在特定誤碼率下的總體抖動。關于雙狄拉克模型的相關原理及知識,請參考Ref [1].

由于采樣示波器在早期只是純粹進行眼圖疊加進而進行總體抖動估算而很難對具體的成因進行分析,因此無法滿足很多的應用需求(直到2006年左右在采樣示波器上開發出碼型同步觸發技術從而可以穩定捕獲特定碼型比如不長于2?16的PRBS碼型,才引入了抖動分解技術)。

隨著實時示波器在平臺和性能上的大幅提升,在實時示波器上進行抖動分析越來越普遍并漸漸成為主流。實時示波器無需外部觸發或同步時鐘信號,同時相比采樣示波器具有長內存可以一次觸發采集一定時長的波形用于抖動分析進而做出對實際工作有指導性的抖動分解結果。

那么首先實時示波器如何進行抖動分析呢?

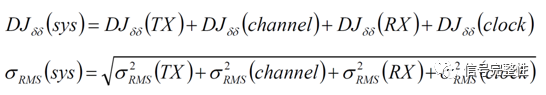

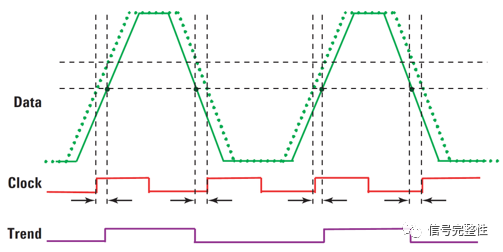

如下圖示,實時示波器首先捕獲一定時長的波形,然后基于特定標準的數據的時鐘恢復算法通常為一階或二階鎖相環,帶寬因標準差異而不同,針對CLK通常采用Constant CLK即首先計算周期的平均值得到基準,分析得到信號的TIE抖動。

基于此TIE抖動結果,抖動分析軟件會分析得到抖動趨勢圖(Trend),這一趨勢圖提供了每個時間點的數據邊沿位置相對于理想位置時間差即TIE的趨勢圖。如果是數據相關抖動DDJ如ISI則會顯示出與數據碼型的強相關性,如果是周期性抖動Pj成分則會顯示出與其它特定頻率信號的相關性。

分析抖動的另一種方法是采用頻域角度,針對TIE抖動趨勢圖做FFT數學函數,基于重復頻率成分的抖動視圖角度。在這種情況下,數據結果被處理繪制為垂直軸上的定時誤差值與水平軸上的頻率。這個角度在尋找與數據本身特征不相關的周期抖動Pj時,會特別有用。

實時抖動分析軟件還提供了“直方圖”視圖,將抖動分析結果顯示為概率分布的函數(PDF)(數據記錄中所有TIE測量結果合成),表現為定時誤差與命中數(N)的二維顯示。實時直方圖的結果應該與從眼圖產生的重復直方圖的測量結果密切相關。但是,通過實時采樣的長存儲深度,可以從單次采集信號中獲得更多數據。此外,基于實時示波器的重復多次采樣,可以產生更準確和完整的PDF。

圖7 EZJIT軟件實時抖動分析的處理方法

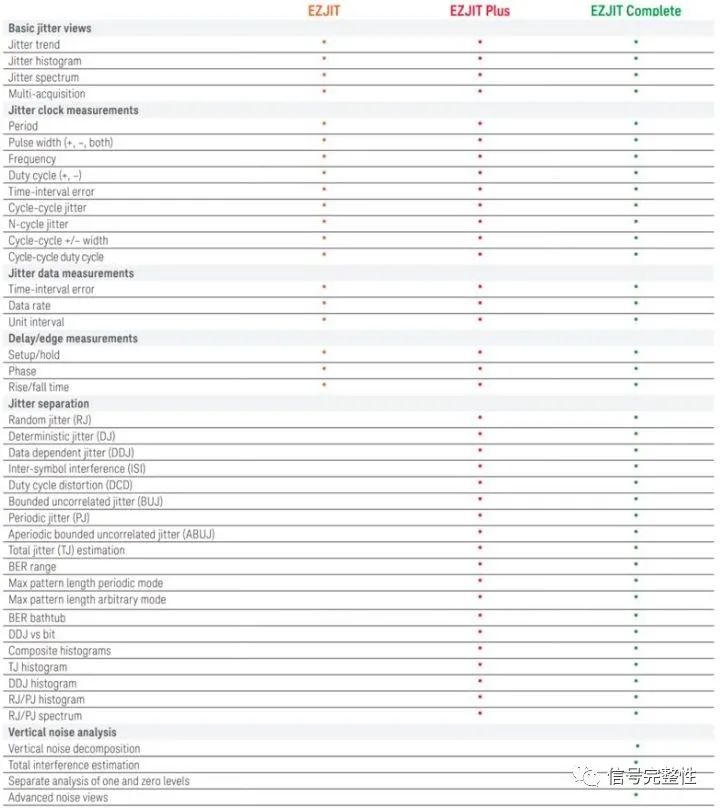

Keysight實時示波器抖動分析軟件EZJIT提供的功能就到這里。

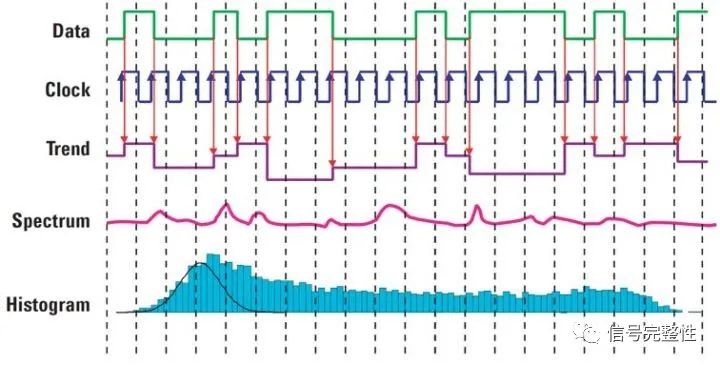

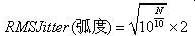

然后,實時抖動分析軟件是如何進行一步步的抖動成分分解的? 抖動分解是EZJIT PLUS的功能。如Ref[2] [3]文獻描述,根據經典抖動成因分解模型:

圖8 經典抖動成因分解模型

首先第一步,根據數據碼型特點(在EZJIT Plus軟件里可以選擇Periodic Data 或Arbitrary Data)將DDJ(數據相關抖動,主要是ISI即碼間干擾)和RJ和PJ(與數據無關抖動成分)分離開來;根據DCD和ISI的不同表現再進行分離。

有時甚至可以采用發送特定如101010…碼型以準確測量DCD抖動。在Arbitrary Data模式下EZJIT PLUS軟件使用線性回歸技術從TJ中提取DDJ。這種線性回歸類似回聲消除或其他自適應濾波應用。這一線性回歸技術要求設定一組系數來描述數據相關抖動的如何從傳輸的數據碼型計算,EZJIT PLUS軟件里指這套系數為ISI Filter。(關于如何設定ISI Filter請參考Ref [5])

圖9 典型DCD(左)和ISI(右)

第二步,基于第一步已經去除了DDJ成分的頻譜圖將PJ和RJ分離。對功率譜密度積分推導出RJrms,PJ成分求和可以得到PJrms。針對RJ的特性在EZJIT Plus軟件里可以設定RJ的帶寬,如白噪聲為寬帶寬,粉紅噪聲為窄帶寬。(相關說明請參考Ref[3])

圖10 分離了DDJ后高于設定閾值的被當作PJ,去除后就可以根據剩余的頻譜分量計算RJrms

第三步,根據TIE的直方圖視圖結果基于前面描述的雙狄拉克模型法擬合出DJ(δ-δ)。結合前面的頻譜法擬合出的RJrms,就可以確定要求的誤碼率水平下的總體抖動即TJ@BER,基于此可以繪出浴盆曲線(Bath Tub)等圖表。

到這里EZJIT PLUS就完成了實時示波器的抖動分析和分解的全部過程,最終輸出包括分解完畢的各個抖動分量值,總體抖動@給定BER水平,浴盆曲線等。這也是我們進行抖動分析和分解最終需要得到的結果。

為了獲得準確的分析和測量結果在進行實時抖動軟件分析時必須進行正確的設置,包括恰當的信號垂直刻度,足夠的波形數據也就是捕獲時長,以及足夠的采樣率設置等等因素,另外針對前面提到的包括數據周期重復模式還是任意碼型,RJ帶寬及噪聲設置,以及如何設置ISI濾波器尺寸等詳細請參考文末所列參考文獻2,3,4,5等。

另外要強調的是足夠的波形數據和捕獲時長除了可以捕獲更多的時鐘周期或數據UI進行更準確的抖動分析外也意味著可以捕獲更低頻的抖動因為捕獲的整個波形周期更長,這也是示波器長存儲的重要價值之一。

3 抖動測試的演進和新挑戰

早年的經典抖動定義和分析分解方法在21世紀初基本已經確立,是通用串行電路分析的重要方法之一。但是隨著數據速率的持續推高和電路復雜程度的加深比如鏈路寬度以及對均衡算法的應用等因素,特定標準的抖動定義和算法也在不斷演進。

典型如PCIExpress3.0/4.0針對TX抖動測試重新進行了規劃,定義TP1測試點(發送端芯片封裝管腳處)抖動分為數據相關抖動和數據不相關成分。數據相關抖動成分主要源于封裝損耗和反射等信號完整性效應。而數據不相關成分則源于PLL抖動,電源噪聲和多鏈路之間串擾等。

PCIE4.0 Base規范里明確說明了之所以做如此分離的原因,因為這種分離與Tx和Rx均衡能力很好地匹配,Tx或Rx均衡不會減輕不相關的抖動成分,也無法通過均衡恢復水平時間窗口裕量即降低抖動或得到更加張開的水平眼圖。重要的是,通過均衡可恢復的裕量(數據相關成分)不作為不可恢復的抖動計入預算。

從Tx測量中去除了數據相關的抖動,就可以分析剩余的抖動成分,計算剩余抖動成分的UTj和確定性抖動(雙狄拉克模型)UDJDD分量。高頻抖動(在通道中受到抖動放大)由分離的TTX-UPW-DJDD和TTX-UPW-TJ參數來解決。

圖11 PCIE4.0 Base規范里描述的DDJ測量和定義

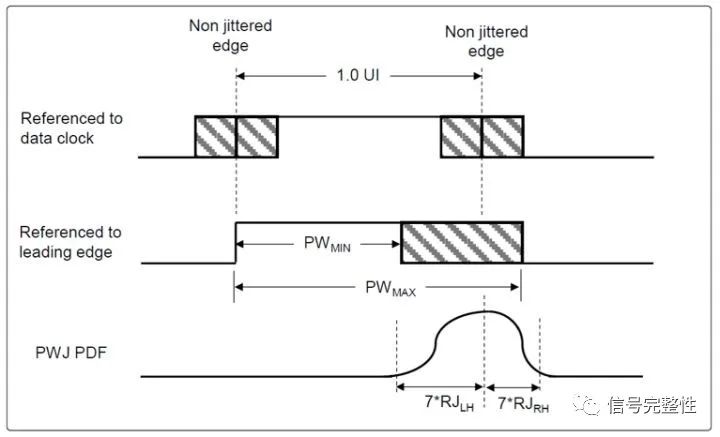

并引入了全新的PWJ,Pulse Width Jitter:

圖 12 PCIE3.0/4.0引入PWJ

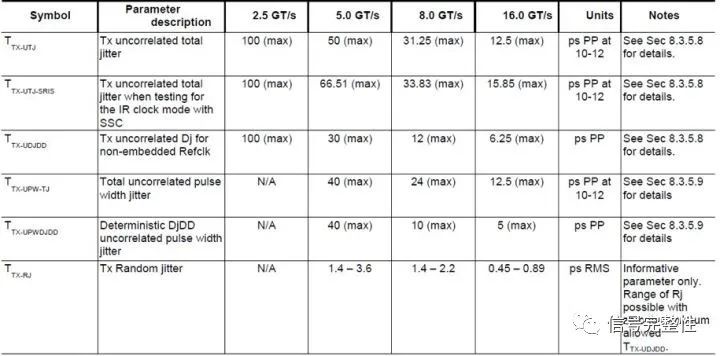

圖13 PCIE4.0 Base規范定義的抖動測量項目

在PCIE4.0 Base規范中,最終定義了如上表的分析項目。可以看到,除了針對性的就DDJ專門做了定義并分離,針對Uncorrelated Jitter依然采用了前面描述的經典抖動分析和分解理論進行分析。關于最新的PCIE4.0標準中,針對抖動測量和分析的定義請參考PCIE4.0 Base規范,Ref [6]。

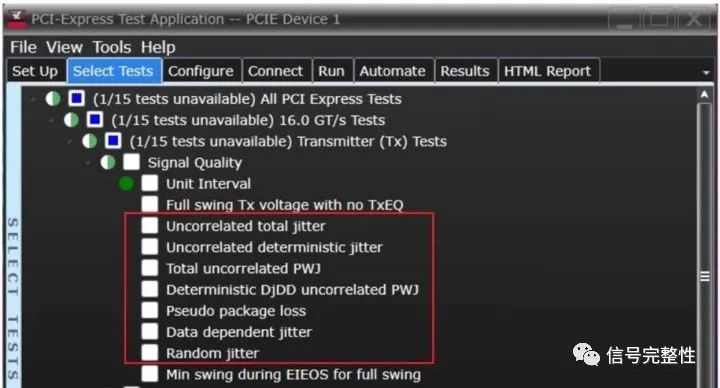

傳統的抖動測試軟件EZJIT作為通用抖動分析軟件,沒有按照PCI Express的新定義進行抖動分析和處理,因此如果需要進行完全符合PCI Express標準和規范的抖動分析就需要借助于實時示波器上的一致性測試軟件如D9040PCIC測試軟件,針對PCIE4.0 Base測試點有非常全面的抖動測試項目如下圖示:

圖14 Keysight D9040PCIC一致性測試軟件測試項目

除了PCIE標準外,其它一些標準在抖動定義和測量分析方面也有很多發展和演進,比如USB3.x標準作為典型的接口一致性測試規定不同的測試碼型,奈奎斯特碼型CP1或者CP10用于RJ,PRBS碼型CP0或CP9用于Tj測試,當然也需要一致性測試軟件進行測試,具體不做更多舉例。

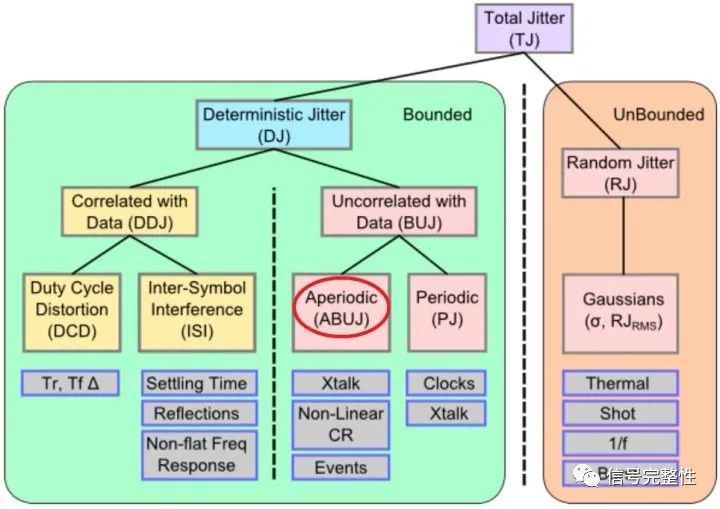

另外針對多鏈路傳輸如IEEE 802.3系列標準在實現200G/400G時,相對早期單鏈路串行總線的抖動定義和測量分析,必須考慮跨鏈路的數據串擾引起的抖動,如下圖所示:

圖15 更全面的抖動成分分解模型

這種串擾或者地彈等引起的抖動,呈現為非周期,有界和與數據無關的特性,因此命名為ABUJ(Aperiodic Bunded Uncorrelated Jitter )。

針對這一新的抖動成因,繼續采用EZJIT Plus軟件的頻譜法分析時,會存在將這一由串擾引起的ABUJ歸入RJ的風險,從而得到過大的RJ結果,最終導致過大的TJ結果,帶來測量誤差。

圖16 數據中存在XTALK引起ABUJ抖動時頻譜法分析RJ產生誤差

如何解決這一新的問題和挑戰呢?

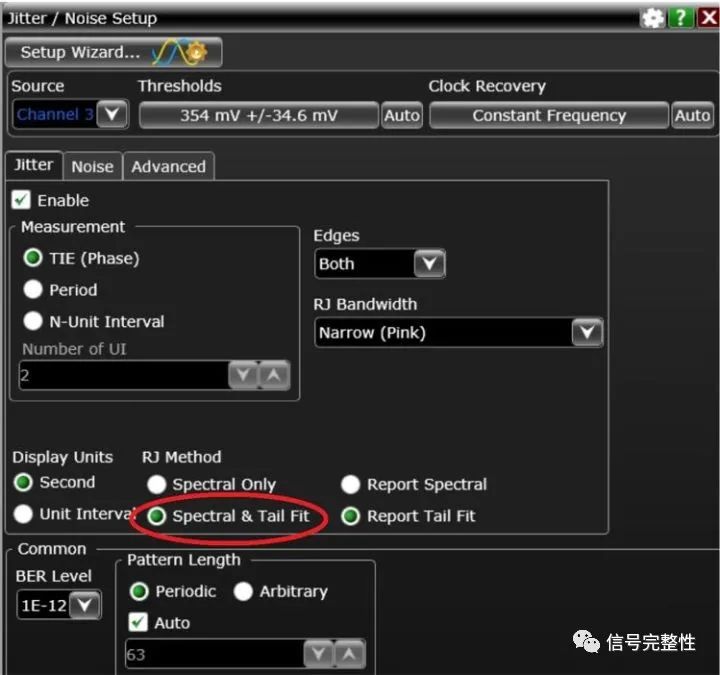

在EZJIT Plus軟件里增加了Tail Fit方法進行RJ提取,如下圖所示:

圖17 EZJIT PLUS軟件里增加Tail Fit法提取RJ

這一方法指的就是在實時示波器的抖動分析軟件里采用雙狄拉克模型法進行RJ提取:

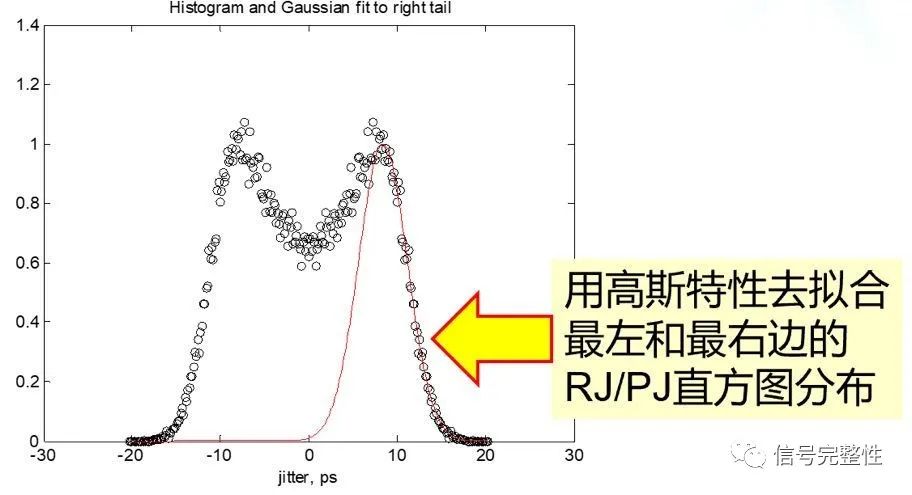

圖18 Tail Fit法RJ擬合示意圖

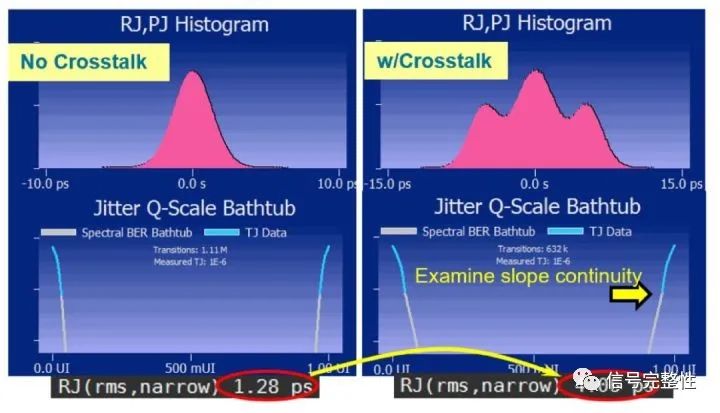

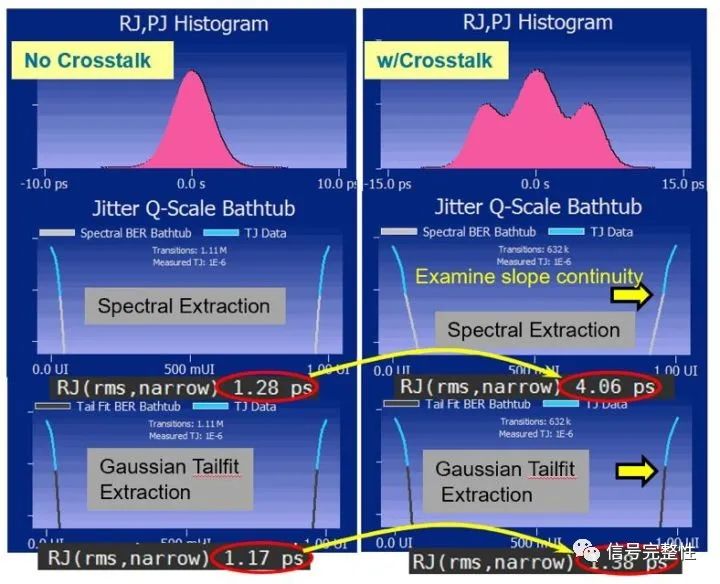

在以往未使用高斯擬合的原因是由于總直方圖中的點稀缺,曲線擬合的點數仍然很少,它會給你帶來不穩定的結果。下圖顯示了針對一個數據信號存在和不存在串擾情況下分別采用頻譜法和高斯尾部擬合法對比的結果。

左邊顯示的是無串擾情況下分別采用頻譜法和高斯法結果相近,右邊顯示在有串擾情況下,頻譜方法得到的RJ明顯偏大,采用高斯法后得到的RJ結果就顯然回歸正常。

圖19 高斯法和Tail Fit兩種方法分別對存在和不存在串擾引起的ABUJ分離差異對比

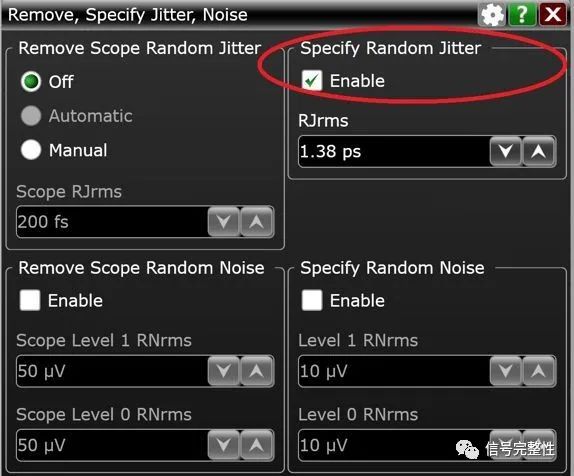

除了采用高斯尾部擬合法外,為了獲得更高精度的測量,還可以先關閉相鄰通道的串擾源,進行一次抖動測量并記錄RJrms結果,打開串擾源,在下圖中指定RJrms,然后再進行抖動測量,ABUJ就被歸入有界抖動,不會被歸入RJ成分并可準確得到,而TJ也可準確得到。

圖20 EZJIT PLUS軟件里手動去除RJ分析ABUJ示意圖

近10年左右,除了在信號水平方向進行更加深入的抖動分析外,在信號的垂直方向進行噪聲和干擾分析也慢慢開始興起,但相比水平方向的抖動對眼圖關閉和系統BER影響的理論比較成熟,業界在垂直方向噪聲和干擾對垂直方向眼圖閉合分析的理論依然在發展中。

垂直方向噪聲和干擾對信號傳輸的影響的分析功能目前在Keysight采樣示波器N1000系列的 N1010100A軟件包和實時示波器的 EZJIT Complete 軟件中均可支持:

圖21 EZJIT軟件3個等級提供強大的測量和分析能力

抖動測量和分析的理論將一直隨著被研究的信號標準的發展而發展,因此其步伐也不會停止,因此本文所列演進和挑戰也只能是略舉一二例罷了。

4 影響抖動測試結果和精度的因素

抖動測量和分析在今天的串行數據電路設計和測試中的重要意義不言而喻,因此如何進行精確測量當然也成為每個工程師都關心的問題。

首先針對被測信號在示波器上要做出正確的測量設置。這些正確設置包括恰當的垂直刻度設置,通常建議信號在垂直刻度方向占滿7格左右即用足垂直顯示精度。

水平方向主要包括足夠的采樣率設置和存儲深度,對實時采樣示波器而言,采樣率應當滿足所用帶寬的2.5倍以上。存儲深度不足導致波形采集數據不足可能會導致實時示波器不能進行正確的時鐘恢復。太長的存儲深度則會導致數據波形過大,運算速度變慢。

因此建議按照規范或標準數據量捕獲波形進行分析,比如部分標準或規范通常推薦1M UI進行分析,USB3.x和PCIE3.0即是如此,當然到PCIE4.0已經更改為2M UI。

對一般性串行數據抖動分析,應當達到100K UI量級數據以上。有時部分標準需要進行SSC(擴頻時鐘)測量,如果進行手動分析,建議根據需要測量的SSC周期數和所用采樣率計算恰當的采樣深度。

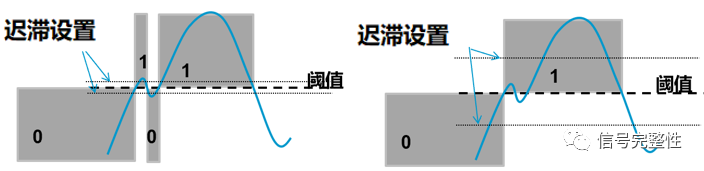

另外針對信號的閾值(Threshold)設置和遲滯(Hysteresis)設置也非常關鍵,通常建議設置信號幅度一半的電平為閾值,差分總線通常為0V。

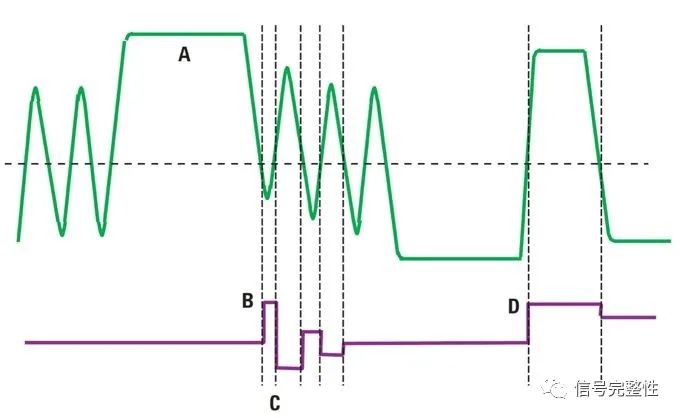

針對一些有共模偏置的信號建議先手動測量信號幅度和共模電壓以選取準確的閾值。準確遲滯設置也非常重要,因為可以避免示波器將信號邊沿上的一些因為反射導致的不連續誤判為ISI抖動的一個bit。

如下圖示,左邊設置的遲滯門限較低,因此會將波形上升沿上的一個回勾當作一個有效bit,顯然這會被歸入ISI抖動,右邊遲滯設置電平門限拉高就會對這個回勾忽略不計。

圖22 準確的遲滯設置避免將波形回勾計為一個bit的ISI抖動

如果想獲得準確TIE測量結果,還有一個必須強調的是準確的遵循被測信號規范設置的時鐘恢復算法,這是實時示波器進行抖動分析和分解的重要基礎。相關信息請閱讀各標準規范。

其它還包括在上期提到的關于EZJIT Plus如何進行抖動分解的一些設置,比如ISI濾波器的大小(Filter Size),Rj帶寬等等。

總之,如果要進行一次準確的抖動分析和測量,涉及的知識非常廣泛的,操作也略顯繁瑣。因此在對抖動測試不甚熟悉的情況下建議使用示波器上的抖動測試向導(Setup Wizard),抖動向導會對信號進行自動設置,包括信號刻度及閾值和遲滯等。建議安裝Keysight實時示波器離線軟件D9010BSEO進一步深入了解。

除了操作層面外,儀器的哪些指標對抖動測量的結果和精度會有比較大的影響呢?或者如何選擇一個恰當的示波器完成預設的目標或工作呢?

首先是測量系統的恰當帶寬。

測量系統帶寬包括示波器和探頭與電纜及夾具等連接部件等,如果不符合標準和規范要求,低于規范要求帶寬則會帶來信號輸入鏈路額外的ISI抖動。

在今天已經普遍應用的針對電纜夾具和探頭的去嵌技術如N2809A—Precision Probe和包含InfiniiSim的D9020ASIA分析套件也可以部分解決這些效應,當然也會帶來額外的副作用即同步放大了儀器的本底噪聲,必然帶來額外誤差。過高帶寬也是不推薦的,因為會引入更多的高頻帶噪聲。

其次實時示波器的采樣率也會有影響。

通常更高采樣率會有更高精度。顯而易見,更高采樣率會有更高的分辨率和邊沿解析度,對最終的抖動分析結果會有影響。

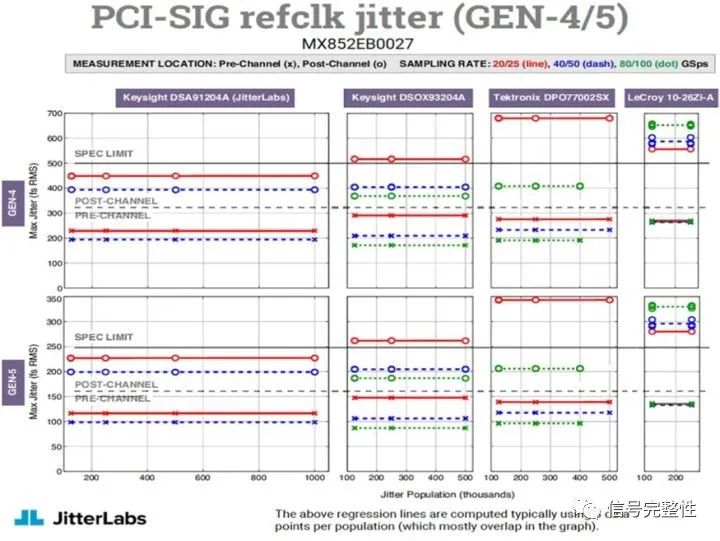

下圖是源自第三方的Jitter Labs針對PCIE Gen4 /Gen5時鐘測量結果對比,可以看到Keysight 90000A和90000X(當前替代型號是V系列)與T公司及L公司另兩款產品測試結果對比。

紅色為20/25GSa/s,藍色為40G/50GSa/s,綠色為80/100GSa/s,Post-Channel和Pre-Channel指對PCIE Gen4/Gen5時鐘測試的不同測試點位置。很明顯在同型號產品上更高采樣率得到的結果更好。K公司產品對比T/L產品相對結果明顯更優,這又是什么原因呢?

圖23 不同型號示波器不同采樣率測試結果對比

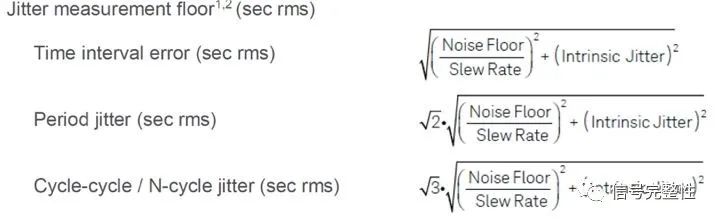

第三,儀器的本底噪聲和固有抖動。

Keysight公司產品相比業界其它公司產品有更低的噪聲本底和固有抖動,因此在上圖Jitter Lab測量對比結果中顯示出更高的精度。

一般實時示波器在采用頻譜法進行抖動分析時都會采用功率譜密度積分得到RJrms值,頻譜法進行功率譜積分時會將示波器的寬頻本底噪聲帶入到RJ的分析結果中,帶來更多的誤差。而儀器的固有抖動也是誤差之源,參考如下公式:

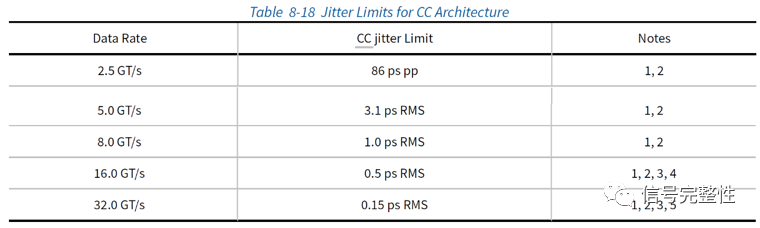

從公式中還可以看出噪聲本底和信號本身的跳變斜率(Slew Rate)相關。在今天越來越低的信號幅度,越來越快的邊沿,越來越低的裕量測試場景下,典型如PCIExpress規范里對CC CLK的CC Jitter描述,在32GT/s,CC Jitter Limits達0.15ps RMS,對實時示波器的測量精度提出了更高要求:

圖24 PCIExpress5.0規范對CC Jitter Limit的要求

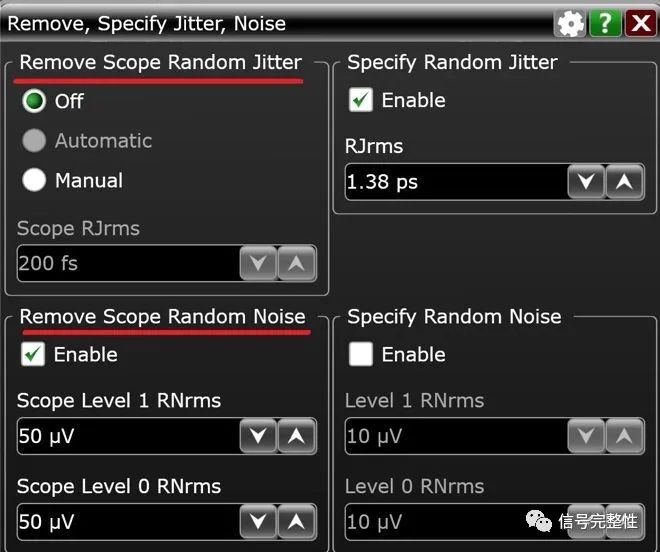

為了滿足這些標準和規范的最新要求,業界除了在算法上做出一些改進和提高外,Keysight公司在EZJIT Plus/Complete軟件里提供了去除示波器本身的隨機抖動和噪聲的選項,從而去除測量誤差提高測量精度。

圖25 EZJIT COMPLETE軟件提供去除示波器隨機抖動和噪聲功能

另外捕獲足夠時長的波形用于數據分析也是抖動測試中的一個關鍵。

因為足夠的波形數據和捕獲時長除了可以捕獲更多的時鐘周期或數據UI進行更準確的抖動分析外也意味著可以捕獲更低頻的抖動因為捕獲的整個波形周期更長,這也是示波器長存儲的重要價值之一。

因此在選擇和購買示波器的時候,推薦選擇具有更長存儲深度配置的產品。

以上談到了實時示波器的4個影響抖動測量精度的主要因素或指標,雖然抖動軟件的分析算法一直與時代同步進行提高和改進,但是在實際工作中盡量選擇更高精度的設備依然是獲得高精度的測量結果的最有力保障。

從抖動測試到相噪測試——實時示波器的新戰場

實時示波器因為其高采樣率下長存儲和重復單次采樣能力在抖動分析應用領域成為主力設備。隨著數據速率的持續提高,裕量的下降,比如前面提到的PCIE5.0規范中關于CC Jitter 的要求,僅從時域角度進行測量已經顯得捉衿見肘。

InfiniiVision 實時示波器 -

利用超快的波形捕獲率執行一般性日常調試,更快地捕獲毛刺信號

Infiniium 實時示波器 -

利用超高帶寬、超低本底噪聲和高 ENOB 的示波器,輕松獲得開發下一代技術時所需的信號完整性

另一方面隨著近幾年實時示波器的ADC位數從8bit向10bit全面升級,實時示波器的無雜散動態范圍(Spurious Free Dynamic Range)等指標得到了全面提高,典型如Keysight公司的 S和UXR系列實時示波器已經實現了從500MHz--8GHz和13--110GHz 硬件10bit ADC的全天候覆蓋,其本身的SFDR指標均非常優異。因此實時示波器也開始進入頻域指標測量領域,比如相位噪聲,Phase Noise。

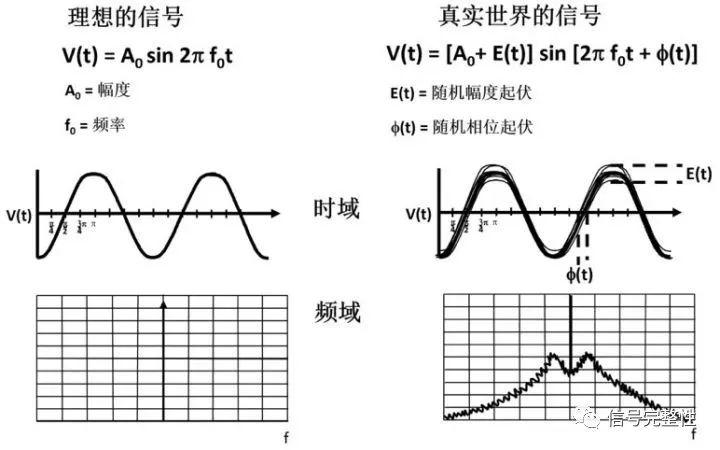

首先來看什么是相位噪聲?

在維基百科中,相位噪聲的定義是“時域不穩定性(抖動)導致波形在相位上發生快速、短期、隨機的波動,這種波動在頻域中的表現即為相位噪聲”。這一術語中的“噪聲”一詞告訴我們,它指的不是雜散或確定性波動。

定義中提到的“短期”是為了與確定時鐘源純凈度時所用的其他方法加以區別,例如以百萬分之幾(ppm)為單位的穩定度。它通常是以更大的時間長度進行測量,例如秒或分鐘。

圖26 理想與真實信號在時域和頻域的對比

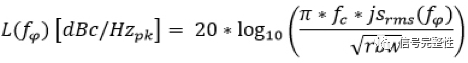

雖然有許多技術術語可以量化相位噪聲,但最常采用的指標之一是“單邊帶(SSB)相位噪聲”,L(f)。在數學上,美國國家標準與技術研究院(NIST)將L(f)定義為從載波的偏移頻率處的功率密度與載波信號的總功率之比,單位為dBc/Hz:

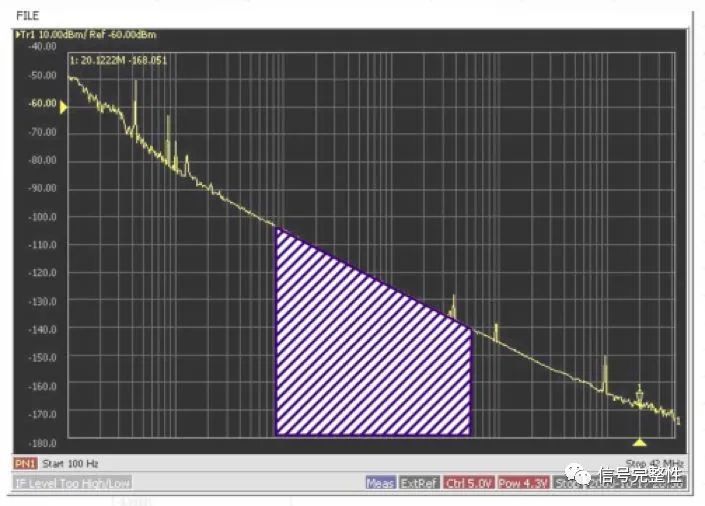

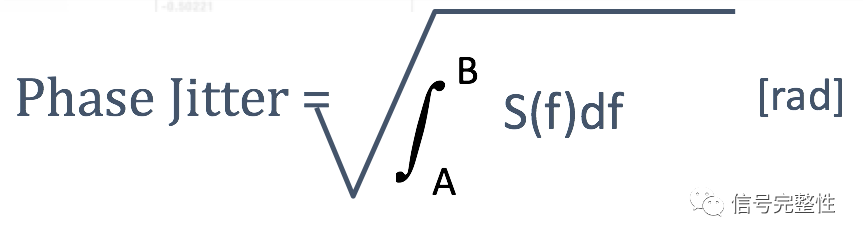

基于頻域相噪的測量結果可以再轉化為時域的相位抖動,這就是數字和時域研究人員感興趣的結果。如下圖示,相位抖動可以對陰影頻帶范圍內相噪進行積分得到。

圖27 基于相噪測量得到相位抖動

對于傳統的數字領域的公司和工程師而言,如果為了測試相位噪聲而專門進行相位噪聲測量儀器的投資,很明顯其性價比是不高的。因此發掘現有設備的潛能讓其發揮更大作用,也是一個不錯的選擇,而普遍存在的實時示波器當然是最佳的選擇。

相比其它頻域儀器測量方法,采用實時示波器進行相噪分析的優點除了節約投資外主要還有實時示波器可以測量方波時鐘信號或者帶SSC(擴頻時鐘)的時鐘信號相噪,尤其是SSC擴頻時鐘在高速串行數據標準如PCIExpress/USB等參考時鐘信號里是相當常見的。

另外采用實時示波器的方法可以測量100MHz以上的時鐘頻率偏移,而頻域儀器一般限定在100MHz范圍內。針對數字域常見的差分信號,示波器可以采用高阻探頭直接探測或者采用2個通道輸入再進行差分運算,無需額外的附件Balun(巴倫)。

當然實時示波器還可以直接測量傳遞到數據信號上的相位噪聲。實時示波器還有強大的數據存儲和記錄能力可以保存波形用于傳統的數字分析工具比如PCIExpress 標準的CLK Jitter Tool等。

總而言之,采用實時示波器進行相位噪聲的分析和測試,不僅可以發揮實時示波器的作用節約投資,而且針對頻域測量儀器在數字標準和信號上的不足提供了更多優點:

支持更廣泛信號類型

更廣泛的時鐘信號如方波、帶SSC時鐘、數據信號

更簡便豐富的連接方式無需Balun以及探頭

更輕松的電纜接入

更大的頻率偏移支持能力

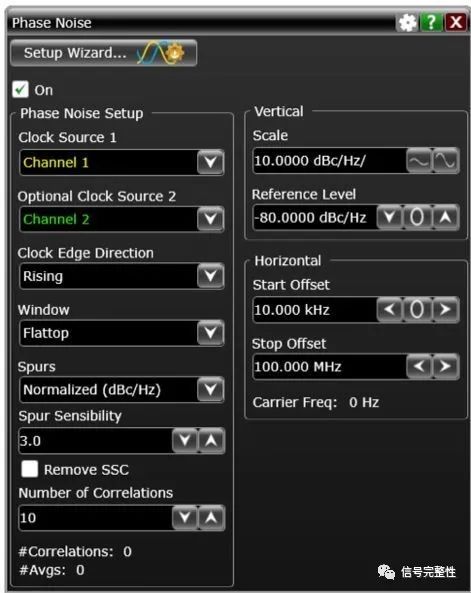

……Keysight公司在2018年推出了基于Infinium系列實時示波器的D9010/D9020JITA抖動/噪聲/相噪分析軟件,除了包含EZJIT Complete的全部功能外,還提供了功能強大的相噪測試功能:

將單邊帶(SSB)相位噪聲繪制為對數頻率與dBc / Hz

使用2個通道和交叉相關來降低寬帶測量噪聲

通過降低寬帶測量噪聲來測量差分時鐘的相位噪聲

測量帶擴頻調制(SSC)時鐘的相位噪聲

減少交叉相關時間間隔誤差(TIE)測量中的寬帶噪聲(RJ)

在相位噪聲圖上測量兩個頻率之間的積分抖動

使用InfiniiMax探頭測量電路中的時鐘/數據相位噪聲

圖28 D9010/D9020 JITA軟件相噪測試設置

圖29 D9010/9020 JITA 單邊帶相位(SSB)噪聲測量結果

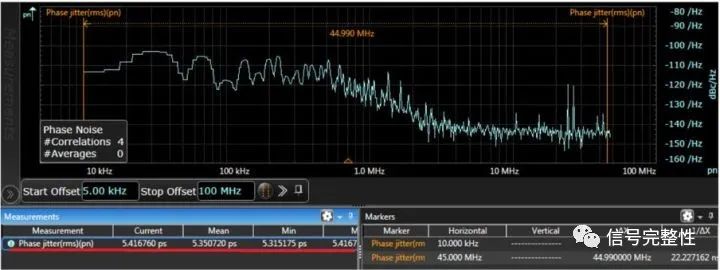

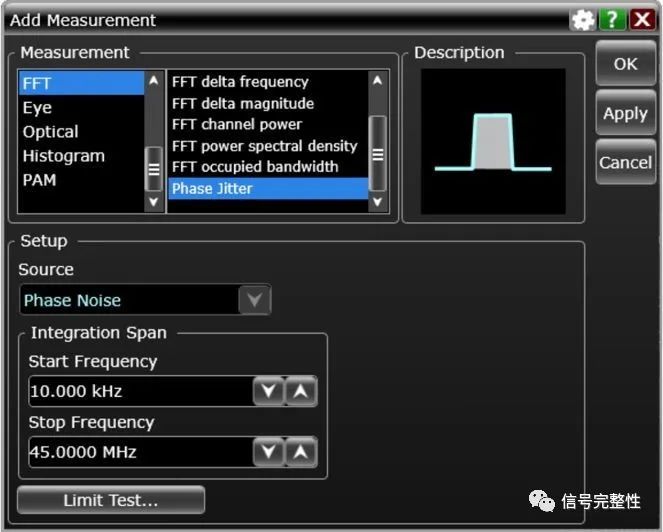

基于相噪測量結果,然后在測量菜單下選擇FFT →Phase Jitter項目,參照下圖,選擇感興趣的頻帶,就可以得到Phase Jitter測量結果,如下圖示:

圖30 基于相噪測試結果的相位抖動測量

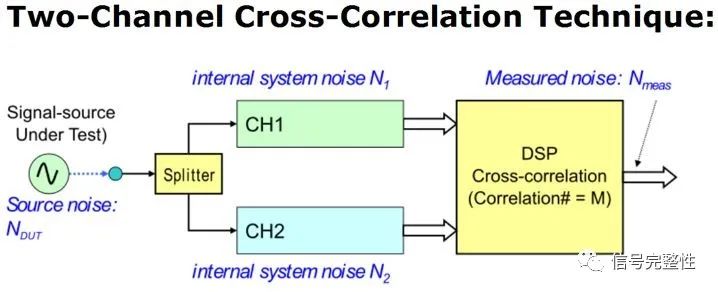

為了獲得更精確的測量結果,相噪測試時還可以進行2-通道互相關降低儀器本底噪聲。時鐘信號通過功分分成兩個信號輸入到示波器的兩個通道,可以執行雙通道互相關技術。

時鐘信號可以是單端或差分(如果差分信號則建議分別針對正負信號經過功分后用SMA電纜接入1-3或2-4通道)。然后在通道上執行互相關操作,如下圖30所示。

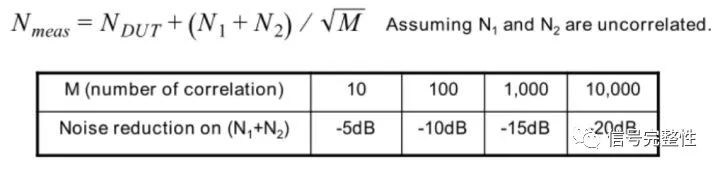

通過每個通道的DUT噪聲是相干的并且不受互相關的影響,而每個通道產生的內部噪聲是不相干的,并且以或者的速率通過互相關運算減少,其中M是進行波形相關運算的采集數量,采用的波形相關運算數量越大則進行平均運算時的速度越慢。

圖31 雙通道互相關降低儀器本底噪聲示意

圖32 相關運算數量和降低噪聲性能對應關系

相噪測試為實時示波器進入頻域測量打開了另一扇窗戶,尤其是針對數字和時域信號日益增長的頻域測試需求。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19178瀏覽量

229200 -

示波器

+關注

關注

113文章

6203瀏覽量

184545 -

抖動

+關注

關注

1文章

69瀏覽量

18847 -

數字電路

+關注

關注

193文章

1601瀏覽量

80511 -

抖動測試

+關注

關注

0文章

4瀏覽量

8799

原文標題:抖動與抖動測試

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

射頻知識——抖動和相位噪聲

抖動的基礎知識

抖動與抖動測試的基礎知識

抖動與抖動測試的基礎知識

評論