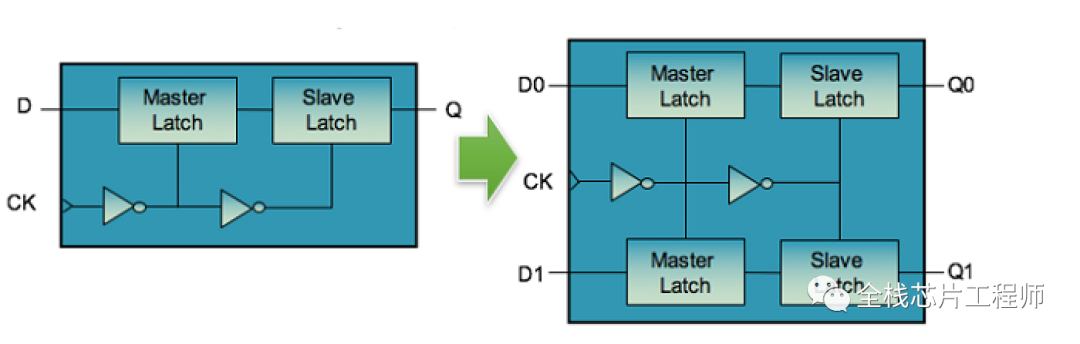

所謂multi-bit cell,可以理解成把多個完全相同的cell合并在一個cell里,如下圖所示,集成2bit的multi-bit cell的clock inverter是共享的,那么可以節省2個clock inverter的面積、功耗。

同時由于flip-flop數量減少,時鐘互聯線也減少,即減少了clock net length、capacitance、clock inverter更利于總功耗的降低。

有一點非常重要,MBFF對SBFF的合并使用目的是降低功耗,但是前提是保證timing,若timing不滿足,MBFF是應該被要求拆分成SBFF,SBFF更方便resize、move等操作。

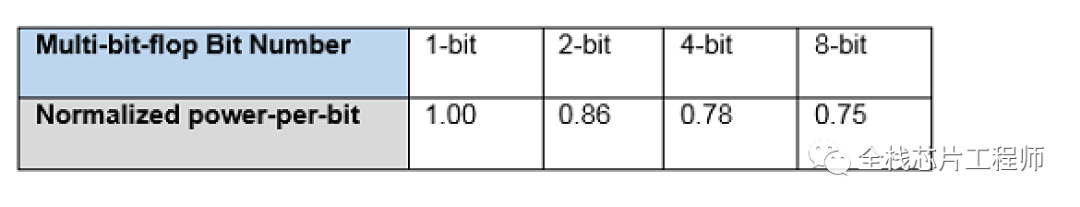

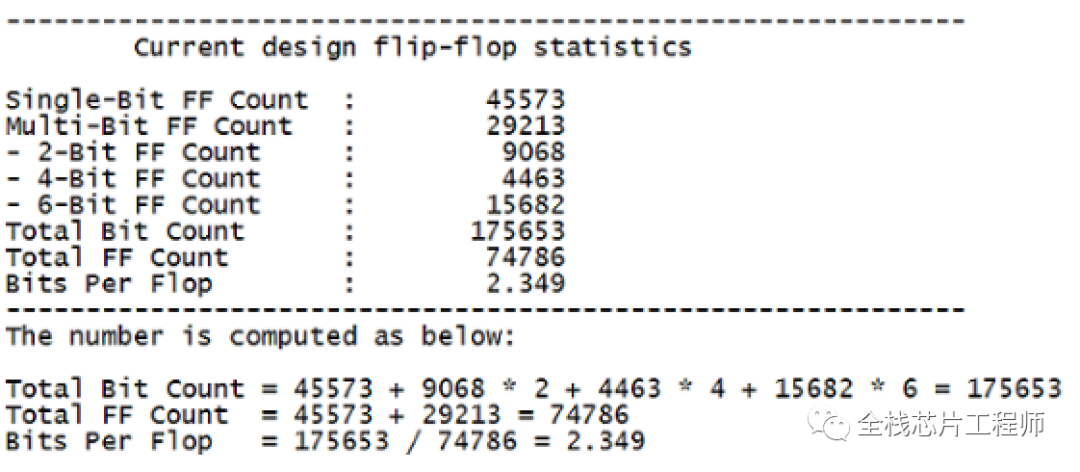

芯片功耗很大一部分在時鐘樹上,通過multi-bit cell技術我們可以獲得如下圖所示的功耗改觀:

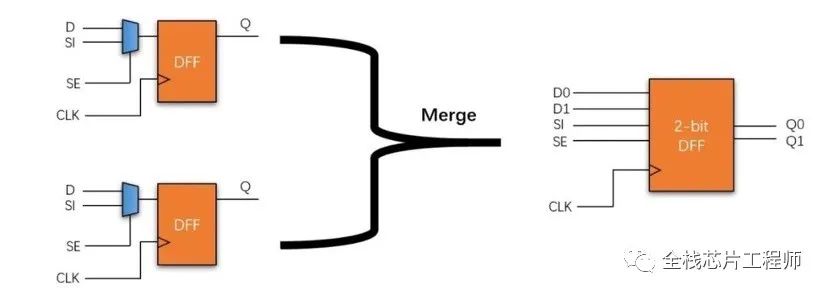

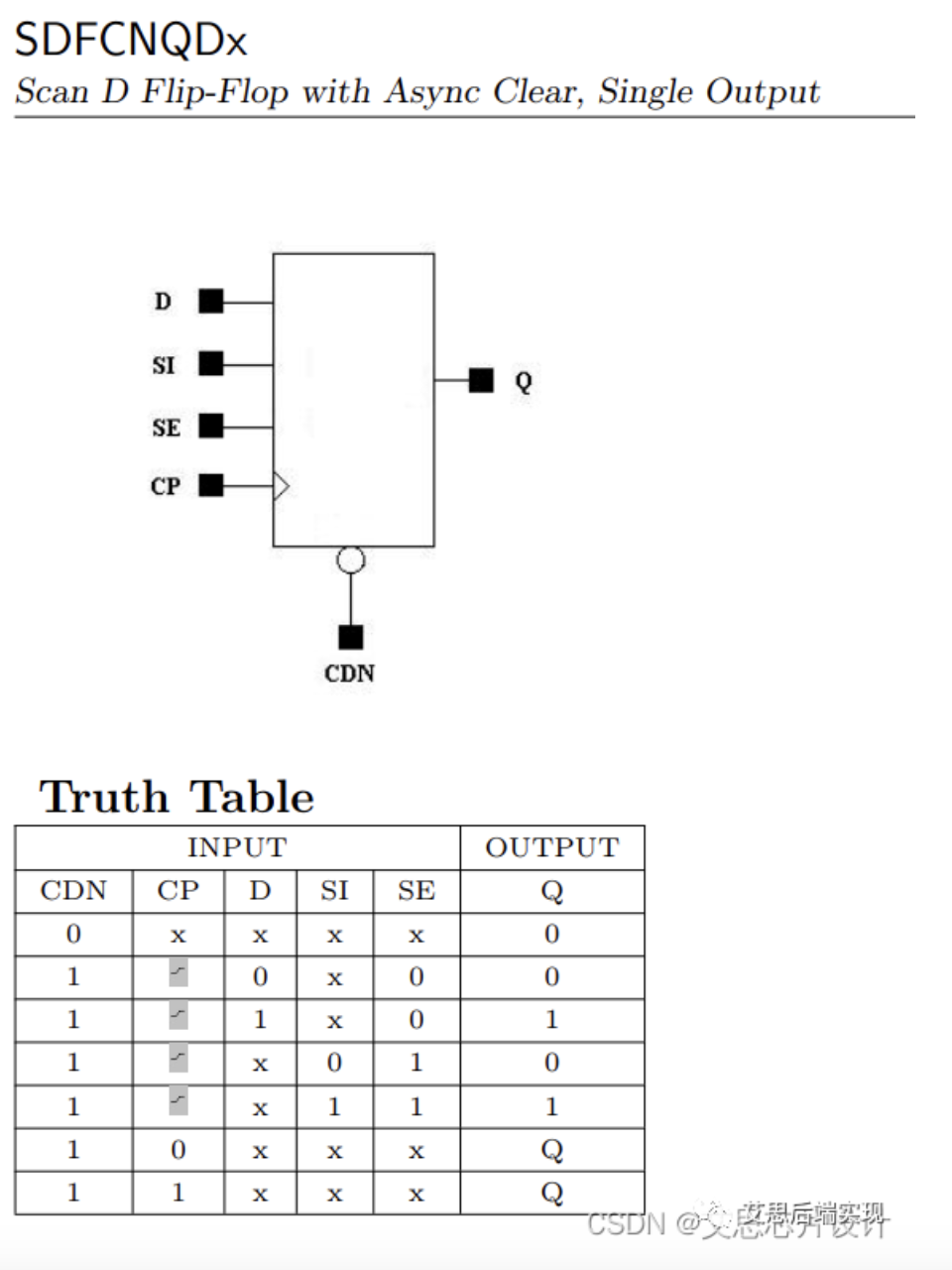

此外,通常scan DFF由于帶了scan mux電路,其面積會更大,而Multi-bit flip-flop (MBFF)合并單bit寄存器后,可以更明顯降低面積,以scan DFF為例,single bit 和multi bit的邏輯關系一般如下:

在晶體管級別的版圖設計過程中,會采用優化晶體管連接,晶體管共用等手段來節約面積,因此multi-bit cell比同等bit數目的single-bit cell的版圖面積總和要小一些。假設一個1-bit DFF的面積為?,那么一個2-bit DFF的面積一般會比?

?小一些,4-bit DFF的面積會比?

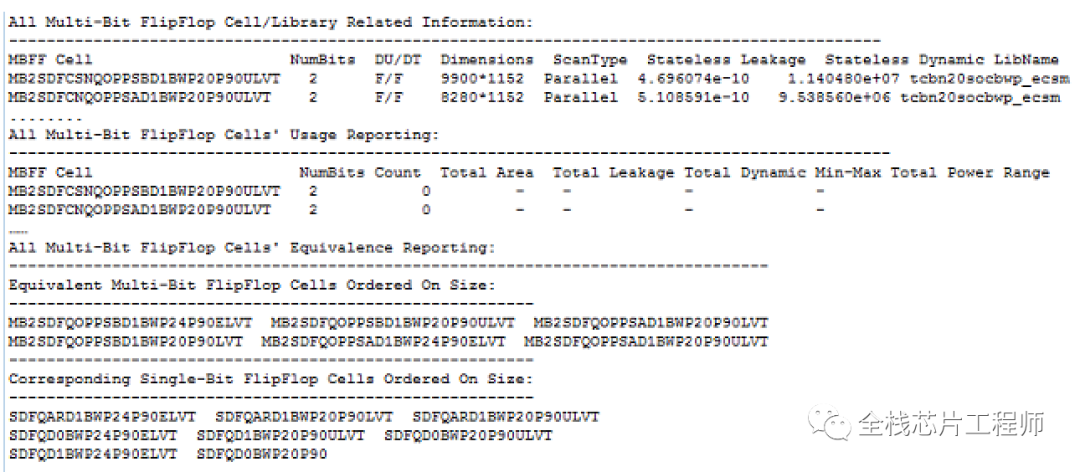

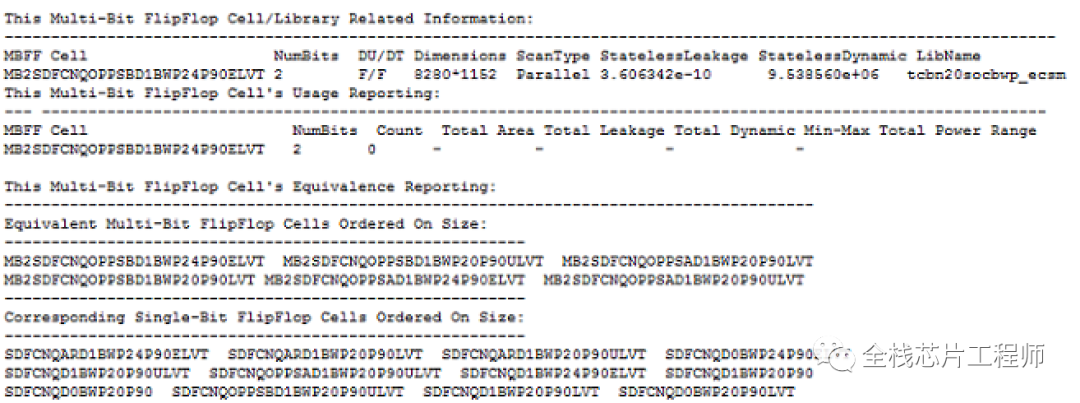

?小更多。 在Cadence INNOVUS中可以用如下命令查看MBFF信息:

reportMultiBitFFs -all

reportMultiBitFFs -statistics

reportMultiBitFFs -cell MB2SDFCNQOPPSBD1BWP24P90ELVT

MBFF結構在功耗上帶來的好處主要體現在以下幾個方面,整體而言,就是減少了clock net length、capacitance、clock inverter。

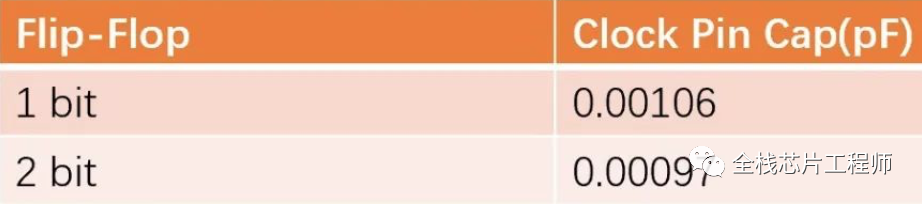

1)clock pin capacitance減少從而降低clock switching power

由下圖可知,雖然2bit MBFF較1bit flip-flop的clock pin cap改觀不大,但當design中有大量multi-bit DFF來替代single-bit DFF時,DFF數量大量降低,芯片時鐘樹上整體pin cap的下降是非常明顯的。cap越小switching power也越小,動態功耗降低。

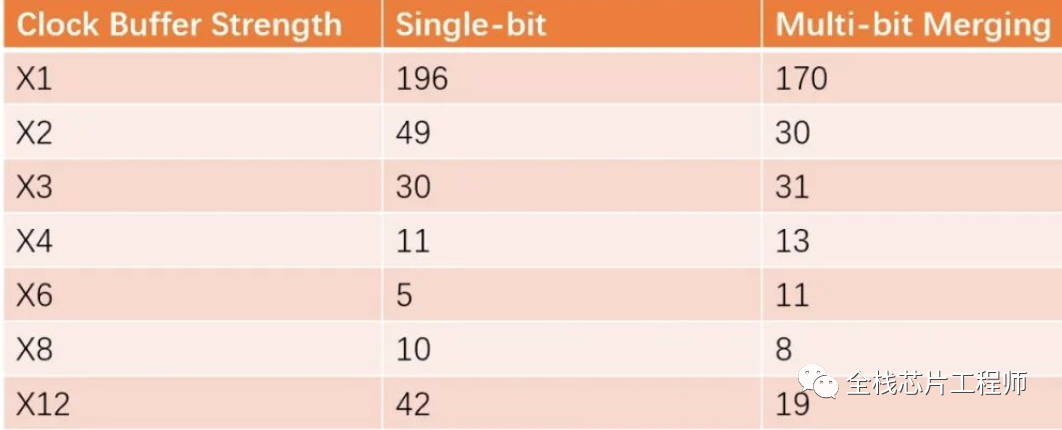

2)時鐘樹buffer數量減少,降低switching和leakage power

由于multi-bit DFF中每個DFF的clock pin cap相對于single-bit DFF有一些減小,那么在multi-bit design中一個相同的buffer可以驅動更多的MDFF,當然最主要還是DFF數量的減少,從而顯著減少時鐘樹上的buffer數量和面積,進一步降低時鐘樹上的功耗。

3)時鐘樹繞線資源減少,時鐘樹寄生RC從而降低dynamic power

MBFF大量使用時,相對于single-bit design來說,芯片standard cell數量大幅下降,而且在很多時候DFF的擺放也可能會更加集中,時鐘樹繞線將節省大量走線資源,進而減少整個時鐘網絡的寄生RC。

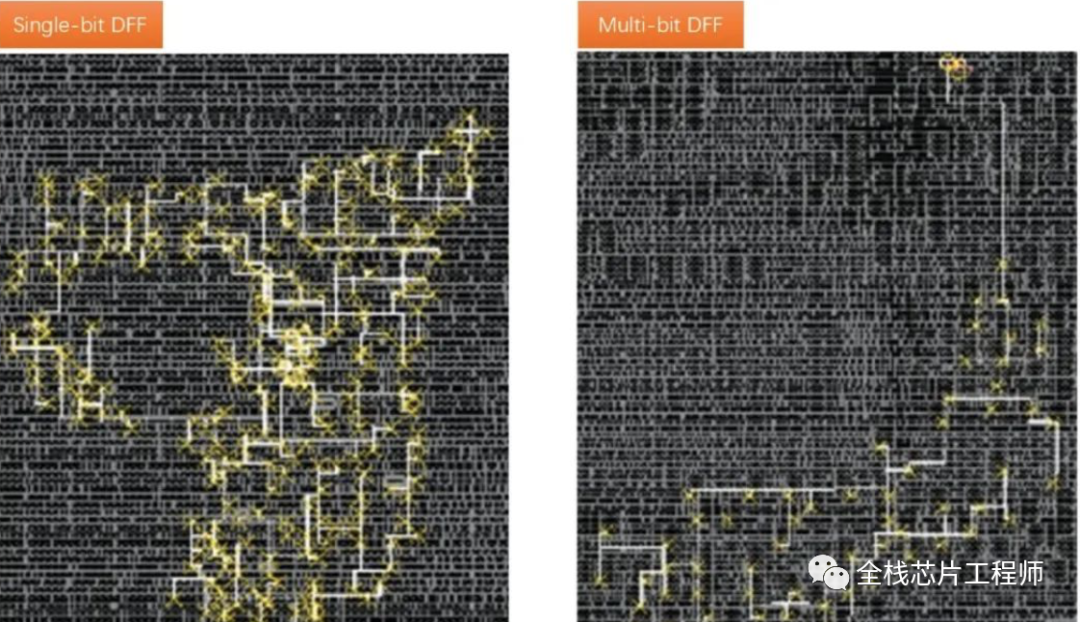

下圖展示了single-bit DFF與multi-bit DFF的繞線差異,可以看出右側的MBFF繞線明顯更少,時鐘整體的寄生RC得到減少,從而降低功耗。

盡管multi-bit有以上諸多優點,但是在實際應用中并不總能得到最好的結果。

其主要原因在于以下幾個方面:

a) single-bit到multi-bit的轉化有諸多條件限制,很多時候design實際的multi-bit cell比率不高。

b) multi-bit cell擺放不合理可能會引起congestion問題、timing問題,反而會增加更多的組合邏輯的power從而抵消clock tree上帶來的功耗降低的效果。

比如,2bitsingle-bitDFF本來被place在不同位置,若合同為2bit的multi-bit DFF后,routing連線可能反而更長,增加了路徑延遲,工具會采用buffering、sizing的優化方式優化時序,若依然不能滿足timing,那么multi-bit cell不如拆分成single-bit cell,因為single-bit cell可以更方便resize、move。

c) IR/EM方面的考慮可能會故意讓multi-bit cell互相擺放的遠一些,從而無法達到減少clock net length寄生RC從而降低功耗的效果。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5325瀏覽量

120053 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

時鐘樹

+關注

關注

0文章

53瀏覽量

10732 -

dff

+關注

關注

0文章

26瀏覽量

3400

原文標題:低功耗設計之Multi-Bit Cell

文章出處:【微信號:ExASIC,微信公眾號:ExASIC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

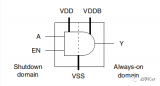

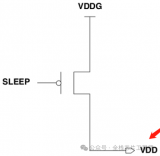

低功耗isolation cell設計

什么是Isolation Cell?低功耗設計基礎—Isolation Cell

STM32CubeMX低功耗模式簡介

STM32CubeMX低功耗模式簡介

STM32之待機喚醒低功耗模式簡介

ZXSC300-SINGLE OR MULTI CELL L

電子知識大全之樹電運行低功耗電路簡介

Multi-bit Flip Flop(MBFF)修復技巧

芯片設計里的Multi-Bit FF探究

isolation cell的低功耗設計

低功耗設計之multi-bit cell技術簡介

低功耗設計之multi-bit cell技術簡介

評論