近年來(lái),基于SPICE的模擬器的仿真結(jié)果已經(jīng)非常接近于實(shí)際特性。在某些情況下,將其作為一種現(xiàn)實(shí)的理想特性,調(diào)整實(shí)際的電路特性并使之接近這種理想特性,是非常“好用”的工具。然而,某些分析算法、條件設(shè)置、器件模型,并非沒(méi)有收斂性或穩(wěn)定性方面的課題。更好地了解仿真的收斂性和穩(wěn)定性課題,有助于更有效地利用仿真這個(gè)工具。

SPICE仿真的收斂性與穩(wěn)定性

所謂仿真中的收斂性問(wèn)題,是指即使執(zhí)行了程序也不開(kāi)始計(jì)算、中途停止等問(wèn)題,導(dǎo)致即使微小的條件變更也能引發(fā)結(jié)果很大的變化、出現(xiàn)不應(yīng)該出現(xiàn)的結(jié)果等。簡(jiǎn)而言之,就是分析錯(cuò)誤和結(jié)果不穩(wěn)定。

其原因有幾種,在這里以“器件模型”這種原因?yàn)槔齺?lái)說(shuō)明。下面是串聯(lián)連接的電阻和二極管的I-V(電流-電壓)特性,與電阻這樣的電流和電壓簡(jiǎn)單成正比的線性器件相比,二極管這樣的非線性器件的仿真會(huì)更復(fù)雜。可能任何人都可以輕松地創(chuàng)建電阻I-V特性的計(jì)算公式,而二極管正向特性的公式恐怕就沒(méi)有那么簡(jiǎn)單了。在下面的示例中,使用SPICE仿真中眾所周知的牛頓法,介紹一種通過(guò)不斷迭代來(lái)獲得負(fù)載線和非線性負(fù)載(在這里為二極管)的交點(diǎn)—工作點(diǎn)的近似解的方法。這種器件模型的特性有時(shí)是不連續(xù)的,在具有變曲點(diǎn)等較復(fù)雜的特性情況下,有時(shí)會(huì)出現(xiàn)如右圖所示的“不應(yīng)該出現(xiàn)的”不收斂的結(jié)果。

收斂性和穩(wěn)定性較差時(shí)的處理方法

收斂性和穩(wěn)定性較差時(shí),有幾種處理方法。不同的模擬器其處理方法也不同,下面的方法請(qǐng)理解為其中一個(gè)示例。模擬器的設(shè)置項(xiàng)目中,有收斂性和穩(wěn)定性相關(guān)的項(xiàng)目,試著更改這些項(xiàng)目。在本例中,算法有三個(gè)選項(xiàng),我們將嘗試更改現(xiàn)有的選項(xiàng)。另外,也將嘗試更改精度和誤差等收斂條件。

①嘗試將算法更改為Gear

?trapezoidal(梯形法):計(jì)算速度和精度高,但收斂性方面表現(xiàn)較差。

?modified trap(梯形法改進(jìn)版):改善了梯形法的收斂性。

?Gear(預(yù)測(cè)校正法):容易收斂,但在計(jì)算速度和精度方面表現(xiàn)較差。

②放寬收斂條件

?Abstol:電流精度。圖例為1pA以內(nèi)。

?Reltol:相對(duì)誤差。圖例為0.1%以內(nèi)。

?Chgtol:電荷精度。圖例為10fC以內(nèi)。

?Vlottol:電壓精度。圖例為1uV以內(nèi)。

當(dāng)提高精度(降低值)時(shí),計(jì)算速度會(huì)下降,但收斂性會(huì)改善。

③設(shè)置Maximum Timestep。這一欄空白也可以執(zhí)行仿真,但可能會(huì)使Timestep取值過(guò)大而出錯(cuò)。

④當(dāng)Tran(瞬態(tài)分析)的第一個(gè)DC點(diǎn)的收斂較差時(shí),設(shè)置為“skip dc”可有效改善這個(gè)問(wèn)題。

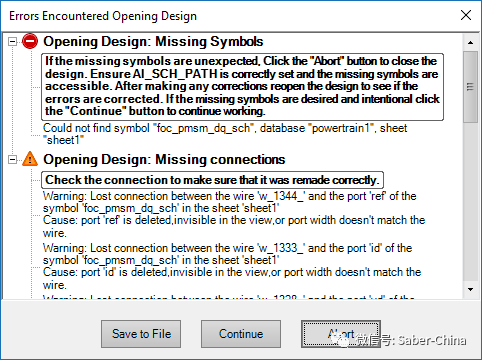

上述方法是可以在用戶處通過(guò)更改模擬器的設(shè)置等,來(lái)規(guī)避收斂和穩(wěn)定性問(wèn)題時(shí)的方法。但其中也有可能是器件模型本身具有缺陷,在這種情況下,是很難在用戶處解決仿真錯(cuò)誤的。

如果需要?jiǎng)?chuàng)建一個(gè)器件模型,最重要的是要?jiǎng)?chuàng)建一個(gè)比起精度更重視收斂性和穩(wěn)定性的、能運(yùn)行的器件模型。

電子電路仿真基礎(chǔ):SPICE仿真的收斂性與穩(wěn)定性

電子電路仿真基礎(chǔ):SPICE仿真的收斂性與穩(wěn)定性

評(píng)論