我們深度解釋了這種魔法的本質,以及如何在模擬芯片設計的不同階段,根據常見的EDA工具特性和原理,從計算角度幫助模擬工程師更高效地完成吟唱施法。

芯片設計五部曲之一 | 聲光魔法師——模擬IC

第二集:數字IC

假如我們想要錄制一段聲音,模擬信號的做法是把所有的聲音信息用一段連續變化的電磁波或電壓信號原原本本地記錄下來。而按照一定的規則將其轉換為一串二進制數0和1,然后用兩種狀態的信號來表示它們,這叫數字信號。

當聲音變大或變小了,模擬信號都會跟著變化,所以模擬信號有無數種狀態。狀態之間微妙的差異,需要人的經驗判斷,有點玄學的成分。

而數字信號永遠只有0和1兩種狀態,信號的轉換嚴格遵循邏輯關系,一個輸出對應唯一確定的結果,程序完全依照輸出指令執行,這是科學。

數字IC設計工程師的設計目標:在PPA(Power、Performance、Area)三個指標上追求完美的平衡。

怎么玩轉這門科學?

這,是一種藝術。

今天,我們就從資源需求、并行特征、數據敏感度等角度展開聊聊在數字芯片設計各階段,如何利用不同EDA工具的特點,讓數字芯片的設計研發效率獲得顯著提升。

和模擬芯片相呼應,這篇還是從計算角度出發,至于調度/管理/數據/協同/CAD等視角,會在后面的文章里體現~(比如第三集

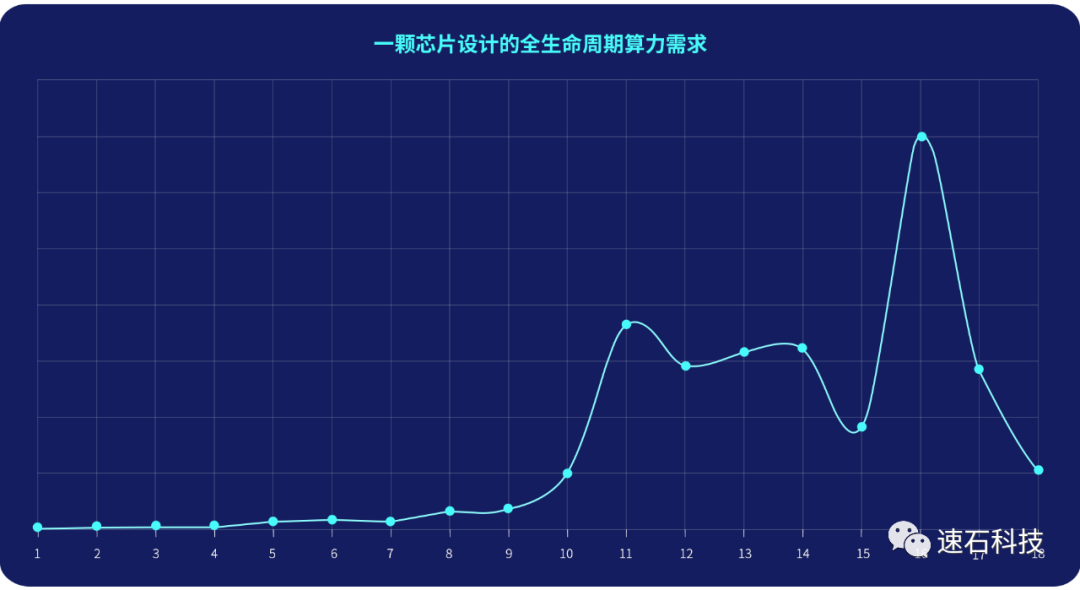

和模擬相比,數字芯片需要使用EDA工具的場景更多,IC工程師們對于計算機的使用天然比較親近。但就跟《解密一顆芯片設計的全生命周期算力需求》一樣,只負責某項工作的研發可能不關心,或者只了解自己的這部分,IT對業務所知有限,也不一定清楚。除非有大佬坐鎮,大多數公司的日常大概是以拍腦袋經驗論為主。

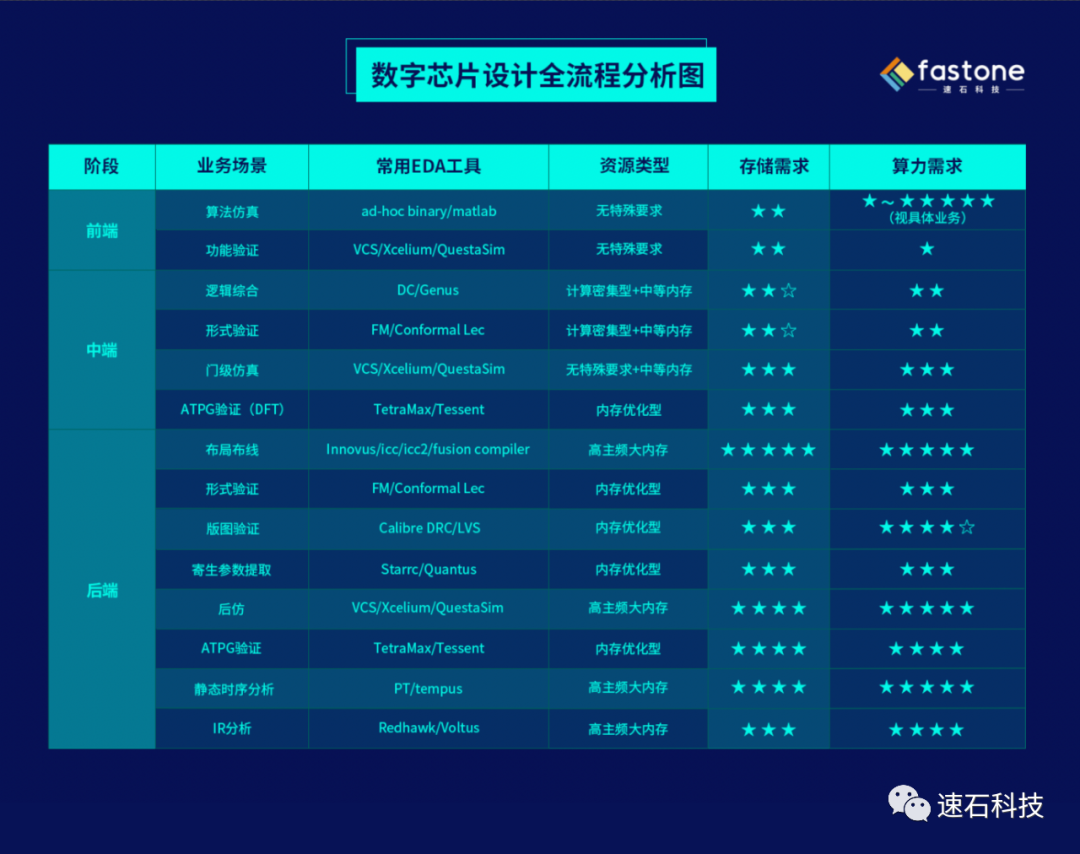

我們先來看一下大畫面,數字芯片設計全流程分析圖:

01

數字前端:前端設計/驗證

這一階段包含了規格制定、架構設計、RTL編碼等步驟。 數字前端算法仿真和功能驗證場景有大量中小任務并行,這一階段,對于資源類型和用量通常無特殊需求。 不過需注意若大量使用現有IP通常沒有算法仿真這一步。而且每家公司業務不同,算法仿真需求量差異非常大(下一集主角就是ta)。

02

數字中端:邏輯綜合與DFT實現

這一階段可分為邏輯綜合、形式驗證、門級仿真、ATPG驗證等業務場景。 數字中端呈現單、多任務混合的特點,因為計算的輸入數據中包含門延遲信息,輸入數據變多,對內存的需求相比前端有一定增長。ATPG驗證建議內存優化型,其他三種場景更加偏計算密集型。

03

數字后端:物理實現

這一階段包括布局布線、形式驗證、版圖驗證、寄生參數提取、后仿、ATPG驗證、靜態時序分析和IR分析等業務場景。 數字后端基本都是多任務,由于包含版圖的寄生參數,信息量非常大,普遍需要大內存機器。其中,布局布線、后仿、靜態時序分析、IR分析的大任務數量非常多,對主頻也有要求,需要兼具高主頻和大內存的資源。

資源需求

后端>中端>前端,數字后端·真·資源黑洞

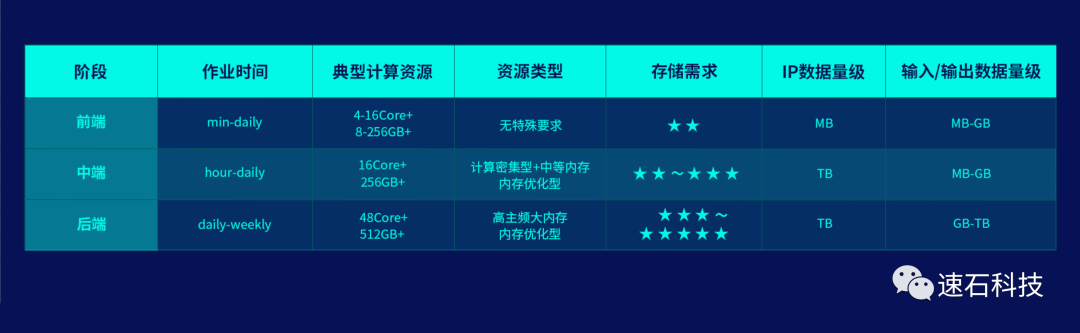

把數字IC設計前、中、后端三大階段進行資源需求對比。

可以看到無論是任務運算時間、所需計算資源、存儲需求還是IP與輸入數據量級上,數字前中后端形成了非常明顯的階梯結構,整體資源需求呈現前端<中端<后端的趨勢。 這是由三個階段的具體工作內容決定的:

數字前端,用RTL代碼將芯片架構師的設計寫出來,前端驗證也主要是針對RTL的功能進行驗證,偏邏輯功能。

數字中端,需要將RTL代碼綜合成網表并規劃、插入各種用于芯片測試的邏輯電路,需要加入Foundry廠提供的標準單元庫的工藝參數,驗證也到了邏輯門這一級。

數字后端負責芯片的物理實現,先將電路網表通過自動布局布線畫成版圖,再進行寄生參數提取,創建一個可以精確模擬數字電路響應的模型,這一階段會加入版圖的寄生參數。

從代碼到邏輯門電路再到物理層,隨著階段的演進,信息量逐級遞增,計算時所需消耗的資源量也隨之增加。

而在28nm以及更先進制程下,包含的工藝參數更多,電路更復雜,前中后端每一階段的信息量級還會被進一步放大。

哪怕前端RTL基本一致,中端和后端因為Foundry廠工藝參數更多更復雜,同樣的代碼計算量也是更大的。

換個思路,我們舉個栗子。

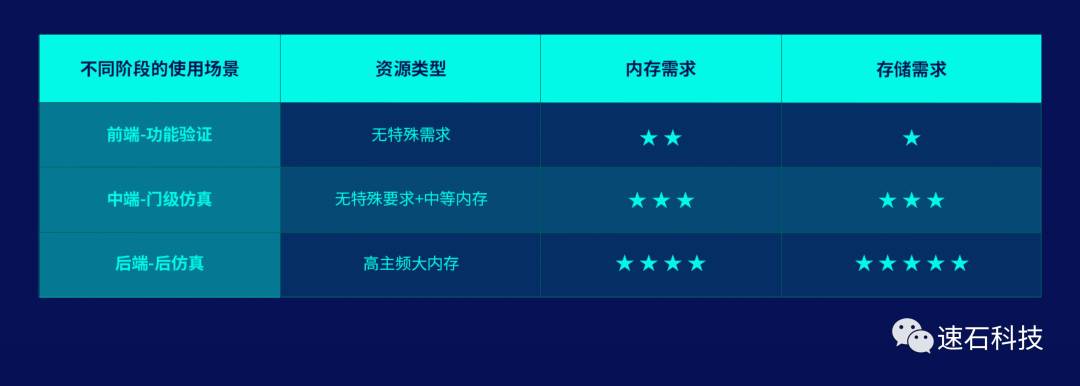

通過一個在數字前中后端都會出場的EDA工具來看看三大階段的資源需求。

VCS的主要作用是將Verilog HDL(一種硬件描述語言)轉成C語言,編譯出來并執行。作為一個翻譯官,ta的工作量取決于雙方對話的頻率,以及需要翻譯的文本量。

VCS在前端的功能驗證、中端的門級仿真、后端仿真中都有出場,在不同階段對任務資源的需求完全不同:

從前端到中端再到后端,雖然VCS的工作性質沒變,但整體來說,消耗的資源越來越多了。

綜上,數字后端設計與驗證環節相比中端和前端資源需求更高、運算時間更長、數據量更大,往往會占據整個項目周期資源需求量的50%以上。

下圖是我們某客戶全生命周期月度算力實際用量曲線,可以看到后端的波峰相當明顯,詳情戳:解密一顆芯片設計的全生命周期算力需求

這也就意味著,數字后端對IC設計公司的壓力相當大,能否在這一階段獲取充足的資源,是提升研發效率、保障項目進度的關鍵。

典型并行場景

靜態時序驗證&版圖驗證

并行度是我們評估任務能否通過分布式計算完成,提升效率的標準之一。 這里涉及到兩個重要的判斷標準:可拆分,互不干擾。 可拆分指的是,大任務可以分解為小任務,原任務目標不變。

互不干擾指的是,拆分為小任務之后,任務之間互相不干擾,可以不同步。

從前端到中端再到后端,任務數量越來越多。

任務的并行度決定了速度提升的空間。

靜態時序驗證:最常見且并行度較高

靜態時序驗證是最常見的設計場景之一,基本原理是檢查各信號通路上經過的門電路,然后累加門延遲,求取整個路徑的信號延遲。

沿信號通路求Delay Time的過程,就是沿信號通路不停做簡單加法。

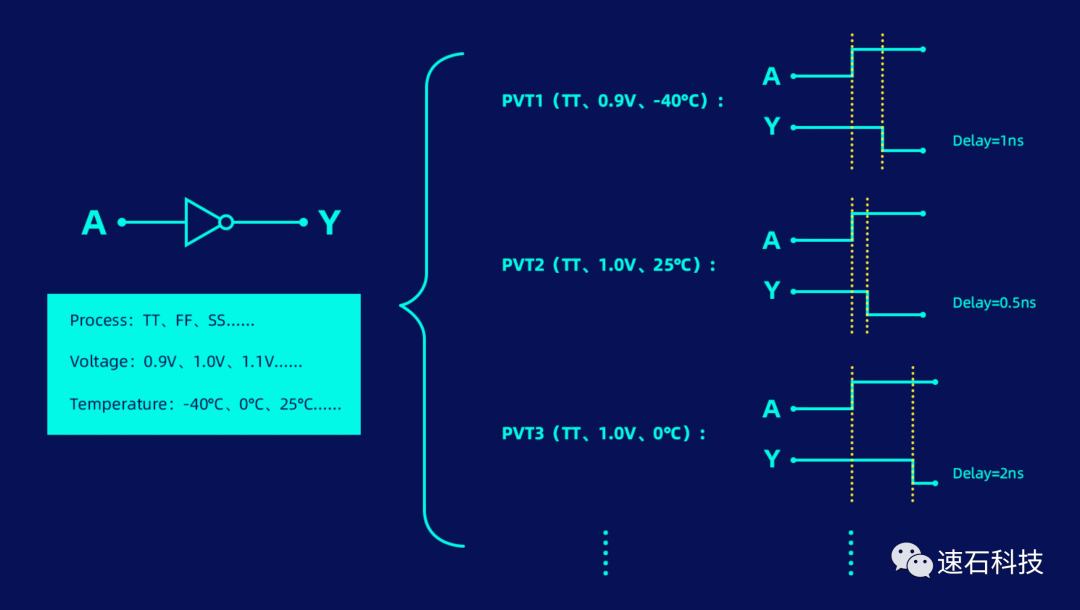

在靜態時序驗證過程中,有一個PVT的概念。

我們需要驗證邏輯門在不同的工藝(Process)、電壓(Voltage)、溫度(Temperature)條件下的延遲。

首先,列出可能的條件,如:

工藝:TT、FF、SS……

電壓:0.9V、1.0V、1.1V……

溫度:-40°C、0°C、25°C……

隨后,窮舉每一種可能性,如:

PVT1=TT、0.9V、-40°C

PVT2=TT、1.0V、25°C

PVT3=TT、1.0V、0°C

……

最后,驗證邏輯門在每一種PVT條件下的延遲:

數字芯片中有著無數這樣的邏輯門,每一個PVT下,邏輯門都有對應的Delay Time,而P、V、T之間可以有很多種組合,就會有很多個Delay Time的情況需要驗證。

這一場景,天然適合暴力堆機器。

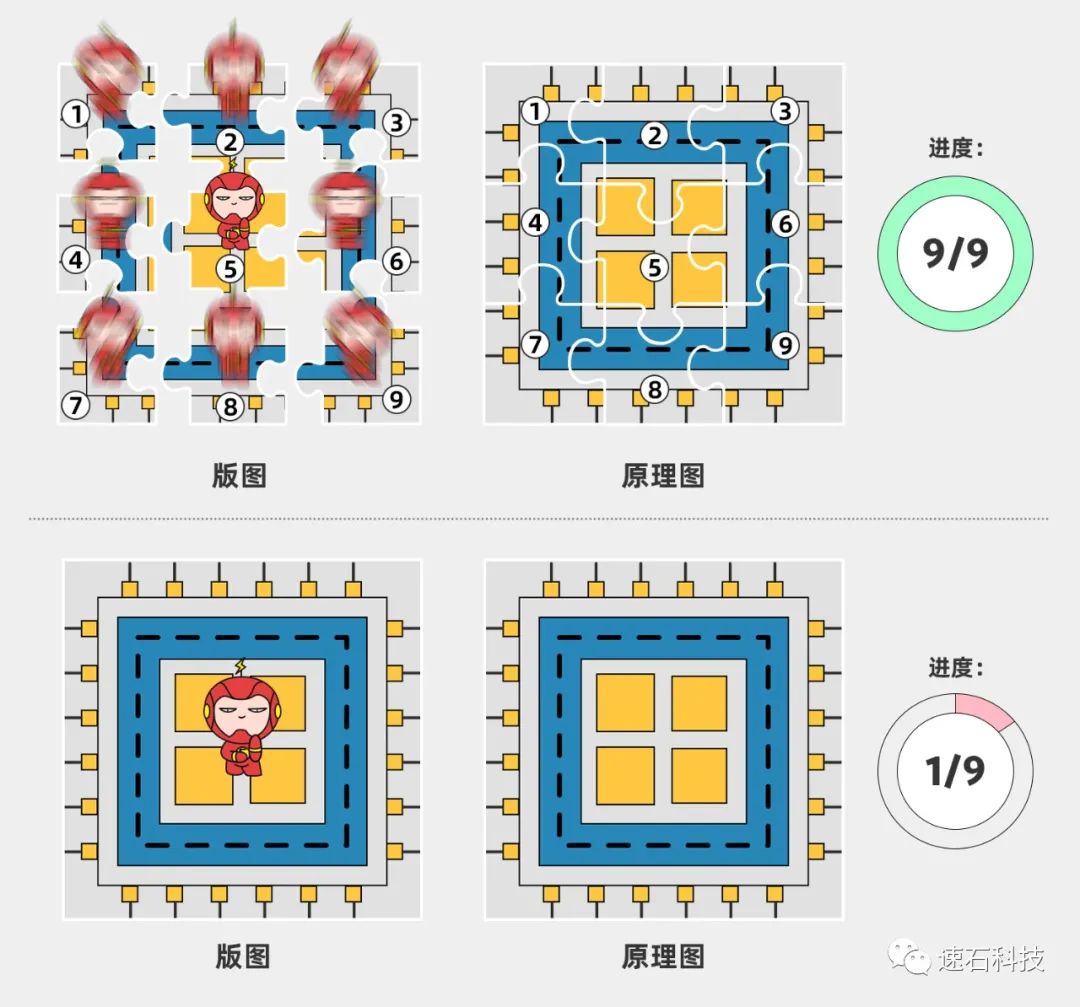

版圖驗證:最高并行度

模擬芯片和數字芯片,這一場景的原理一模一樣,使用的EDA工具也完全相同。

版圖驗證屬于檢查類任務,以模塊為單位,本質上是數據對比工作,重內存需求,子任務間沒有數據關聯,是數字芯片設計與驗證中并行度最高的場景。

這一階段很適合利用云上的內存優化型資源,使用“小F影分身術”(版圖分割術),通過暴力堆資源的方式快速完成任務。

關于版圖驗證,我們在《芯片設計五部曲之一 | 聲光魔法師——模擬IC》中有更詳細的說明。

數據敏感度

前端>中端>后端,但是不用擔心

我們按照數據敏感度從高到低的順序給各類設計數據排了個序: RTL數據 > IP、PDK和版圖> Netlist、Session、過程波形、歸檔數據和Report

好了,接下來我們看看這些數據都會出現在哪些階段:

數字前端有大量RTL代碼,甚至部分公司在此過程中還自己開發了IP,屬于數據安全等級最高的那一撥。許多公司都會嚴格管理這部分數據,設置一定的保密等級,甚至固定放在某幾臺機器上。

中端則涉及到部分的RTL代碼、IP和PDK數據,以及一些Netlist、Session和Report。

后端徹底告別了代碼,以IP、PDK、版圖和數據敏感度較低的數據為主。

如果你要做一款游戲,前端相當于游戲的源代碼,中端是詳細的角色形象設計稿,后端就是玩家拿到手的游戲光碟了。

前端泄密,恭喜你的對手達成“代碼級抄襲”;

中端泄密,別人能照著樣子把仿品做出來,但沒有源代碼參考,知其然不知其所以然;

后端泄密,等對方逆向明白,大半年時間也過去了,你的下一代產品已經在路上了。

值得一提的是,如果使用的是先進工藝,Foundry廠也會對IP/PDK數據有保密要求。

所以在選擇云上業務場景的時候,我們一般優先推薦數字后端先來。當然,會根據每家公司的實際情況進行具體分析。(以后會寫到,這次一定

那么,前端或者中端是不是就適合用云了呢?

甚至,在某些情況下,IC設計公司會面臨全部數據無論敏感度高低必須存放在本地的情況,比如一些高保密項目(軍工項目或國家重點項目),或者有點微妙的競爭關系,怎么辦?

我們有針對性的存算分離解決方案,歡迎來對號入座。

存算分離解決方案到底是什么?我們是如何實現的?掃描文末二維碼關注小F,對暗號“存算分離”搶先了解~

這里還有燧原科技的一手體驗,戳此先睹為快:【案例】燧原科技:芯片設計“存算分離”混合云實踐

關于數字IC設計,從不同設計階段的計算任務視角出發,我們總結了四點:

1、與模擬芯片相似,數字芯片三大階段的資源需求同樣呈現前期<中期<后期的趨勢,但數字芯片需要使用EDA工具的場景更多,整體資源需求更大;

2、版圖驗證并行度最高,靜態時序驗證出場率非常高且并行度很高,都適合用暴力堆機器的方式提高任務效率;

3、數字后端往往會占據整個項目周期資源需求量的50%以上,兼具資源需求高、計算時間長、數據量級大,數據敏感度相對低的特征,是提升數字芯片整體研發效率的關鍵;

4、數據敏感度高?必須放本地?沒關系,我們有解決辦法。

審核編輯:劉清

-

EDA工具

+關注

關注

4文章

265瀏覽量

31718 -

電磁波

+關注

關注

21文章

1444瀏覽量

53754 -

電壓信號

+關注

關注

0文章

213瀏覽量

13332 -

數字芯片

+關注

關注

1文章

108瀏覽量

18374

原文標題:干貨分享:數字芯片設計全流程分析

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

新手走向電子工程師或者硬件工程師具備條件?

高薪誠聘IC版圖工程師

資深工程師的進階之道

誠聘硬件工程師

全網首套且唯一一部全系列運控9點標定,幫助工程師快速完成機器視覺的職業進階。

網首套且唯一一部全系列運控9點標定課程,能幫助工程師快速完成機器視覺的職業進階。

模擬工程師招聘

FPGA工程師需要具備哪些技能?

IR新型SmartRectifier解決方案幫助工程師體驗高

幫助工程師解決三個難題的iSimTM Active Filt

簡化PMIC仿真設計 幫助工程師快速檢查電路

RS Components 提供多種解決方案,更好幫助工程師探索智能互聯工廠

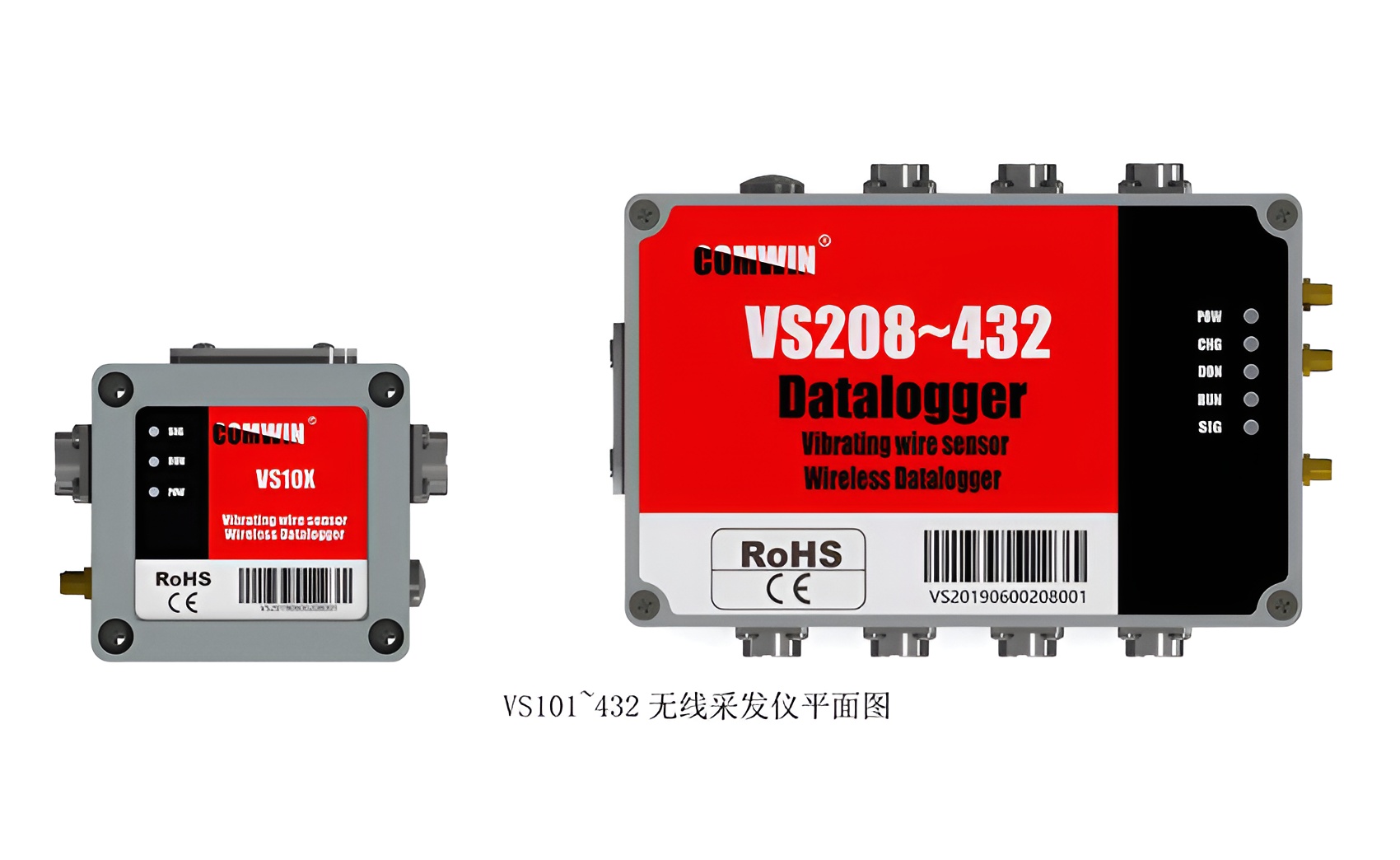

振弦采集儀:幫助工程師準確評估結構健康狀況的利器

如何在模擬芯片設計的不同階段幫助工程師完成吟唱施法

如何在模擬芯片設計的不同階段幫助工程師完成吟唱施法

評論