4

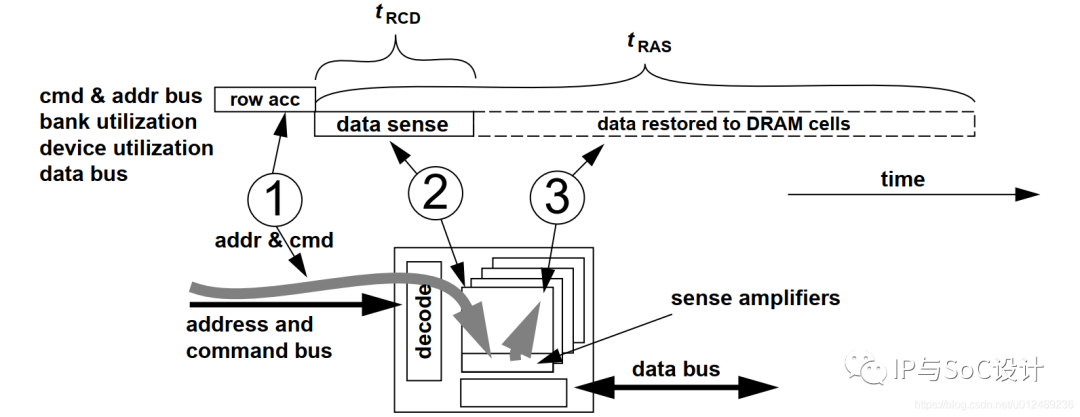

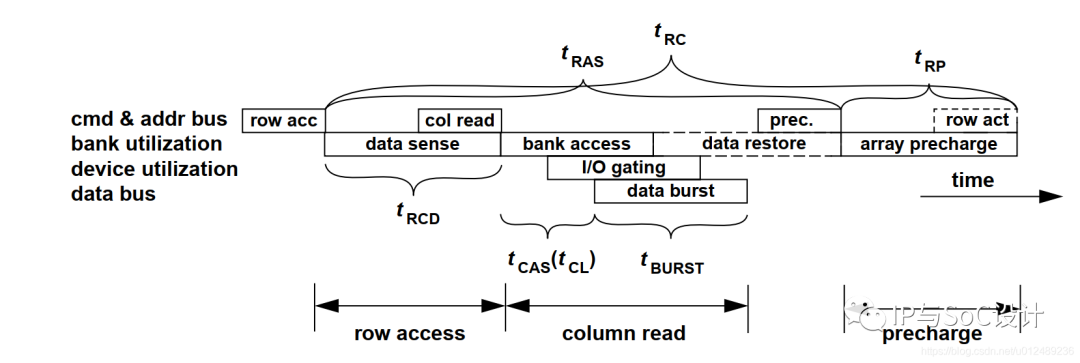

在進行數據的讀寫前,Controller 需要先發送 Row Active Command,打開 DRAM Memory Array 中的指定的 Row。Row Active Command 的時序如下圖所示:

tRCD:RAS-to-CAS Delay(tRCD),內存行地址傳輸到列地址的延遲時間。

Row Active Command 通過地址總線指明需要打開某一個 Bank 的某一個 Row。DRAM 在接收到該 Command 后,會打開該 Row 的 Wordline,將其存儲的數據讀取到 Sense Amplifiers 中,這一時間定義為 tRCD(RCD for Row Address to Column Address Delay)。DRAM 在完成 Row Sense 階段后,Controller 就可以發送 Read 或 Write Command 進行數據的讀寫了。這也意味著,Controller 在發送 Row Active Command 后,需要等待 tRCD 時間才能接著發送 Read 或者 Write Command 進行數據的讀寫。

tRAS: Row Active Time,內存行地址選通延遲

由于 DRAM 的特性,Row 中的數據在被讀取到 Sense Amplifiers 后,需要進行 Restore 的操作。Restore 操作可以和數據的讀取同時進行,即在這個階段,Controller 可能發送了 Read Command 進行數據讀取。

DRAM 接收到 Row Active Command 到完成 Row Restore 操作所需要的時間定義為 tRAS(RAS for Row Address Strobe)。

Controller 在發出一個 Row Active Command 后,必須要等待 tRAS 時間后,才可以發起另一次的 Precharge 和 Row Access。

4.2 Column Read Command

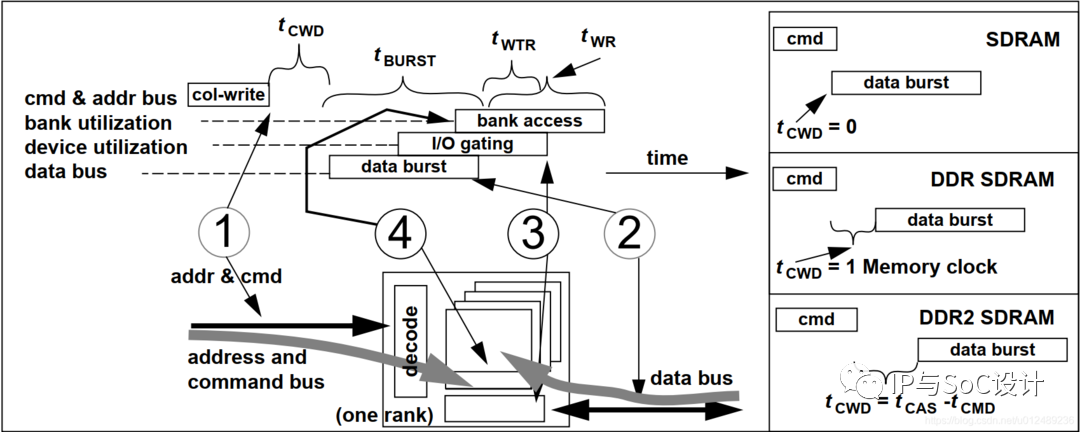

Controller 發送 Row Active Command 并等待 tRCD 時間后,再發送 Column Write Command 進行數據寫入。數據 Burst Length 為 8 時的 Column Write Command 時序如下圖所示:

tCWD/tCL/tCWL:內存CAS延遲時間

Column Write Command 通過地址總線 A[0:9] 指明需要寫入數據的 Column 的起始地址。Controller 在發送完 Write Command 后,需要等待 tCWD (CWD for Column Write Delay) 時間后,才可以發送待寫入的數據。tCWD 在一些描述中也稱為 tCWL(CWL for Column Write Latency)

tWR(WR for Write Recovery)

DRAM 接收完數據后,需要一定的時間將數據寫入到 DRAM Cells 中,這個時間定義為 tWR(WR for Write Recovery)。該值說明在一個激活的bank中完成有效的寫操作及預充電前,必須等待多少個時鐘周期。這段必須的時鐘周期用來確保在預充電發生前,寫緩沖中的數據可以被寫進內存單元中。同樣的,過低的tWD雖然提高了系統性能,但可能導致數據還未被正確寫入到內存單元中,就發生了預充電操作,會導致數據的丟失及損壞。

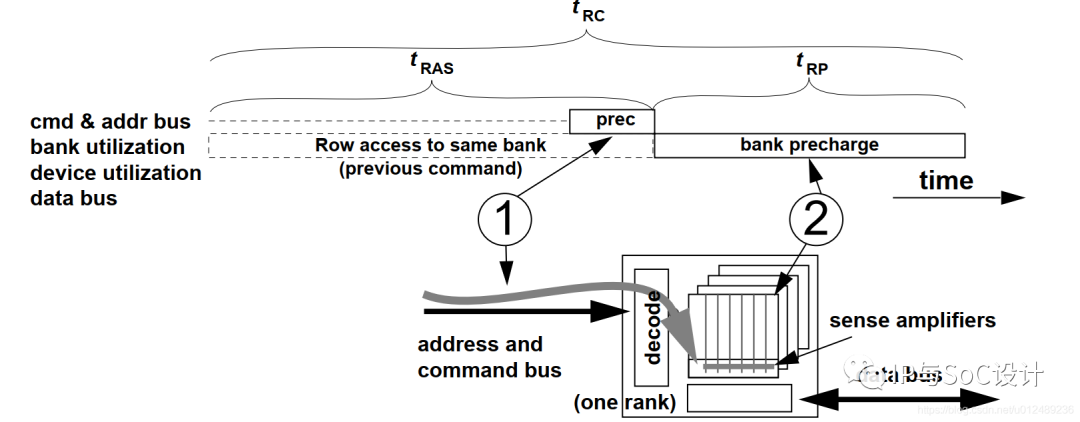

4.3 Precharge Command

要訪問 DRAM Cell 中的數據,需要先進行 Precharge 操作。相應地,在 Controller 發送 Row Active Command 訪問一個具體的 Row 前, Controller 需要發送 Precharge Command 對該 Row 所在的 Bank 進行 Precharge 操作。下面的時序圖描述了 Controller 訪問一個 Row 后,執行 Precharge,然后再訪問另一個 Row 的流程。

DRAM 執行 Precharge Command 所需要的時間定義為 tRP(RP for Row Precharge)。Controller 在發送一個 Row Active Command 后,需要等待 tRC(RC for Row Cycle)時間后,才能發送第二個 Row Active Command 進行另一個 Row 的訪問。

從時序圖上我們可以看到,tRC = tRAS + tRP,tRC 時間決定了訪問 DRAM 不同 Row 的性能。在實際的產品中,通常會通過降低 tRC 耗時或者在一個 Row Cycle 執行盡可能多數據讀寫等方式來優化性能。

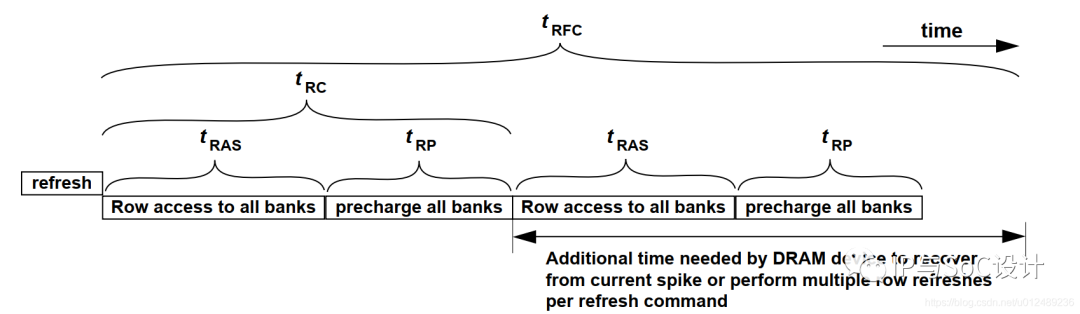

4.4 Row Refresh Command

一般情況下,為了保證 DRAM 數據的有效性,Controller 每隔 tREFI(REFI for Refresh Interval) 時間就需要發送一個 Row Refresh Command 給 DRAM,進行 Row 刷新操作。DRAM 在接收到 Row Refresh Command 后,會根據內部 Refresh Counter 的值,對所有 Bank 的一個或者多個 Row 進行刷新操作。

DRAM 刷新的操作與 Active + Precharge Command 組合類似,差別在于 Refresh Command 是對 DRAM 所有 Bank 同時進行操作的。下圖為 DRAM Row Refresh Command 的時序圖:

DRAM 完成刷新操作所需的時間定義為 tRFC(RFC for Refresh Cycle)。

tRFC 包含兩個部分的時間,一是完成刷新操作所需要的時間,由于 DRAM Refresh 是同時對所有 Bank 進行的,刷新操作會比單個 Row 的 Active + Precharge 操作需要更長的時間;tRFC 的另一部分時間則是為了降低平均功耗而引入的延時,DRAM Refresh 操作所消耗的電流會比單個 Row 的 Active + Precharge 操作要大的多,tRFC 中引入額外的時延可以限制 Refresh 操作的頻率。

4.5 Read Cycle

一個完整的 Burst Length 的 Read Cycle 如下圖所示:

下面是DDR常見的一些參數及定義如下:

上述的 DRAM Timing 中的一部分參數可以編程設定,例如 tCAS、tAL、Burst Length 等。這些參數通常是在 Host 初始化時,通過 Controller 發起 Load Mode Register Command 寫入到 DRAM 的 Mode Register 中。DRAM 完成初始化后,就會按照設定的參數運行。

5

性能分析

在學習完DDR的基本操作和時序參數之后,我們就看看性能的影響。當頻率和位寬固定后,帶寬也就不可更改,但是在內存的工作周期內,不可能總處于數據傳輸的狀態,因為要有命令、尋址等必要的過程。那么這些操作占用的時間越短,內存工作的效率就越高,性能也就越好。

對于我們來說,最好的方法是提高頻率,但是提高頻率會受多方面的影響,還有什么辦法提高內存訪問采取速度。

**·多通道: **現代內存控制器從北橋移入CPU內部,而內存控制器都可以同時操作多個通道。比如現在的筆記本開始支持雙通道、三通道,如果數據分布在不同通道的內存條上,內存控制器就可以不用管上面的這些延遲時序,同時可以讀取它們,速度可以增加兩倍,甚至三倍。

·交織方式(Interleaving): 同一塊內存分布到不同的通道中去,這樣無論Cache命中與否都可以同時存取,多通道的技術才能發揮更大的用處。

·超頻內存: 也就是提升DDR的頻率來增加速度

6

總結

對于DDR的讀寫以及一些時序參數的原理性知識后,下一步就進入到DDR的驅動調式,主要是對于一款控制器,我們該如何去調試DDR。其實對于DDR的調試,主要的讀寫的控制,都是由DDR的控制器完成了,我們主要是通過MRS模式/EMRS模式來完成對于DDR參數的配置,而對于MRS模式的使用,已經集成到DDR控制器中完成了,我們只需要根據控制器手冊配置相應的寄存器就可以完成對于DDR調試。

7

參考文檔

DRAM Memory-Access Protocol

DRAM Timing

本文轉自:https://blog.csdn.net/u012489236

-

DRAM

+關注

關注

40文章

2303瀏覽量

183319 -

晶體管

+關注

關注

77文章

9635瀏覽量

137858 -

bit

+關注

關注

0文章

48瀏覽量

31990

發布評論請先 登錄

相關推薦

淺談DDR內存技術原理2

淺談DDR內存技術原理2

評論