前言

HPC、AI、數據中心以及汽車自動化等應用對于高效能和高性能算力需求持續增長,單芯片系統實現方案從設計、實現、生產制造、可靠性等各個方面都遇到了嚴峻的技術挑戰。三維異構集成的3DIC chiplet設計,通過水平和垂直方向上的多芯片集成堆疊,使得芯片系統在性能、面積/體積、功耗、生產工藝、良率、成本、市場等諸多因素中獲得最佳平衡,經過十多年的發展目前已逐漸成為后摩爾時代新的技術趨勢。

3DIC異構集成設計分析全流程EDA平臺簡介

芯和3DIC異構集成設計分析全流程是一個適用于2.5D/3D系統級協同設計的統一平臺。從架構規劃、設計創建、物理實現,到分析驗證和系統簽核,它是一個高度集成、可擴展的平臺,具有靈活高效的工作流程環境,支持超大容量的系統級設計管理、架構探索和自動化布局布線,支持2D/3D交互式可視操作模式,同時集成了業界可信的golden簽核級分析工具,助力于實現產品最佳PPAC目標。

3DIC系統頂層的創建管理

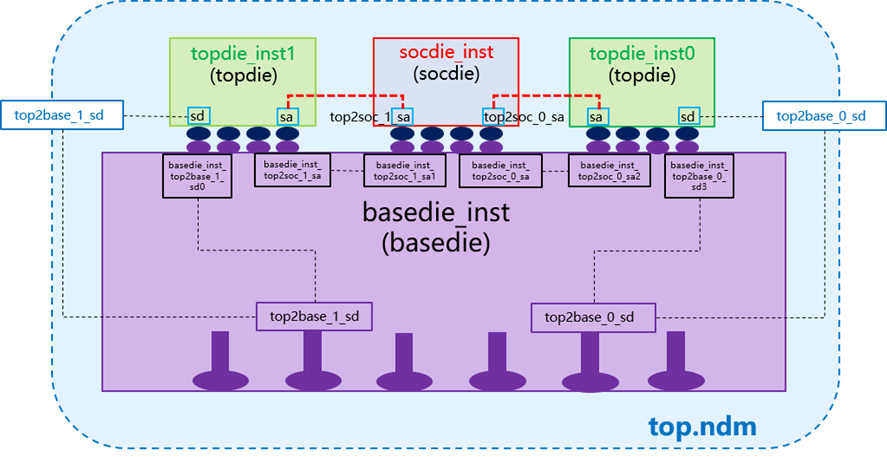

在系統架構方面,與傳統的2D架構不同,3DIC系統需要建立一個頂層結構來進行系統的設計實現和管理,管理來自于不同fab、不同工藝的不同設計庫,基于系統頂層來實現系統級的邏輯互連的定義,多芯片布局,以及系統級的各類仿真、分析、驗證工作等。

本文主要介紹如何使用該EDA平臺中的3DIC Compiler便捷高效地實現3DIC系統頂層的創建管理。

1. Die Design創建

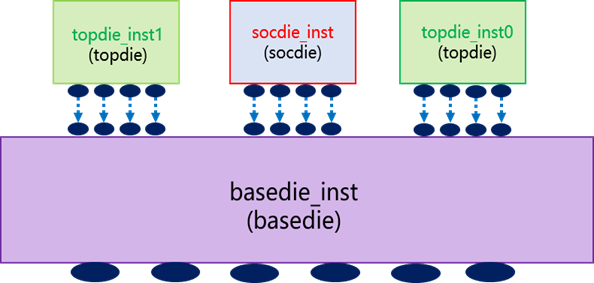

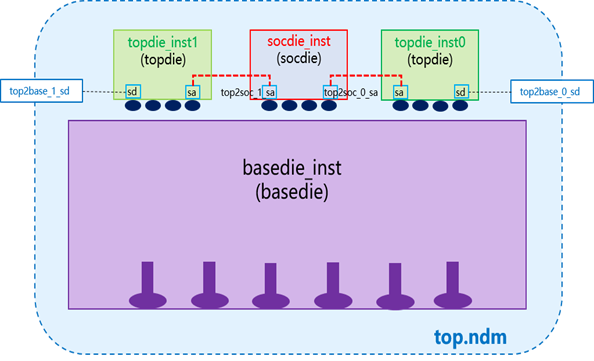

圖 1

3DIC系統架構

topdie/socdie Die原型創建:使用基本輸入(Die的尺寸、工藝文件、I/O信息)開始創建新設計:

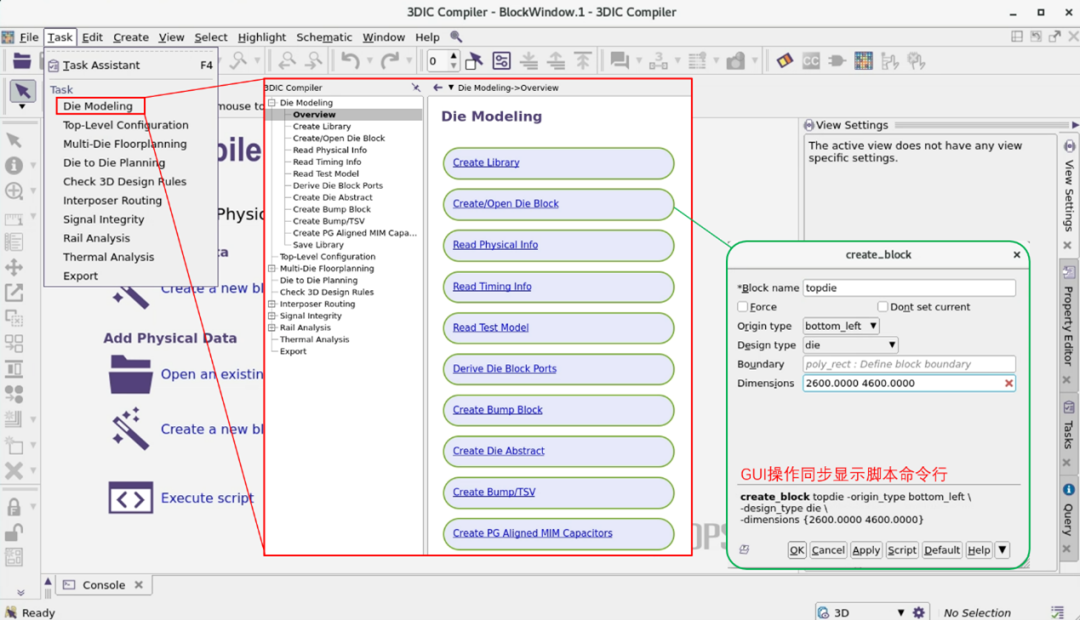

1)在菜單欄選中Task->Die Modeling,如圖2所示,在設計流程任務列表中選擇所需操作按序執行。通過Create Library -> Create Die Block完成工藝文件的導入和Die尺寸的設置。GUI 操作同步顯示對應的腳本命令行,可通過界面Script按鈕導出文本。

圖 2

創建Die Design流程

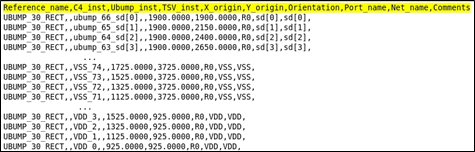

2)讀取I/O物理信息。工程師可以讀取已有的DEF、MDXF、CSV文件,也可以采用3DIC Compiler創建Bump/TSV。其中,CSV文件中提供Bump實例名稱、Bump坐標以及互連的端口和網絡,如圖3所示。在讀取CSV數據之后,Bump的物理和邏輯信息,包括P/G的net和port等都可以在Die design中完成創建。

圖 3

CSV文件格式

2. basedie/interposer Design創建

basedie/interposer design Library的創建流程參考topdie/socdie Die。完成Library的創建以后,下一步是網表的導入。對于初始網表,工程師根據不同的設計需求,可以采用2種網表格式:

1)空白網表:網表中不包含端口或邏輯連接,所有Die-to-Die以及Die-to-Package的互聯關系都是在系統頂層指定的。工具通過分析連接關系自動追溯創建basedie/interposer的網表:插入interposer/basedie到package的端口、Die到package feedthrough信號通路、D2D連接。

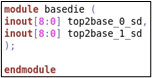

2)包含部分或者全部互連關系的網表:例如連接package的端口,如圖4所示。

圖 4

basedie design定義部分互連關系的網表示例

3. 3DIC系統頂層網表的定義

3DIC Compiler采用虛擬系統頂層定義進行系統設計實現和管理,其中包含多芯片系統的所有實例和互連,本身并不會產生用于生產制造的實際GDS。它的網表是一個層次化網表,對D2D互連線、Die到package feedthrough互連端口等進行完整定義。

1)basedie/interposer design初始網表為空時,系統頂層網表中D2D、D2Package feedthrough互連端口定義如圖5所示:

圖 5

top-level design網表示例

2)basedie/interposer design初始網表定義了package的端口時,系統頂層網表中D2D、D2Package feedthrough互連端口定義如圖6所示:

圖 6

top-level design網表示例

注意:當網表中含有D2D、D2Package bus總線互連的定義時,需要注意bit的定義順序。比如本案例中,需要滿足topdie port sd[8:0]與basedie port top2base_0_sd[8:0]同樣比特的互連時,必須滿足design創建bus port/net按照同樣的順序:

創建topdie design讀取CSV文件時read_design_io需要加上option -create_bus_high_to_low,實現bus net或port按照從高比特到低比特的順序創建;

basedie design網表bus net 按照從高比特到低比特的順序定義;

top-level design網表bus net 按照從高比特到低比特的順序定義;

當然,工程師也可以采用design中創建bus port/net都按照從低比特到高比特的順序。

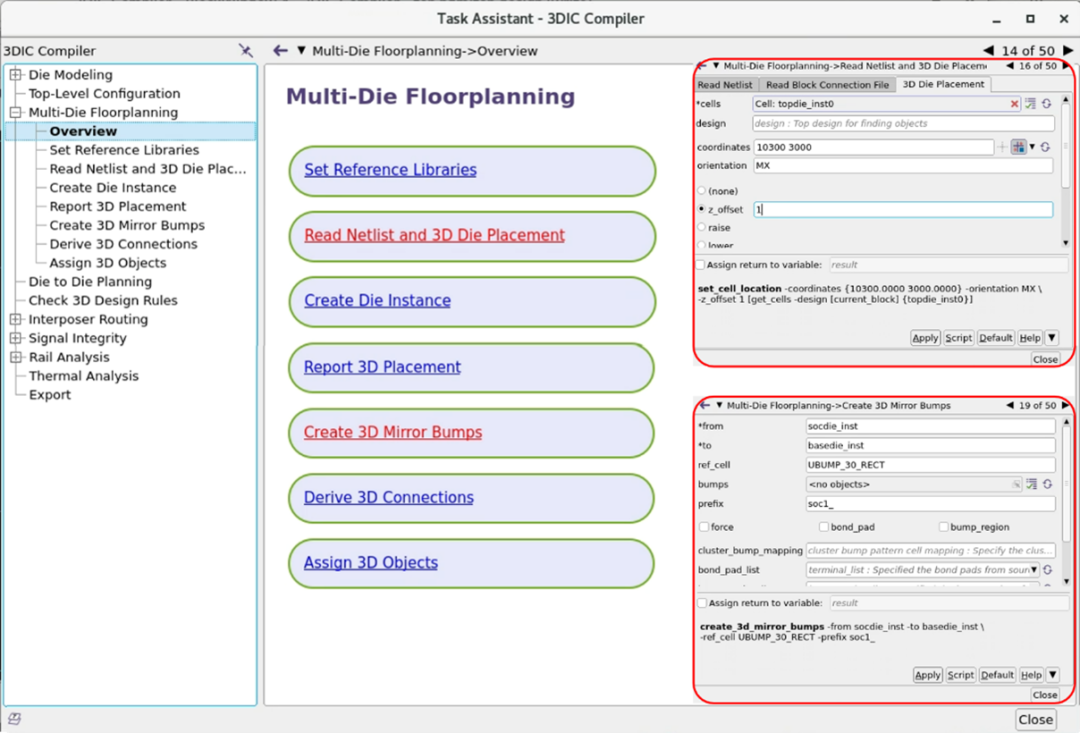

4.3DIC系統布局規劃

Top-level design Library的創建流程參考topdie/socdie Die。在Task Assistant中選擇Multi-Die Floorplanning,依次選擇所需操作,例如:網表的讀入、3D Die布局、Bump鏡像、Net assign等操作,如圖7所示,實現3DIC系統布局規劃。

圖 7

Multi-Die Floorplan流程

其中需要注意的是,當通過鏡像的方式自動完成basedie Bumps的創建和對準后,要以assign net的方式自動追溯D2D、D2Package的各種邏輯互連關系,實現basedie的netlist創建。在這個過程中,

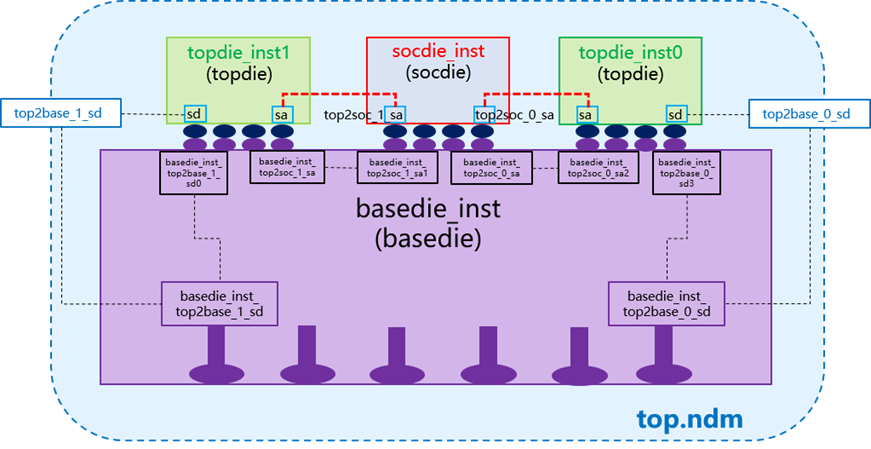

1)當basedie/interposer design初始網表為空時:工具依據C4 Bumps和ubumps之間的曼哈頓距離來選擇C4Bumps,更嚴格地說,工具綜合計算所有Net長度,找到設計中所有Net的曼哈頓距離的最小總和來完成D2Package邏輯互連關系的創建,實現basedie的netlist創建。如圖8所示。

圖 8

Mirror Bump和assign net 的原理圖

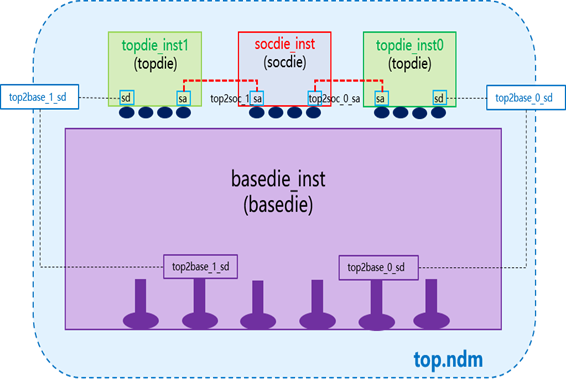

2)當basedie/interposer design初始網表定義了package的端口時:工具自動追溯D2D、D2Package的邏輯互連關系,實現basedie的netlist創建,如圖9所示。

圖 9

Mirror Bump和assign net 的原理圖

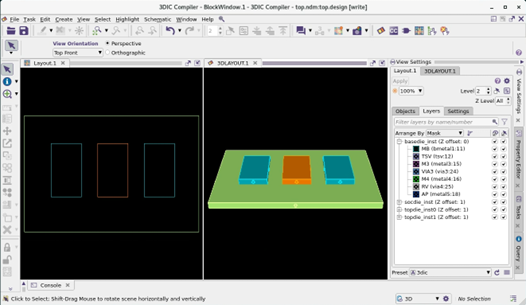

完成以上操作以后,就可以完整實現系統級的可視化管理,如圖10所示,基于系統級頂層結構,可進行系統級的各類仿真、分析、驗證工作。

圖 10

系統頂層的2D和3D視圖

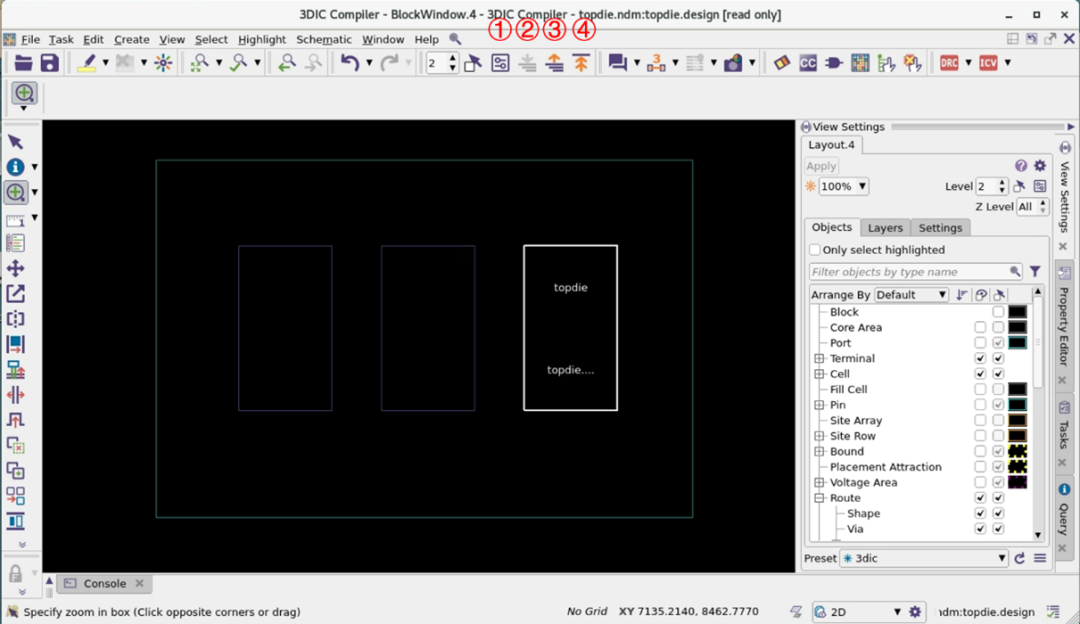

5.在頂層設計的背景下編輯Die Design

3DIC Compiler的就地編輯(Edit In Place, EIP)功能允許工程師在3D系統頂層設計的背景下編輯選定的芯片,而無需在另一個窗口中打開該Die Design。EIP菜單欄提供了以下選項:

①層次結構

設置視圖層次,擴展cell類型,改變顯示方式,以及設置打開多個或關閉多個層次;

②下推

向下推到一個選定的block;

③彈出

彈回上一層;

④彈到頂部

彈到最上面的一層。

當工程師使用EIP編輯一個較低層別的Die Design時,通過點擊EIP菜單欄上的彈出圖標,當前的block會變成所選Die Design的block。在編輯過程中,被選中的會被高亮顯示,而其他的Die Design都會變暗,如圖11所示。使用'f'鍵放大到當前選中的block,工程師就可以執行編輯操作。另外,請注意,被選中的Die Design保留了頂層設計中的方向和旋轉角度。

圖 11

就地編輯Die Design

總結

本文介紹了如何使用3DIC Compiler便捷高效地實現3DIC系統頂層的創建管理,從Die原型創建開始,進行Multi-Die Floorplan規劃,basedie或interposer 以及系統頂層網表定義,基于系統頂層實現basedie/interposer Bumps自動創建和對準,以及自動追溯D2D、D2Package的各種互連關系建立邏輯互連,最終實現3DIC系統頂層的創建管理。其中,可以特別關注“就地編輯”功能,它能極大地幫助工程師提升多芯片系統設計的效率。

審核編輯:劉清

-

EDA技術

+關注

關注

12文章

172瀏覽量

36877 -

HPC

+關注

關注

0文章

311瀏覽量

23683 -

GUI

+關注

關注

3文章

648瀏覽量

39546 -

DEF

+關注

關注

0文章

13瀏覽量

6234 -

GDS

+關注

關注

0文章

28瀏覽量

6235

原文標題:【應用案例】如何使用3DIC Compiler實現“3DIC系統頂層的創建管理”?

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何使用EDA中的3DIC Compiler實現3DIC系統頂層的創建管理

如何使用EDA中的3DIC Compiler實現3DIC系統頂層的創建管理

評論