“開關噪聲-EMC基礎篇”前后共有21篇文章,本文是最后一篇。從“EMC基礎”知識開始,以開關電源為前提分別介紹了“降噪對策(步驟與概要)”、“使用電容器降低噪聲”、“使用電感降低噪聲”、“其他降噪對策”相關的基礎內容。本文將對各篇文章的關鍵要點做最終總結。

<EMC基礎>

?何謂EMC

關鍵要點

?EMC(電磁兼容性)是指兼備EMI和EMS兩方面的性能。

?EMI(電磁干擾)是指因輻射/發射(Emission)電磁波而對環境產生的干擾。

?EMS(電磁敏感性)是指對電磁波干擾(EMI)的耐受性/抗擾度(Immunity)。

?頻譜基礎

關鍵要點

?當頻率升高時,頻譜振幅整體增加。

?上升/下降延遲時,進入-40dB/dec衰減時的頻率降低,頻譜的振幅衰減。

?Duty變更時,雖然會產生偶次諧波,但對譜峰無影響。基波頻譜衰減。

?僅上升延遲時,tr分量從更低的頻率開始衰減。

?差模(常模)噪聲與共模噪聲

關鍵要點

?電磁干擾EMI大致可分為“傳導噪聲”和“輻射噪聲”兩種。

?傳導噪聲可分為差模(常模)噪聲和共模噪聲兩類。

?關于輻射噪聲,差模噪聲的線纜環路面積、共模噪聲的線長是非常重要的因素。

?注意;即使條件相同,共模噪聲帶來的輻射遠遠大于差模噪聲。

?何謂串擾

關鍵要點

?平行的布線間會產生串擾。

?串擾的因素有雜散(寄生)電容引發的電容(靜電)耦合和互感引發的電感(電磁)耦合。

?開關電源產生的噪聲

關鍵要點

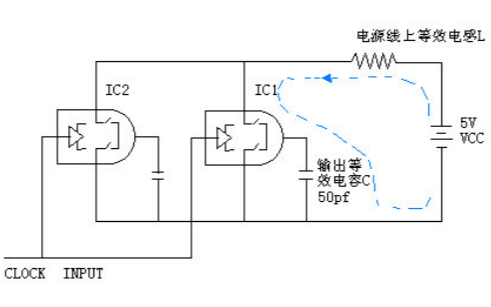

?在開關時會產生急劇電流ON/OFF的環路中,會因寄生分量產生高頻振鈴=開關噪聲。

?這種開關噪聲可通過優化PCB板布線等來降低,但即使這樣,殘留的噪聲也會作為共模噪聲傳導至輸入電源,因此需要采取防止噪聲漏出的措施。

<降噪對策>

?降噪對策步驟

關鍵要點

?隨著開發進程的推進,可使用的降噪對策技術和手段越來越有限,對策成本也越來越高。

?在產品開發的初期階段,預先進行充分探討與評估,可以從容有效地采取降噪對策。

?掌握噪聲的種類和性質,并針對不同的噪聲采取不同的有效對策是非常重要的。

?降噪對策按照“把握頻率成分→把握產生源和傳導路徑→強化GND→增加降噪部件”的步驟進行。

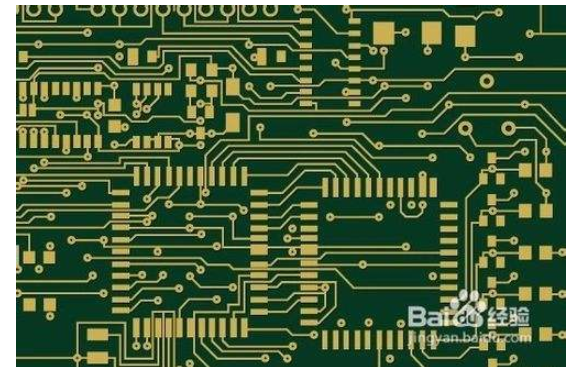

?開關電源噪聲對策的基礎知識

關鍵要點

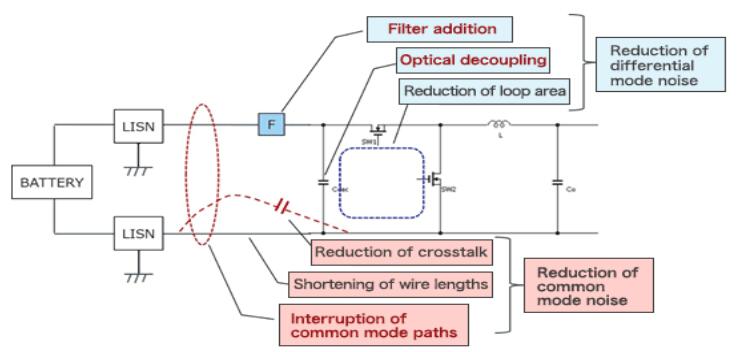

?要想降低差模噪聲,可在電路板上縮小大電流路徑的環路面積,并增加最優解耦和輸入濾波器。

?盡可能地抑制噪聲的發生源–差模噪聲是非常重要的,也關系到降低共模噪聲。

?要想降低共模噪聲,可縮短布線,抑制串擾,切斷(濾波)共模路徑。

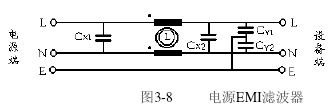

?開關電源的輸入濾波器

關鍵要點

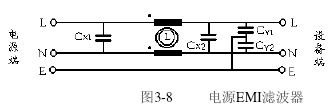

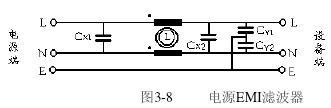

?開關電源的輸入濾波器,需要針對共模噪聲和差模噪聲分別采用不同的處理。

?對共模噪聲使用共模濾波器。

?對差模噪聲使用由電容器、電感、磁珠、電阻等部件組成的濾波器。

<使用電容器降低噪聲>

?電容的頻率特性

關鍵要點

?降噪用電容器的選型需要根據阻抗的頻率特性進行(而非容值)。

?容值和ESL越小,諧振頻率越高,高頻區域的阻抗越低。

?容值越大,容性區域的阻抗越低。

?ESR越小,諧振頻率的阻抗越低。

?ESL越小,感性區域的阻抗越低。

?使用電容器降低噪聲

關鍵要點

?通過降低目標噪聲頻率的阻抗來降低噪聲幅度。

?降噪用電容器的選型需要根據阻抗的頻率特性進行(而非容值)。

?去耦電容的有效使用方法要點1

關鍵要點

?去耦電容的有效使用方法有兩個要點:①使用多個電容,②降低電容的ESL。

?使用多個電容時,容值相同時和不同時的效果不同。

?去耦電容的有效使用方法要點2

關鍵要點

?去耦電容的有效使用方法有兩個要點:①使用多個電容,②降低電容的ESL。

?通過降低電容的ESL,可改善高頻特性,并可更有效地降低高頻噪聲。

?有的電容雖然容值相同,但因尺寸和結構不同而ESL更小。

?去耦電容的有效使用方法其他注意事項

關鍵要點

?理解Q與頻率-阻抗特性之間的關系,并根據目的區分Q的差異。

?高Q電容窄帶阻抗急劇下降。低Q電容在較寬頻段相對平緩下降。

?PCB圖形的熱風焊盤等會增加電感分量,使諧振頻率向低頻端移動。

?探討對策時的試裝,如果不按照現實的修改實際安裝,很可能在修改后的PCB板上無法獲得探討時的效果。

?電容量變化率大時,諧振頻率會變化,無法獲得目標頻率理想的噪聲消除效果。

?在溫度條件和變動較大的嚴苛應用中,可以探討使用具有CH、C0G特性的溫度特性優異的電容。

?去耦電容的有效使用方法總結

<使用電感降低噪聲>

?電感的頻率特性

關鍵要點

?電感在諧振頻率之前呈現感性特性(阻抗隨頻率升高而增加)。

?電感在諧振頻率之后呈現容性特性(阻抗隨頻率升高而減小)。

?在比諧振頻率高的頻段,電感不發揮作為電感的作用。

?電感值L變小時,電感的諧振頻率會升高。

?電感的諧振點阻抗受寄生電阻分量的限制。

?使用電感和鐵氧體磁珠降低噪聲的對策

關鍵要點

?用于降噪對策的電感,大致可以分為繞組型電感構成的濾波器和利用鐵氧體磁珠進行熱轉換兩種。

?鐵氧體磁珠與普通電感相比,具有電阻分量R較大、Q值較低的特性。

?普通的電感可容許較大的直流疊加電流,只要在其范圍內,阻抗不怎么受直流電流的影響。

?鐵氧體磁珠對于直流電流容易飽和,飽和會導致電感值下降,諧振點向高頻段轉移。

?普通電感構成的濾波器,可選電感值的范圍較寬。

?鐵氧體磁珠的Q值較低,因此在較寬頻率范圍內具有有效的降噪效果。

?使用共模濾波器降低噪聲的對策

關鍵要點

?使用共模濾波器消除對共模噪聲。

?共模濾波器是利用自感作用來阻止共模電流通過的濾波器。

?注意點 : 串擾、GND線反彈噪聲

關鍵要點

?有些PCB板布線布局,會因串擾而導致濾波效果下降。

?Π型濾波器的電容的GND的某些設置方法可能會帶來地線反彈噪聲。

?優化PCB板布線布局可避免這些問題。

?使用電感降低噪聲 總結

<其他降噪對策>

?RC緩沖電路

關鍵要點

?RC緩沖電路可通過電阻將寄生電容、寄生電感等產生的尖峰電壓轉換為熱,從而降低尖峰電壓。

?增加緩沖電路可能會導致效率降低,因此需要探討噪聲水平和效率之間的平衡點。

?電阻是將噪聲電壓轉換為熱,因此需要注意電阻的容許損耗。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

相關推薦

本帖最后由 eehome 于 2013-1-5 09:56 編輯

EMI-EMC設計積驗總結

發表于 08-09 13:24

EMI-EMC設計積驗總結

發表于 08-20 13:07

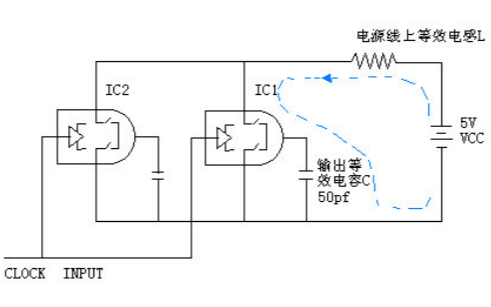

1、為什么數字電路的地線和電源線上經常會有很大的噪聲電壓?怎樣減小這些噪聲電壓? 數字電路工作時會瞬間吸取很大的電流,這些瞬變電流流過電源線和地線時,由于電源線和地線電感的存在,會產生較大的反沖電壓,這就是觀察到的噪聲電壓。減小這些噪聲電壓的方法一是減小電源線和地線的電感,如使用網格地、地線面、電源線面等,另一個方法是在電源線上使用適當的解耦電容(儲能電容)。 2、在實踐中,常見到將多股導線絞起來作為高頻導體,據說這樣可以減小導線的射頻阻抗,這是為什么? 這樣增加了導線的表面積,從而減小了高頻電阻。 3、電路或線路板電磁兼容性設計時要特別注意關鍵信號的處理,這里的關鍵信號指那些信號? 從電磁發射的角度考慮,關鍵信號線指周期性信號,如本振信號、時鐘信號、地址低位信號等;從敏感度的角度考慮,關鍵信號指對外界電磁干擾很敏感的信號,如低電平模擬信號。 4、怎樣防止搭接點出現電化學腐蝕現象? 選擇電化學電位接近的金屬,或對接觸的局部進行環境密封,隔絕電解液。 5、什么是搭接,舉出幾種搭接的方法。 金屬構件之間的低阻抗(射頻)連接稱為搭接,搭接的方式有焊接、鉚接、螺釘連接、電磁密封襯墊連接等。 6、請盡可能多的列出降低地線射頻阻抗的方法。 盡量使用表面積大的導體,以減小高頻電流的電阻;盡量使導體短些,以減小電阻和電感;在導體表面鍍銀,減小表面電阻;多根導體并聯,減小電感。 7、為什么在有些進口樣機中看到有些地線通過電容或電感接地? 為了使地線系統對于不同頻率的信號呈現不同的地線結構。 8、導致地線干擾問題的根本原因是什么? 地線的阻抗是導致地線問題的根本原因,由于地線阻抗的存在,當地線上流過電流時,就會產生電壓,形成電位差,而我們在設計電路時,是假設地線上各點電位是相同的,地線電位是整個系統工作的參考電位,實際地線電位與假設條件的不同導致了各種各樣的地線問題。 9、在進行電磁干擾問題分析時,往往用什么定義來描述地線? 將地線定義為信號的回流線。 10、當穿過面板的導線很多時,往往使用濾波連接器或濾波陣列板,在安裝濾波連接器或濾波陣列板時要注意什么問題? 要在濾波連接器或濾波陣列板與機箱面板之間安裝電磁密封襯墊或用導電膠帶將縫隙粘起來,防止縫隙處的電磁泄漏。

發表于 09-27 11:15

EMI-EMC設計積驗總結

發表于 09-15 17:05

華為的EMC設計資料:本書對PCB的EMC設計現有成果加以總結,推廣,同時對一些未知的領域進行積極的探索。結合PCB設計過程中的經驗教訓以及產品的EMC測試數據。

發表于 04-01 19:08

?0次下載

華為的EMC設計資料:本書對PCB的EMC設計現有成果加以總結,推廣,同時對一些未知的領域進行積極的探索。結合PCB設計過程中的經驗教訓以及產品的EMC測試數據。

發表于 02-24 09:33

?0次下載

華為pcb的emc設計指南:本書對PCB的EMC設計現有成果加以總結,推廣,同時對一些未知的領域進行積極的探索。結合PCB設計過程中的經驗教訓以及產品的EMC測試數據。

發表于 02-24 09:34

?0次下載

電磁兼容性EMC(Electro Magnetic Compatibility)是指設備或系統在其電磁環境中符合要求運行并不對其環境中的任何設備產生無法忍受的電磁干擾的能力。因此,EMC包括兩個方面

發表于 07-07 09:24

?7731次閱讀

此文檔為EMC設計指導文件本文檔的主要內容詳細介紹的是電磁兼容EMC的設計總結。

整體布局

1、高速、中速、低速電路要分開;

2、強電流、高電壓、強輻射元器件遠離弱電流、低電壓、敏感元器件

發表于 09-20 08:00

?7次下載

下圖總結了開關電磁兼容EMC的噪聲和解決這些噪聲的基本措施。

發表于 05-13 10:03

?1029次閱讀

本書旨在對我司PCB的EMC設計現有成果加以總結、推廣,同時對一些未知的領域進行積極的探索。結合我司PCB設計過程中的經驗教訓以及產品的EMC測試數據,我們對PCB的EMC設計進行了較

發表于 12-18 08:00

?0次下載

RJ45以太網口EMC設計總結

發表于 12-30 11:07

?85次下載

本書旨在對我司PCB的EMC設計現有成果加以總結、推廣,同時對- -些未知的領域進行積極的探索。結合我司PCB設計過程中的經驗教訓以及產品的EMC測試數據,我們PCB的EMC設計進行了

發表于 06-06 10:45

?0次下載

EMC設計總結

發表于 12-30 09:20

?4次下載

EMC基礎-總結

EMC基礎-總結

評論