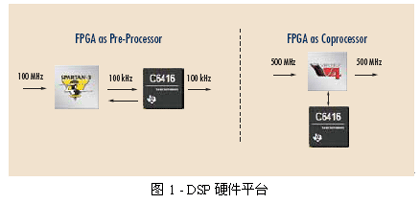

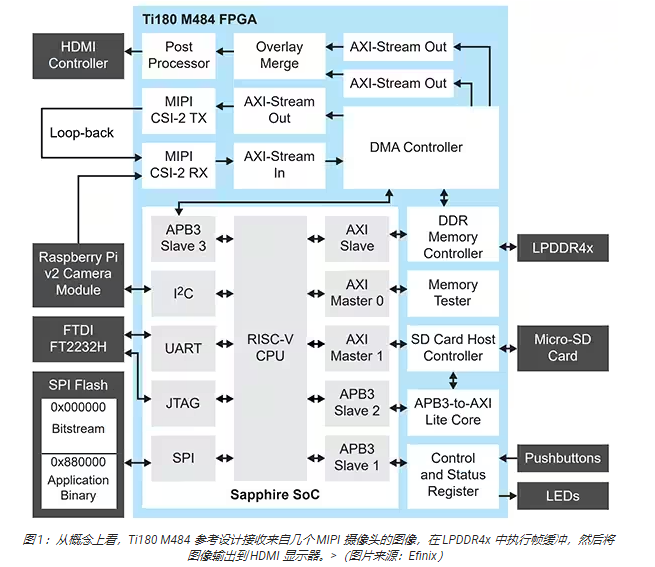

圖像處理系統(tǒng)設(shè)計(jì)注意點(diǎn):1.將算法開(kāi)發(fā)和FPGA實(shí)現(xiàn)分離用軟件的圖像處理環(huán)境可以使用大批量的圖像樣本進(jìn)行測(cè)試及調(diào)試算法,再將算法映射到硬件上,這樣大大節(jié)省了硬件調(diào)試周期。圖像處理的算法中,大部分需要采用浮點(diǎn)數(shù)運(yùn)算,而浮點(diǎn)數(shù)運(yùn)算再FPGA中是非常不劃算的,因此需要轉(zhuǎn)換成定點(diǎn)數(shù)計(jì)算,此時(shí)會(huì)設(shè)計(jì)到浮點(diǎn)運(yùn)算轉(zhuǎn)定點(diǎn)運(yùn)算時(shí)精度下降的問(wèn)題。這里的軟件是指DSP,CPU,硬件是指FPGA;一般結(jié)構(gòu)規(guī)則計(jì)算量大的操作如sobel算子均值濾波可以采用硬件進(jìn)行,不規(guī)則的動(dòng)態(tài)可變長(zhǎng)度循環(huán)的底層算法由軟件進(jìn)行;

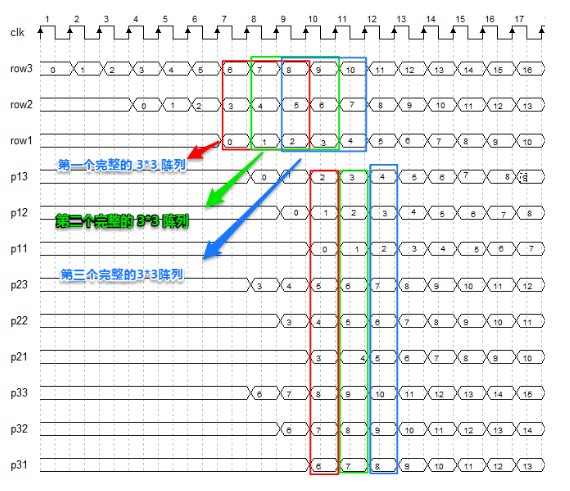

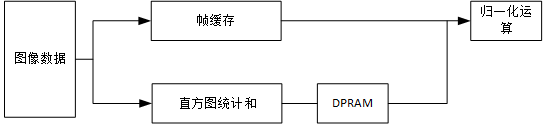

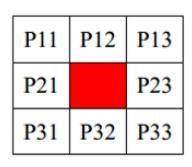

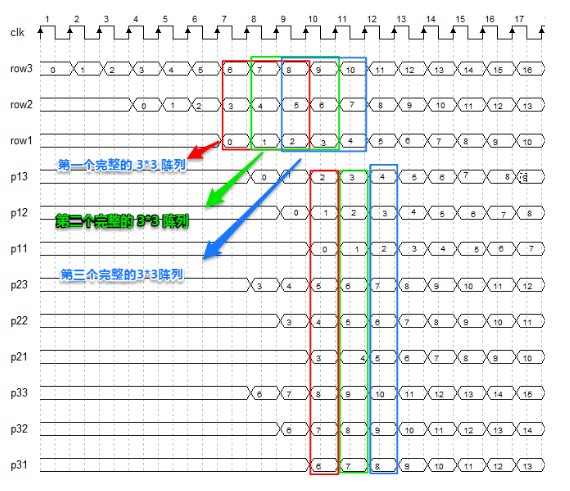

圖像處理FPGA 設(shè)計(jì)基本方法:1.陣列結(jié)構(gòu)結(jié)合流水線(xiàn)處理設(shè)計(jì)例如RGB圖像,包括三組數(shù)據(jù),處理時(shí)需要并行三通道后,每個(gè)通道進(jìn)行分別的串行流水處理。直方圖是圖像的灰度分布統(tǒng)計(jì)的一種表示方法,統(tǒng)計(jì)目標(biāo)圖像中各個(gè)灰度點(diǎn)的像素個(gè)數(shù),很多對(duì)于圖像的調(diào)整算法都是基于此進(jìn)行的;如何基于FPGA進(jìn)行統(tǒng)計(jì)呢?1)由于是統(tǒng)計(jì)圖像的直方圖,所以一定是統(tǒng)計(jì)結(jié)果會(huì)在圖像經(jīng)過(guò)之后才能產(chǎn)生,因此需要進(jìn)行緩存;緩存一:統(tǒng)計(jì)后的結(jié)果;緩存二:經(jīng)過(guò)統(tǒng)計(jì)處理器的圖像數(shù)據(jù),以便后面和直方圖做同步處理。2)圖像常常用8位、24位、32位來(lái)表示一個(gè)像素的灰度值, 因此,統(tǒng)計(jì)種類(lèi)分別為2^8=256/2^24=16777216/2^32=4294967296,地址位寬根據(jù)此進(jìn)行選擇設(shè)定;根據(jù)不同的精度選擇不同的緩存方式:片內(nèi)或片外緩存; 首先根據(jù)當(dāng)前來(lái)的灰度值做為讀RAM地址,讀出RAM中對(duì)應(yīng)灰度值的的統(tǒng)計(jì)值;第二將讀出結(jié)果加一并回寫(xiě)回RAM的當(dāng)前地址中;第三重復(fù)操作至當(dāng)前圖像處理結(jié)束;第四下一幅圖像到來(lái)之前順序按灰度值從0到最大的順序?qū)⒆罱K結(jié)果讀出;因此以行同步脈沖的上升沿作為統(tǒng)計(jì)開(kāi)始,行同步脈沖作為行統(tǒng)計(jì)計(jì)數(shù)器 行統(tǒng)計(jì)計(jì)數(shù)器達(dá)到最大高度時(shí),作為統(tǒng)計(jì)結(jié)束標(biāo)志。1.統(tǒng)計(jì)出直方圖,獲取各個(gè)像素灰度累加和2.乘以均衡系數(shù):(2^DW-1)/IW*IH(像素最大值/圖像的面積)首先需要區(qū)分線(xiàn)性和非線(xiàn)性濾波器的區(qū)別,區(qū)別在于其輸出與輸入之間是否有唯一且確定的函數(shù)傳遞。銳化濾波器:主要包括SOBEL算子 LAPLAS算子梯度運(yùn)算等濾波器的物理意義主要是響應(yīng)信號(hào)對(duì)目標(biāo)信號(hào)響應(yīng)后的樣子,也就是響應(yīng)函數(shù)g(i,j)滑過(guò)整個(gè)圖像,即對(duì)圖像做一個(gè)卷積處理,就得到了濾波結(jié)果。用一個(gè)圖像區(qū)域的各個(gè)像素的平均值來(lái)代替原圖像的各個(gè)像素值,主要作用是減小銳度,減小噪聲。 均值濾波一般出現(xiàn)在圖像處理的預(yù)處理步驟, 預(yù)處理后,根據(jù)噪聲來(lái)源,例如針對(duì)椒鹽噪聲做中值濾波處理,針對(duì)高斯噪聲做高斯濾波處理后續(xù)可能繼續(xù)做邊緣提取等復(fù)雜操作處理。設(shè)計(jì)一個(gè)濾波器可以理解成設(shè)計(jì)一個(gè)響應(yīng)函數(shù)g(x,y)=Σi=-rrΣj=-rrI(x+i,y+j)) / (2r+1)2數(shù)學(xué)公式很好理解,就是求一個(gè)窗口的所有像素灰度值之后后再除以整個(gè)窗口的面積也就是像素點(diǎn)個(gè)數(shù),求出平均值; 均值濾波的方法將數(shù)據(jù)存儲(chǔ)成3x3的矩陣,然后求這個(gè)矩陣。在圖像上對(duì)目標(biāo)像素給一個(gè)模板, 該模板包括了其周?chē)呐R近像素(以目標(biāo)象素為中心的周?chē)?8 個(gè)像素,構(gòu)成一個(gè)濾波模板,即去掉目標(biāo)像素本身),再用模板中的全體像素的平均值來(lái)代替原來(lái)像素值。 (參考:http://www.cnblogs.com/ninghechuan/p/6789399.html) (參考:http://www.cnblogs.com/aslmer/p/5779079.html#undefined) shift_ram 進(jìn)行數(shù)據(jù)矩陣化,將3x3矩陣的中心像素的周?chē)藗€(gè)點(diǎn)求和,采取了流水線(xiàn)的設(shè)計(jì)方法,來(lái)增加吞吐量,然后再求平均值代替目標(biāo)像素的值。

1 //矩陣元素移位賦值

2 always @(posedge clk or negedge rst_n)begin

3 if(rst_n==1'b0)begin

4 {p_11,p_12,p_13} <= {5'b0,5'b0,5'b0} ;

5 {p_21,p_22,p_23} <= {15'b0,15'b0,15'b0};

6 {p_31,p_32,p_33} <= {15'b0,15'b0,15'b0};

7 end

8 else begin

9 if(per_href_ff0==1&&flag_do==1)begin

10 {p_11,p_12,p_13}<={p_12,p_13,row_1};

11 {p_21,p_22,p_23}<={p_22,p_23,row_2};

12 {p_31,p_32,p_33}<={p_32,p_33,row_3};

13 end

14 else begin

15 {p_11,p_12,p_13}<={5'b0,5'b0,5'b0};

16 {p_21,p_22,p_23}<={5'b0,5'b0,5'b0}

17 {p_31,p_32,p_33}<={5'b0,5'b0,5'b0}

18 end

19 end

20 end

21

22

23 always @(posedge clk or negedge rst_n)begin

24 if(rst_n==1'b0)begin

25 mean_value_add1<=0;

26 mean_value_add2<=0;

27 mean_value_add3<=0;

28 end

29 else if(per_href_ff1)begin

30 mean_value_add1<=p_11+p_12+p_13;

31 mean_value_add2<=p_21+ 0 +p_23;

32 mean_value_add3<=p_31+p_32+p_33;

33 end

34 end

35

36 wire [8:0]mean_value;//8位數(shù)之和

37 wire [5:0]fin_y_data; //平均數(shù),除以8,相當(dāng)于左移三位。

38

39 assign mean_value=mean_value_add1+mean_value_add2+mean_value_add3;

40 assign fin_y_data=mean_value[8:3];

| -1 0 +1 |

Gx= | -2 0 +2 |

| -1 0 +1 |

| -1 -2 -1 |

Gy= | 0 0 0 |

| +1 +2 +1 |包括X和Y兩個(gè)方向的兩套3X3矩陣,使其分別和圖像的X和Y方向進(jìn)行卷積計(jì)算(矩陣的卷積計(jì)算即將所有元素做乘加計(jì)算);兩個(gè)方向的卷積結(jié)果求平方根計(jì)算;計(jì)算結(jié)果如果大于閾值則等于0xffff,如果小于閾值則等于0;參考代碼如下:由于算子簡(jiǎn)單以及有正負(fù)區(qū)分,因此需要做正值和負(fù)值分別計(jì)算后再進(jìn)行相減計(jì)算。// | -1 0 +1 |

//Gx= | -2 0 +2 |

// | -1 0 +1 |

//

// | -1 -2 -1 |

//Gy= | 0 0 0 |

// | +1 +2 +1 |

reg [8:0] p_x_data ,p_y_data ; // x 和 y 的正值之和

reg [8:0] n_x_data ,n_y_data ; // x 和 y 的負(fù)值之和

reg [8:0] gx_data ,gy_data ; //最終結(jié)果

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

p_x_data <=0;

n_x_data <=0;

gx_data <=0;

end

else if(per_href_ff1==1) begin

p_x_data <= p_13 + (p_23<<1) + p_33 ;

n_x_data <= p_11 + (p_12<<1 )+ p_13 ;

gx_data <= (p_x_data >=n_x_data)? p_x_data - n_x_data : n_x_data - p_x_data ;

end

else begin

p_x_data<=0;

n_x_data<=0;

gx_data <=0;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

p_y_data <=0;

n_y_data <=0;

gy_data <=0;

end

else if(per_href_ff1==1) begin

p_y_data <= p_11 + (p_12<<1) + p_13 ;

n_y_data <= p_31 + (p_32<<1) + p_33 ;

gy_data <= (p_y_data >=n_y_data)? p_y_data - n_y_data : n_y_data - p_y_data ;

end

else begin

p_y_data <=0;

n_y_data <=0;

gy_data <=0;

end

end

//求平方和,調(diào)用ip核開(kāi)平方

reg [16:0] gxy; // Gx 與 Gy 的平方和

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

gxy<=0;

end

else begin

gxy<= gy_data* gy_data + gx_data* gx_data ;

end

end

wire [8:0] squart_out ;

altsquart u1_altsquart ( //例化開(kāi)平方的ip核

.radical (gxy),

.q (squart_out), //輸出的結(jié)果

.remainder()

);

//與閾值進(jìn)行比較

reg [15:0] post_y_data_r;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

post_y_data_r<=16'h00;

end

else if(squart_out>=threshold)

post_y_data_r<=16'h00 ;

else

post_y_data_r<=16'hffff ;

end

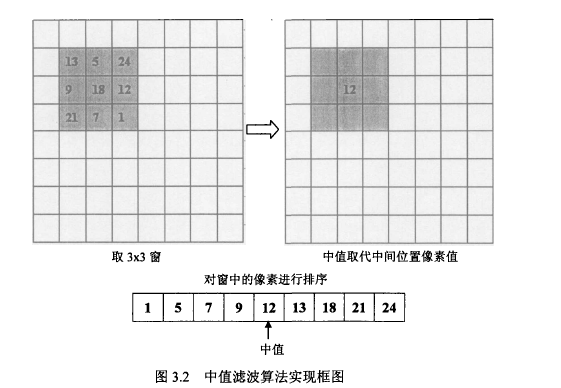

非線(xiàn)性濾波器通常下是沒(méi)有特定的轉(zhuǎn)移函數(shù),統(tǒng)計(jì)排序?yàn)V波器; 中值濾波

將 3*3 滑動(dòng)塊中的灰度值進(jìn)行排序,然后用排序的中間值取代 3*3 滑塊中心的值。示意圖如下圖所示。 第二步:提取出最大值的最小值,中間值的中間值,最小值的最大值 第三步:將第二步提取出來(lái)的三個(gè)數(shù)進(jìn)行排序,中間值即我們要求的中間值。圖像分割是將圖像劃分成若干個(gè)互不相交的小區(qū)域的過(guò)程,將圖像中有意義的特征或應(yīng)用所需要的特征信息提取出來(lái),最終結(jié)果是分割成一些具有

至芯科技12年不忘初心、再度起航2月11日北京中心FPGA工程師就業(yè)班開(kāi)課、線(xiàn)上線(xiàn)下多維教學(xué)、歡迎咨詢(xún)!

FPGA學(xué)習(xí)-USB 3.0協(xié)議理解

ARM+FPGA的高速同步數(shù)據(jù)采集

掃碼加微信邀請(qǐng)您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

原文標(biāo)題:FPGA學(xué)習(xí)-基于FPGA的圖像處理

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

FPGA學(xué)習(xí)-基于FPGA的圖像處理

FPGA學(xué)習(xí)-基于FPGA的圖像處理

評(píng)論