-接下來(lái),請(qǐng)您介紹一下驅(qū)動(dòng)器源極引腳是如何降低開關(guān)損耗的。首先,能否請(qǐng)您對(duì)使用了驅(qū)動(dòng)器源極引腳的電路及其工作進(jìn)行說(shuō)明?

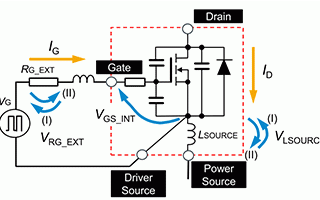

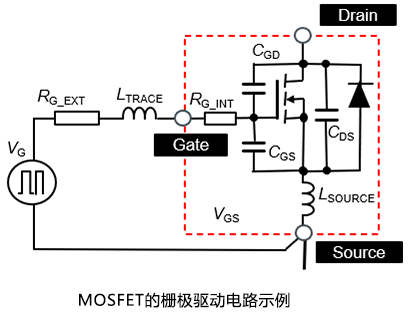

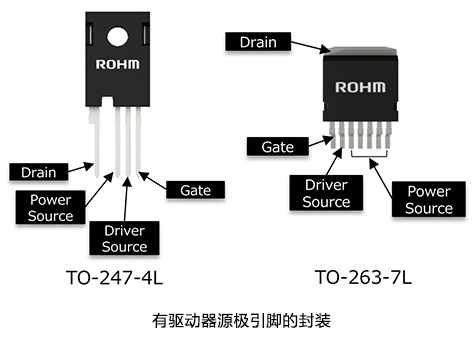

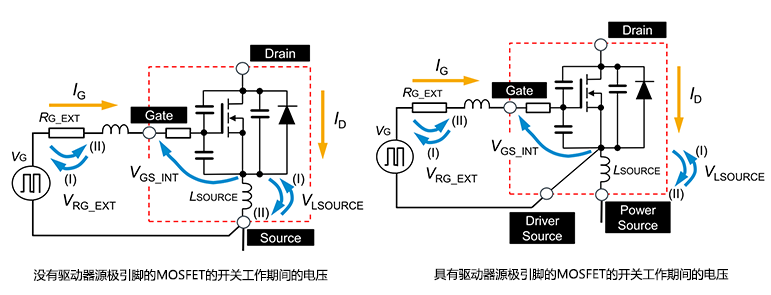

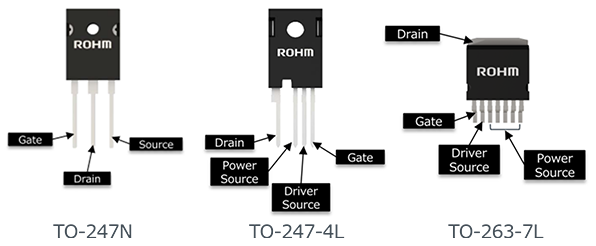

Figure 4是具有驅(qū)動(dòng)器源極引腳的MOSFET的驅(qū)動(dòng)電路示例。它與以往驅(qū)動(dòng)電路(Figure 2)之間的區(qū)別只在于驅(qū)動(dòng)電路的返回線是連接到驅(qū)動(dòng)器源極引腳這點(diǎn)。請(qǐng)看與您之前看到的Figure 2之間的比較。

從電路圖中可以一目了然地看出,包括VG在內(nèi)的驅(qū)動(dòng)電路中不包含LSOURCE,因此完全不受開關(guān)工作時(shí)的ID變化帶來(lái)的VLSOURCE的影響。

如果用公式來(lái)表示施加到內(nèi)部芯片的電壓VGS_INT的話,就是公式(2)。當(dāng)然,計(jì)算公式中沒有3引腳封裝的公式(1)中存在的LSOURCE相關(guān)的項(xiàng)。所以,4引腳封裝MOSFET的VGS_INT僅受RG_EXT和IG引起的電壓降VRG_EXT的影響,而且由于RG_EXT是外置電阻,因此也可調(diào)。下面同時(shí)列出公式(1)用以比較。

-能給我們看一下比較數(shù)據(jù)嗎?

這里有雙脈沖測(cè)試的比較數(shù)據(jù)。這是為了將以往產(chǎn)品和具有驅(qū)動(dòng)器源極引腳的SiC MOSFET的開關(guān)工作進(jìn)行比較,而在Figure 5所示的電路條件下使Low Side(LS)的MOSFET開關(guān)的雙脈沖測(cè)試結(jié)果。High Side(HS)是將RG_EXT連接于源極引腳或驅(qū)動(dòng)器源極引腳,并僅使用體二極管換流工作的電路。

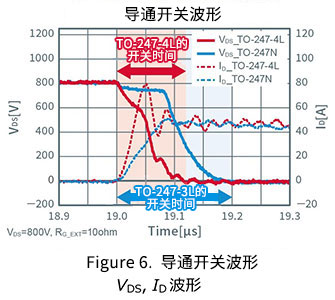

Figure 6是導(dǎo)通時(shí)的漏極-源極間電壓VDS和漏極電流ID的波形。這是驅(qū)動(dòng)條件為RG_EXT=10Ω、VDS=800V,ID約為50A時(shí)的波形。

紅色曲線的TO-247-4L為4引腳封裝,藍(lán)色的TO-247N為以往的3引腳封裝,其中的SiC MOSFET芯片是相同的。

我們先來(lái)比較一下虛線ID的波形。與藍(lán)色的3引腳封裝品的波形相比,紅色的4引腳封裝的ID上升更快,達(dá)到50A所需的時(shí)間當(dāng)然也就更短。

雖然VDS的下降時(shí)間本身并沒有很大的差別,但柵極信號(hào)輸入后的開關(guān)速度明顯變快。

-就像您前面說(shuō)明的,區(qū)別只在于4引腳封裝通過設(shè)置驅(qū)動(dòng)器源極引腳,消除了LSOURCE的影響,因此它們的開關(guān)特性區(qū)別只在于LSOURCE的有無(wú)所帶來(lái)的影響?可不可以這樣理解?

基本上是這樣。當(dāng)然,也有一些應(yīng)該詳細(xì)查考的事項(xiàng),但如果從柵極驅(qū)動(dòng)電路中消除了LSOURCE的影響,則根據(jù)Figure 4中說(shuō)明的原理,開關(guān)速度將變快。關(guān)于關(guān)斷,雖然不像導(dǎo)通那樣區(qū)別顯著,但速度同樣也會(huì)變快。

-這就意味著開關(guān)損耗得到了大幅改善。

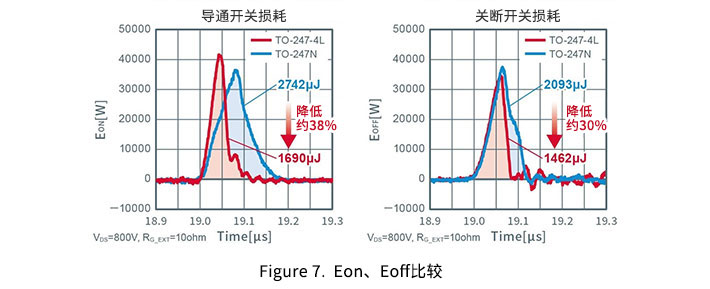

這里有導(dǎo)通和關(guān)斷相關(guān)的開關(guān)損耗比較數(shù)據(jù)。

在導(dǎo)通數(shù)據(jù)中,原本2,742μJ的開關(guān)損耗變?yōu)?,690μJ,損耗減少了約38%。在關(guān)斷數(shù)據(jù)中也從2,039μJ降至1,462μJ,損耗減少了約30%。

-明白了。最后請(qǐng)你總結(jié)一下,謝謝。

SiC MOSFET具有超低導(dǎo)通電阻和高速開關(guān)的特點(diǎn),還具有可進(jìn)一步縮小電路規(guī)模、提高相同尺寸的功率、以及因降低損耗而提高效率并減少發(fā)熱量等諸多優(yōu)點(diǎn)。

另一方面,關(guān)于在大功率開關(guān)電路中的功率元器件的安裝,由于必須考慮寄生電感等寄生分量的影響,如果開關(guān)電流速度明顯提高,那么其影響也會(huì)更大。這不僅僅是實(shí)裝電路板級(jí)別的問題,同時(shí)也是元器件封裝級(jí)別的課題。

此次之所以在最新一代SiC MOSFET中采用4引腳封裝,也是基于這樣的背景,旨在在使用了SiC功率元器件的應(yīng)用中,進(jìn)一步降低損耗。

這里有一個(gè)注意事項(xiàng),或者說(shuō)是為了有效使用4引腳封裝產(chǎn)品而需要探討的事項(xiàng)。前面提到了通過消除封裝電感LSOURCE的影響可提高開關(guān)速度并大大改善開關(guān)損耗。這雖然是事實(shí),但考慮到穩(wěn)定性和整個(gè)電路工作時(shí),伴隨著開關(guān)速度的提高,也產(chǎn)生了一些需要探討的問題。就像“權(quán)衡(Trade-off)”一詞所表達(dá)的,電路的優(yōu)先事項(xiàng)一定需要用最大公約數(shù)來(lái)實(shí)現(xiàn)優(yōu)化。

對(duì)此,將在Tech Web的基礎(chǔ)知識(shí)“SiC功率元器件”中進(jìn)行解說(shuō)。另外,您還可以通過ROHM官網(wǎng)下載并使用本次議題的基礎(chǔ),即Application Note“利用驅(qū)動(dòng)器源極引腳改善開關(guān)損耗(PDF)”。

-感謝您的講解。

審核編輯:湯梓紅

通過驅(qū)動(dòng)器源極引腳將開關(guān)損耗降低約35%

通過驅(qū)動(dòng)器源極引腳將開關(guān)損耗降低約35%

評(píng)論