使用always_ff和在靈敏度列表中指定一個時鐘邊沿并不意味著過程中的所有邏輯都是時序邏輯。綜合編譯器將推斷出每個被非阻塞賦值的變量的觸發器。阻塞賦值也可能推斷出觸發器,這取決于賦值語句相對于程序中其他賦值和操作的順序和上下文。

然而,在有些情況下,組合邏輯數據流行為將從時序邏輯程序中推斷出來。

時序賦值右側的操作符將綜合為組合邏輯,其輸出成為觸發器的D輸入。

如果時序分配的右側調用一個函數,該函數將綜合為組合邏輯,其輸出成為觸發器的D輸入。

圍繞著賦值語句的決策語句可能會綜合為組合式多路復用邏輯,選擇那個表達式作為觸發器的D輸入。

在begin-end語句組中對臨時變量的阻塞賦值,將綜合為組合邏輯,其中臨時變量成為在begin-end中后續非阻塞賦值推斷出的觸發器的輸入。

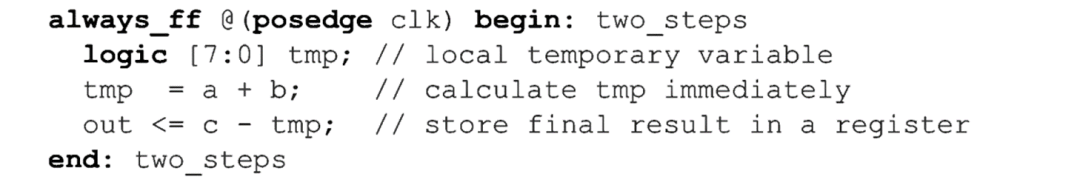

下面非例子說明了在begin-end語句組中對臨時變量的阻塞賦值,將綜合為組合邏輯。

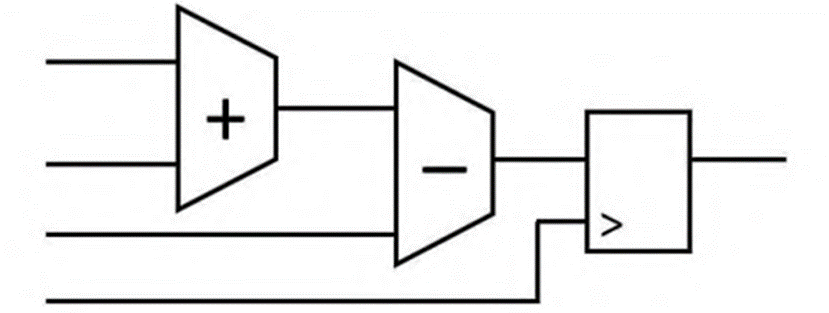

下面就是上面的例子中推斷的示意圖。

對中間臨時變量的阻塞賦值

審核編輯 :李倩

-

邏輯

+關注

關注

2文章

832瀏覽量

29449 -

觸發器

+關注

關注

14文章

1996瀏覽量

61052 -

時序

+關注

關注

5文章

385瀏覽量

37278

原文標題:【數字實驗室】時序邏輯程序中推斷組合邏輯?

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時序邏輯程序中推斷組合邏輯?

時序邏輯程序中推斷組合邏輯?

評論