可以看出,智能體并不像人類專家一樣追求直線布局。為了優(yōu)化布局,智能體更傾向于弧形布局。我們也希望能訓(xùn)練智能體高效地創(chuàng)造一些前所未有的布局方式。

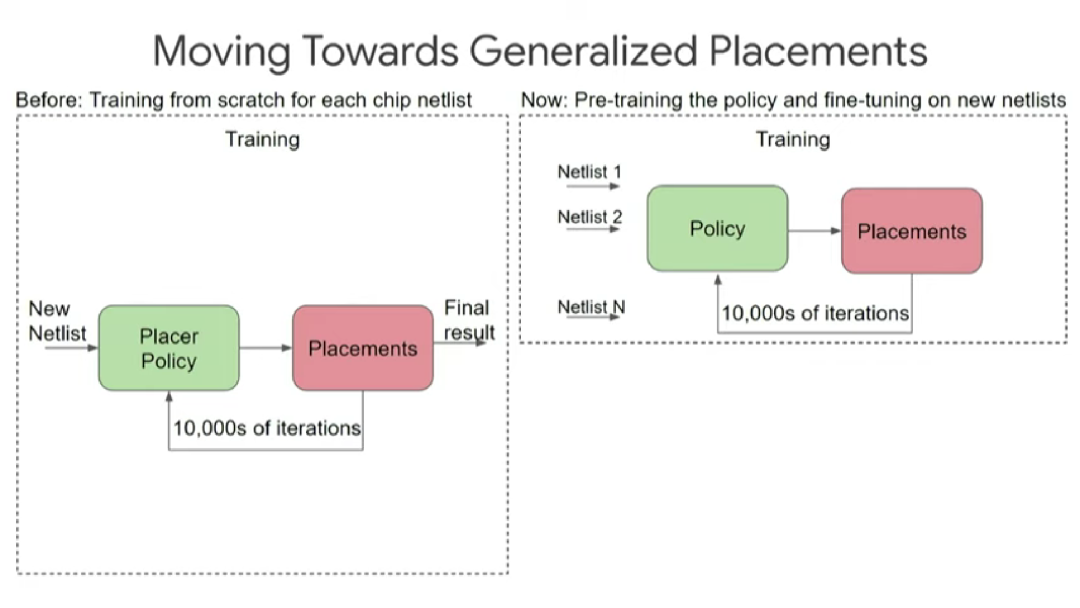

為了實(shí)現(xiàn)這個(gè)目標(biāo),首先,我們運(yùn)用強(qiáng)化學(xué)習(xí)算法優(yōu)化某個(gè)芯片設(shè)計(jì)塊的布局,期間需要經(jīng)歷上萬(wàn)次迭代;然后,重復(fù)前一步驟,在多個(gè)不同的設(shè)計(jì)塊上預(yù)訓(xùn)練出一套布局規(guī)則,最終讓算法在面對(duì)前所未見(jiàn)的新設(shè)計(jì)塊時(shí)也能給出布局方案。

預(yù)訓(xùn)練好的策略有助于在推理時(shí)做更少的迭代,進(jìn)行“零次(zero-shot)布局”。我們實(shí)際上還沒(méi)有新算法來(lái)優(yōu)化這個(gè)特定的設(shè)計(jì),當(dāng)然我們可以做數(shù)百次迭代以得到更好的結(jié)果。

上圖展示了使用不同方法時(shí)的布局成本。藍(lán)線表示不經(jīng)過(guò)預(yù)訓(xùn)練的從頭訓(xùn)練策略的布局成本,綠線表示用已預(yù)訓(xùn)練的算法優(yōu)化新設(shè)計(jì)塊的布局,X軸表示訓(xùn)練時(shí)間,可以看到,藍(lán)線在經(jīng)過(guò)20多小時(shí)的訓(xùn)練后方可大幅降低布局成本,此后仍需經(jīng)過(guò)一段時(shí)間才能達(dá)到收斂。而綠線只用了極少的訓(xùn)練時(shí)間就達(dá)到了更低的布局成本并很快收斂。

最令我感到興奮的是圈紅部分。調(diào)優(yōu)預(yù)訓(xùn)練策略在短時(shí)間內(nèi)就可實(shí)現(xiàn)相當(dāng)不錯(cuò)的布局,這種實(shí)現(xiàn)就是我所說(shuō)的,在一兩秒內(nèi)完成芯片設(shè)計(jì)的布局。

上圖展示了更詳細(xì)的不同設(shè)計(jì)的情況。Y軸表示線長(zhǎng)成本(越低越好)。綠色表示使用商業(yè)工具的線長(zhǎng)成本,可以看到,從淺藍(lán)色(零次布局)→藍(lán)色(2小時(shí)微調(diào))→深藍(lán)色(12小時(shí)微調(diào)),線長(zhǎng)成本越來(lái)越低。深藍(lán)色一直比黃色的線長(zhǎng)成本要低,因?yàn)橥ㄟ^(guò)12小時(shí)的微調(diào)能從其他設(shè)計(jì)中學(xué)到最佳布局。

上圖展示了更詳細(xì)的不同設(shè)計(jì)的情況。Y軸表示線長(zhǎng)成本(越低越好)。綠色表示使用商業(yè)工具的線長(zhǎng)成本,可以看到,從淺藍(lán)色(零次布局)→藍(lán)色(2小時(shí)微調(diào))→深藍(lán)色(12小時(shí)微調(diào)),線長(zhǎng)成本越來(lái)越低。深藍(lán)色一直比黃色的線長(zhǎng)成本要低,因?yàn)橥ㄟ^(guò)12小時(shí)的微調(diào)能從其他設(shè)計(jì)中學(xué)到最佳布局。

上圖中,左邊和右邊分別展示了從頭訓(xùn)練的策略和經(jīng)過(guò)微調(diào)預(yù)訓(xùn)練策略的芯片布局過(guò)程。每個(gè)小方塊表示一個(gè)宏的中心,空白部分表示為標(biāo)準(zhǔn)單元預(yù)留的位置。可以看到,右邊從一開(kāi)始就將宏放在邊緣,將大片中間區(qū)域留空。而左邊則要經(jīng)過(guò)很多次迭代才能形成這樣的格局。

我們利用強(qiáng)化學(xué)習(xí)工具針對(duì)TPU v5芯片的37個(gè)設(shè)計(jì)塊進(jìn)行了布局與布線。其中,26個(gè)設(shè)計(jì)塊的布局與布線質(zhì)量?jī)?yōu)于人類專家,7個(gè)設(shè)計(jì)塊的質(zhì)量與人類專家相近,4個(gè)設(shè)計(jì)塊的質(zhì)量不如人類專家。目前我們已經(jīng)把這個(gè)強(qiáng)化學(xué)習(xí)工具投入到芯片設(shè)計(jì)流程中了。

總的來(lái)說(shuō),用機(jī)器學(xué)習(xí)進(jìn)行芯片布局與布線的好處包括:可以快速生成多種布局方案;即使上游設(shè)計(jì)有重大改動(dòng)也可以迅速重新布局;大幅減少開(kāi)發(fā)新ASIC芯片所需的時(shí)間和精力。

驗(yàn)證

接下來(lái)是芯片設(shè)計(jì)的驗(yàn)證階段。我們希望用較少的測(cè)試次數(shù)覆蓋多個(gè)測(cè)試項(xiàng)目。驗(yàn)證是阻礙芯片設(shè)計(jì)提速的主要瓶頸。據(jù)估計(jì),芯片設(shè)計(jì)過(guò)程中,80%的工作量在于驗(yàn)證,而設(shè)計(jì)本身僅占20%。因此,驗(yàn)證技術(shù)的任何一點(diǎn)進(jìn)步都會(huì)產(chǎn)生重大作用。

Google在2021年NeurIPS(神經(jīng)信息處理系統(tǒng)大會(huì))上發(fā)表了論文《Learning Semantic Representations to Verify Hardware Designs》,我們能不能運(yùn)用機(jī)器學(xué)習(xí)生成在更短時(shí)間內(nèi)覆蓋更廣狀態(tài)空間的測(cè)試用例?

驗(yàn)證階段的基本問(wèn)題是可達(dá)性(reachability)。目前的芯片設(shè)計(jì)能否讓系統(tǒng)達(dá)成需要的狀態(tài)?我們的想法是,根據(jù)當(dāng)前的芯片設(shè)計(jì)生成一個(gè)連續(xù)的表示,從而預(yù)測(cè)對(duì)系統(tǒng)的不同狀態(tài)的可達(dá)性。

我們可以通過(guò)RTL將芯片設(shè)計(jì)抽象為一張圖,然后運(yùn)用基于圖的神經(jīng)網(wǎng)絡(luò)去了解該圖的特性,從而了解其對(duì)應(yīng)芯片設(shè)計(jì)的特性,繼而決定測(cè)試覆蓋率和測(cè)試用例,這給了我們一個(gè)很好的設(shè)計(jì)的抽象表示。

當(dāng)然,如何將這種方法應(yīng)用到實(shí)際芯片設(shè)計(jì)中將是另外一個(gè)重要話題。用RTL生成圖表示之后,我們?cè)趫D神經(jīng)網(wǎng)絡(luò)中運(yùn)用一種叫Design2Vec的技術(shù)進(jìn)行深度表示學(xué)習(xí),從而幫助我們作出預(yù)測(cè)。

目前,芯片的驗(yàn)證環(huán)節(jié)需要大量人力,例如,找bug、查找測(cè)試覆蓋率漏洞、分析和解決bug等,還需要經(jīng)歷多次如上圖所示的流程循環(huán)。我們希望上述步驟可以實(shí)現(xiàn)自動(dòng)化,自動(dòng)生成新的測(cè)試用例以解決重要的問(wèn)題。

后來(lái)我們發(fā)現(xiàn),可以把這個(gè)問(wèn)題轉(zhuǎn)化為一個(gè)監(jiān)督學(xué)習(xí)問(wèn)題。如果之前進(jìn)行了一系列測(cè)試,并知道這些測(cè)試覆蓋哪些測(cè)試點(diǎn),就可以將這些數(shù)據(jù)用作監(jiān)督學(xué)習(xí)中的訓(xùn)練數(shù)據(jù)。

然后,當(dāng)出現(xiàn)新的測(cè)試點(diǎn)時(shí),假設(shè)進(jìn)行一個(gè)新的測(cè)試,我們需要預(yù)測(cè)這個(gè)測(cè)試能否覆蓋新的測(cè)試點(diǎn)。我們希望能結(jié)合之前的訓(xùn)練數(shù)據(jù)以及芯片設(shè)計(jì)本身,來(lái)實(shí)現(xiàn)這種預(yù)測(cè)。

我們有兩個(gè)Baseline,其中一個(gè)能夠看到測(cè)試點(diǎn)(test points)和覆蓋點(diǎn)(cover points)的數(shù)據(jù),這是一個(gè)黑盒測(cè)試。

而Design2Vec除了能夠處理上述數(shù)據(jù)外,還能處理實(shí)際設(shè)計(jì)、設(shè)計(jì)的圖結(jié)構(gòu)等等。如果你使用一半的測(cè)試點(diǎn)作為訓(xùn)練數(shù)據(jù),并且設(shè)置多個(gè)大小不同的訓(xùn)練集,然后對(duì)其它測(cè)試點(diǎn)進(jìn)行預(yù)測(cè),那么將會(huì)得到非常出色的結(jié)果,即使是對(duì)于相對(duì)較少的覆蓋點(diǎn),也能泛化得非常好。相比之下,Baseline這種方法就不能對(duì)此進(jìn)行很好地泛化。

但使用圖神經(jīng)網(wǎng)絡(luò)來(lái)學(xué)習(xí)設(shè)計(jì)、覆蓋率和測(cè)試屬性的方法,實(shí)際上比NeurIPS論文中的其他所有Baseline都要好。

例如,我們常會(huì)遇到很多難以生成測(cè)試的覆蓋點(diǎn)。工程師們發(fā)現(xiàn)使用RISC-V Design和TPU Design這兩種不同的設(shè)計(jì)也很難為這些特定的覆蓋點(diǎn)生成測(cè)試,于是我們又轉(zhuǎn)向使用貝葉斯優(yōu)化器來(lái)嘗試生成測(cè)試。

上圖右邊這一列是貝葉斯優(yōu)化器覆蓋的不同測(cè)試點(diǎn)、覆蓋點(diǎn)所需的模擬器調(diào)用數(shù)(simulator calls),中間一列是使用Design2Vec所需的模擬器調(diào)用數(shù)。從中可以看到,為覆蓋這些有挑戰(zhàn)性的覆蓋點(diǎn),Design2Vec生成的測(cè)試要少于貝葉斯優(yōu)化器。所以Design2Vec非常好,相比之下它更快,能聚焦覆蓋范圍,還能節(jié)省在運(yùn)行計(jì)算模擬器(本身很昂貴)上的開(kāi)銷。

驗(yàn)證是芯片設(shè)計(jì)在理論和實(shí)踐上長(zhǎng)期面臨的一個(gè)挑戰(zhàn)。我們認(rèn)為,深度表示學(xué)習(xí)能夠顯著提高驗(yàn)證效率和質(zhì)量,并且在設(shè)計(jì)中實(shí)現(xiàn)泛化。

即使設(shè)計(jì)發(fā)生了一些改變,這個(gè)新設(shè)計(jì)的版本也能運(yùn)用之前在眾多設(shè)計(jì)上訓(xùn)練出來(lái)的系統(tǒng),提高驗(yàn)證效率。正如在布局與布線階段,經(jīng)過(guò)訓(xùn)練后的算法即使面對(duì)新設(shè)計(jì)也能夠預(yù)測(cè)不同測(cè)試的覆蓋點(diǎn),以帶來(lái)好的結(jié)果。

-

Google

+關(guān)注

關(guān)注

5文章

1757瀏覽量

57414 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1001瀏覽量

54812 -

硬件設(shè)計(jì)

+關(guān)注

關(guān)注

18文章

394瀏覽量

44530 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8377瀏覽量

132409 -

神經(jīng)網(wǎng)絡(luò)技術(shù)

+關(guān)注

關(guān)注

0文章

6瀏覽量

5286

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

機(jī)器學(xué)習(xí)如何影響計(jì)算機(jī)硬件設(shè)計(jì)2

機(jī)器學(xué)習(xí)如何影響計(jì)算機(jī)硬件設(shè)計(jì)2

評(píng)論