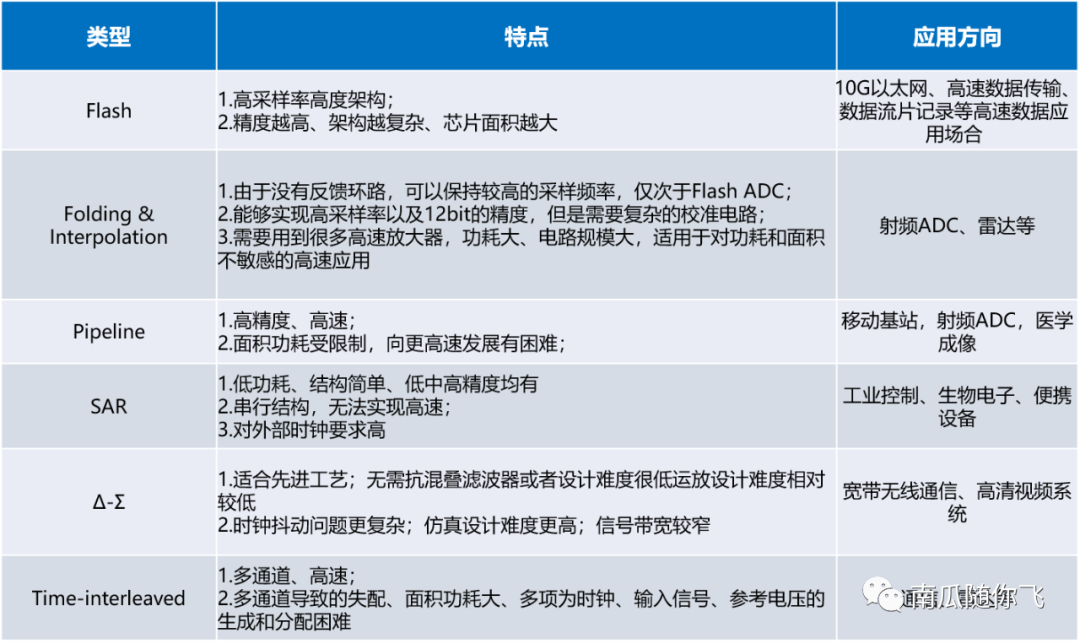

3.Pipeline

Pipeline ADC,流水線(xiàn)式ADC架構(gòu)。正如其名字一樣,采用了類(lèi)似于加工產(chǎn)線(xiàn)上的流水線(xiàn)生產(chǎn)流程和原理,將輸入信號(hào)進(jìn)行分段處理,然后逐個(gè)傳輸?shù)矫總€(gè)ADC完成對(duì)應(yīng)的采樣+量化的工作,最后拼接輸出。與Folding & Interpolation結(jié)構(gòu)不同,Pipeline將輸入信號(hào)在時(shí)間和空間上都進(jìn)行分段了,前者僅在空間上分段,然后并行處理兩路信號(hào)。

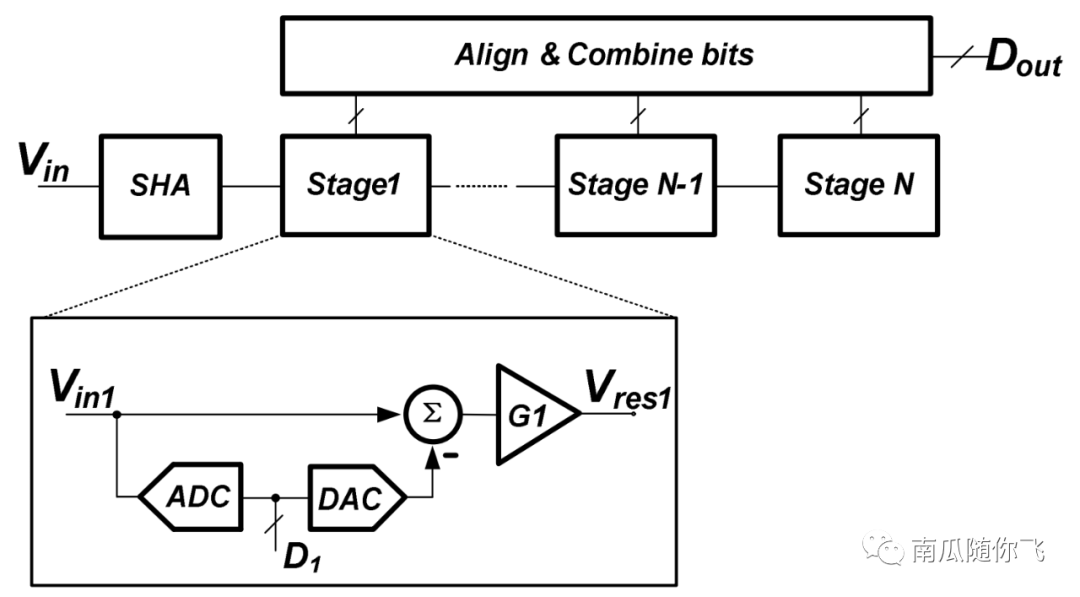

上圖所示為Pipeline ADC的基本結(jié)構(gòu),可以看到輸入信號(hào)需要經(jīng)過(guò)不同的流水線(xiàn)節(jié)點(diǎn)Stage。每一個(gè)Stage中包含了一個(gè)子ADC、一個(gè)子DAC以及一個(gè)殘差放大器(Residue Amplifier)。每一個(gè)Stage在前半個(gè)時(shí)鐘內(nèi)接收信號(hào)完成一次采樣,然后在后半個(gè)時(shí)鐘內(nèi)由子ADC完成量化,輸出量化結(jié)果D。

Pipeline ADC需要保證分段的量化在半個(gè)周期內(nèi)完成,同時(shí)其不想Flash或者Folding & Interpolation同時(shí)完成所有位數(shù)的量化,因此其在高精度的基礎(chǔ)上還可以保留一定的速度優(yōu)勢(shì),但是相對(duì)于Flash和Folding & Interpolation高速來(lái)說(shuō)稍顯不足。

主要的優(yōu)點(diǎn):

- 高精度:其每級(jí)的殘差放大可以抑制后級(jí)的誤差,類(lèi)似于射頻鏈路中的級(jí)聯(lián)噪聲作用,提高了整體的精度;分段結(jié)構(gòu)能夠更靈活的對(duì)每一位進(jìn)行校準(zhǔn),能夠達(dá)到10-16bit;

- 高速:目前可實(shí)現(xiàn)單通道250MS/s+16bit,1.5GS/s+12bit的性能,適用于基站、通信、雷達(dá)等應(yīng)用;

- 量化校準(zhǔn)方便,能夠通過(guò)靈活的校準(zhǔn)算法提高精度、降低功耗;

主要的缺點(diǎn):

- 隨著工藝制程不斷降低,晶體管的溝道效應(yīng)增強(qiáng),本征增益下降,放大器難以保持高增益,因此限制了殘差放大器的精度;

- 高速、高精度需要更高的功耗和更大的面積,系統(tǒng)的架構(gòu)也越發(fā)復(fù)雜,進(jìn)一步導(dǎo)致功耗和面積的增大;

- 流水線(xiàn)式的固有數(shù)據(jù)延遲特點(diǎn)使得其無(wú)法實(shí)時(shí)輸出當(dāng)前量化結(jié)構(gòu),使其無(wú)法朝向更高速的應(yīng)用場(chǎng)景發(fā)展;

高速Pipeline ADC發(fā)展趨勢(shì):

- 低功耗:功耗是限制傳統(tǒng)Pipeline ADC發(fā)展的瓶頸問(wèn)題,降低功耗也是研制高速、高精度Pipeline ADC的重要方向;

- 混合結(jié)構(gòu):為實(shí)現(xiàn)兼容高速、高精度、低功耗的特點(diǎn),往往采用了混合結(jié)構(gòu)實(shí)現(xiàn),例如Pipeline+SAR可以實(shí)現(xiàn)低功耗和中高精度;Pipeline+ Δ-Σ ,可以實(shí)現(xiàn)高精度;

4.SAR

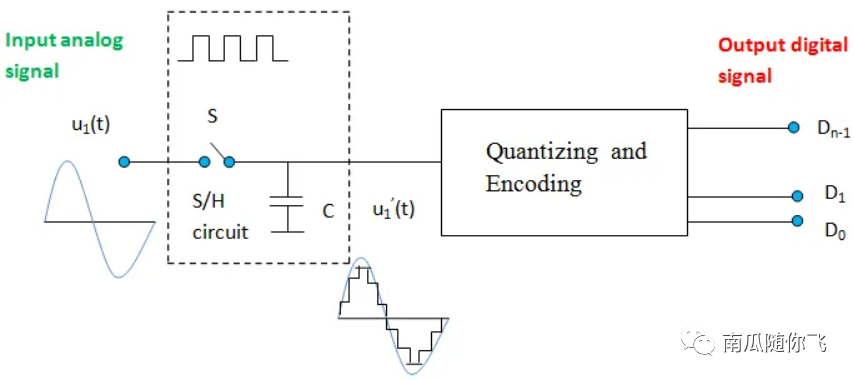

Successive-approximation Register,SAR,逐次逼近式ADC。傳統(tǒng)架構(gòu)的SAR式時(shí)間同步取樣,主要優(yōu)勢(shì)低功耗、結(jié)構(gòu)簡(jiǎn)單、低中高精度均有,能夠應(yīng)用在工業(yè)控制、生物電子、便攜設(shè)備中。

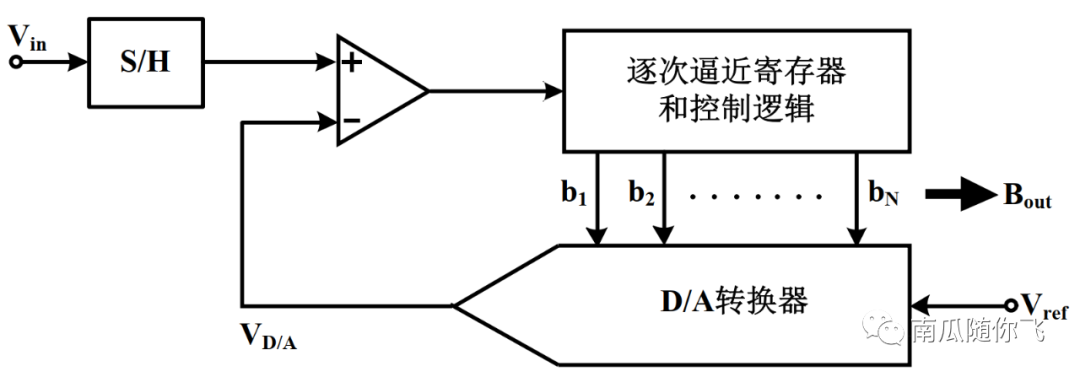

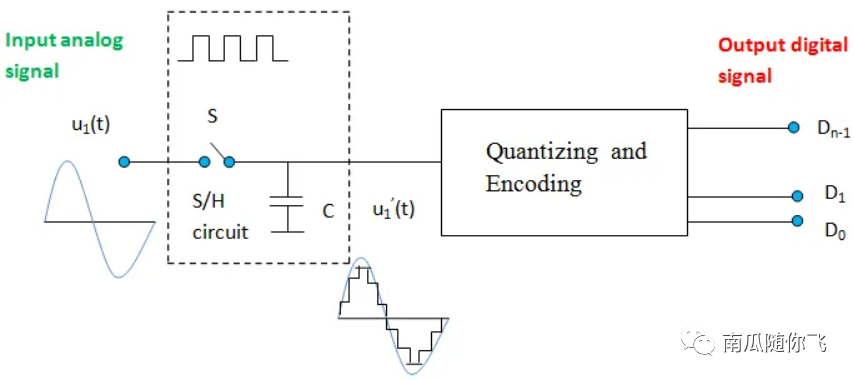

由采樣+保持電路、逐次逼近寄存器、控制邏輯、DAC構(gòu)成。舉個(gè)列子來(lái)說(shuō)明其工作流程和原理。

由采樣+保持電路、逐次逼近寄存器、控制邏輯、DAC構(gòu)成。舉個(gè)列子來(lái)說(shuō)明其工作流程和原理。

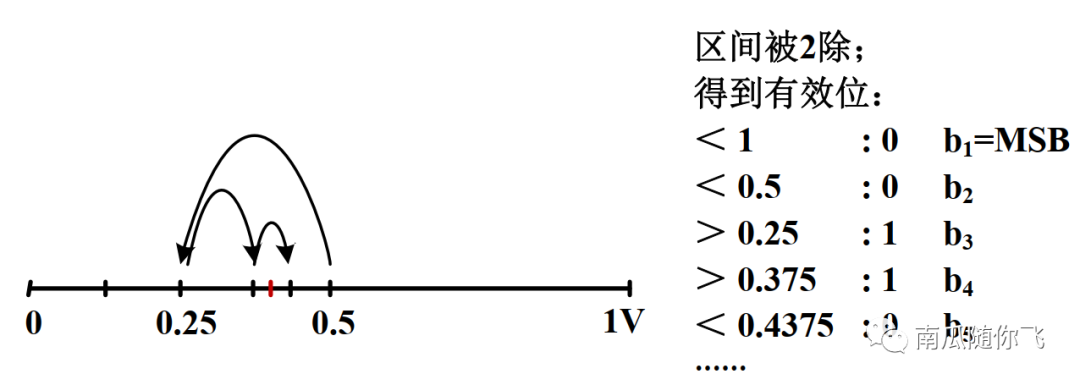

假設(shè)輸入電壓是0.4V(參考電壓為1V)。

1)第一次比較,0.4V <1V,最高有效位為0;

2)二分區(qū)間,輸入電壓與<0.5V 相比較,再次產(chǎn)生一個(gè)0;

3)二分區(qū)間,輸入電壓>0.25V 相比較,有效位為1;

4)1作為控制信號(hào),將比較值從0.25V 選為0.375V,而不是0.125V;

5)比較程序繼續(xù)N 次,得到N 位輸出。

主要缺點(diǎn):

- 逐次逼近是串行結(jié)構(gòu),使得其無(wú)法實(shí)現(xiàn)高速采樣;

- 同步時(shí)鐘電路控制,模塊之間傳遞信號(hào)存在較多等待;

- 基于分頻的時(shí)鐘控制,外部時(shí)鐘頻率要高于內(nèi)部采樣時(shí)鐘N+1倍或以上;

采用異步時(shí)鐘的結(jié)構(gòu)能夠有效解決其關(guān)鍵問(wèn)題:外部時(shí)鐘無(wú)需N+1倍于內(nèi)部采樣時(shí)鐘,降低了對(duì)外部時(shí)鐘速度和精度的要求,簡(jiǎn)化了電路設(shè)計(jì);異步時(shí)鐘下電路模塊在傳遞信號(hào)的時(shí)候沒(méi)有等待問(wèn)題,時(shí)間延遲小。因此異步時(shí)鐘的SAR ADC是目前SAR ADC的主流解決方案。

5.Δ-Σ

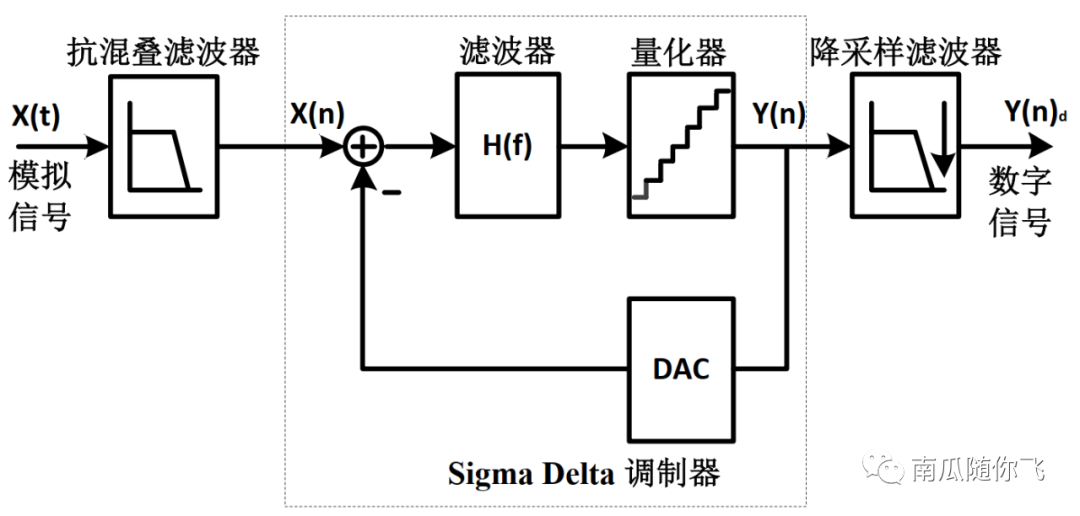

Δ-Σ ,增量累加ADC。與其他幾種ADC不同,這一類(lèi)ADC成為過(guò)采樣ADC,其采樣率遠(yuǎn)大于2倍信號(hào)最高頻率,根據(jù)應(yīng)用場(chǎng)合的不同范圍從20-1000。其他結(jié)構(gòu)如下圖所示。

信號(hào)的采樣率越高,噪聲對(duì)信號(hào)信息的影響就越小,SNR也隨著過(guò)采樣率的提高而提高,因此ADC的分辨率也會(huì)提高。Δ-Σ 就是通過(guò)速度來(lái)?yè)Q取高分辨的一種架構(gòu)。其采樣進(jìn)度能夠達(dá)到24bit。

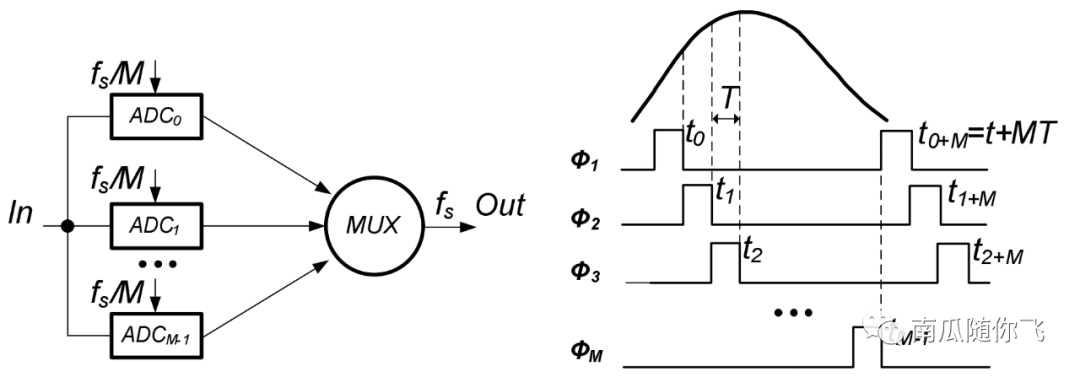

6. Time-interleaved

Time-interleaved,時(shí)間交織ADC。時(shí)間交織的核心思想是兩點(diǎn):多路處理+時(shí)鐘交織。其結(jié)構(gòu)如下圖所示。M個(gè)采樣率為fs/M的ADC階梯式并行采樣。在第一個(gè)采樣時(shí)鐘信號(hào)到達(dá)的時(shí)候把第一個(gè)采樣值傳遞個(gè)ADC0,第二個(gè)時(shí)鐘周期來(lái)到的時(shí)候把第二個(gè)采樣值傳遞給ADC1,這樣類(lèi)推。

Time-interleaved ADC是目前實(shí)現(xiàn)多通道ADC采樣的方案,是實(shí)現(xiàn)高速ADC的重要方案。但是面臨由多通道導(dǎo)致的失配、面積功耗大、多項(xiàng)為時(shí)鐘、輸入信號(hào)、參考電壓的生成和分配困難等問(wèn)題。

-

adc

+關(guān)注

關(guān)注

98文章

6438瀏覽量

544098 -

dac

+關(guān)注

關(guān)注

43文章

2271瀏覽量

190840 -

模擬信號(hào)

+關(guān)注

關(guān)注

8文章

1117瀏覽量

52403 -

數(shù)據(jù)轉(zhuǎn)換芯片

+關(guān)注

關(guān)注

0文章

5瀏覽量

1093

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ADC外圍電路的設(shè)計(jì)

ADC外圍電路設(shè)計(jì)方法

如何在MSP430G2中使用ADC使用Energia IDE讀取模擬電壓

如何使用LTspice模擬 SAR ADC 模擬輸入?

實(shí)用模擬電路設(shè)計(jì)技術(shù)Section4高速采樣ADC

模擬量模塊K2-04ADC和K2-02DAC技術(shù)資料

如何對(duì)ADC中的電源抑制PSR進(jìn)行有效測(cè)量 (2)

ADC數(shù)字地和模擬地的接地原理

終于搞懂模擬電路中的ADC!1

終于搞懂模擬電路中的ADC!3

終于搞懂模擬電路中的ADC!4

ADC模擬電路皇冠上的明珠(1)

遠(yuǎn)場(chǎng)應(yīng)用中的模擬麥克風(fēng)和ADC系統(tǒng)

終于搞懂模擬電路中的ADC!2

終于搞懂模擬電路中的ADC!2

評(píng)論