工作模式有三種:分別為四通道模式、雙通道模式以及單通道模式,這里先簡(jiǎn)單講述雙通道模式(由于工程中用過(guò)雙通道模式);

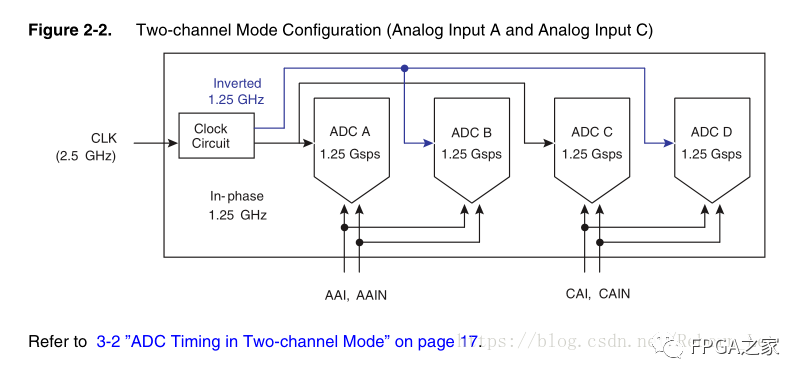

雙通道模式組態(tài):

從這張圖中可以得到的信息是什么呢?

首先有兩個(gè)模擬輸入,分別為AAI,AAIN(這是一個(gè)模擬輸入 Analog Input A)和CAI,CAIN(Analog Input C),根據(jù)實(shí)際工程需要,選擇使用A輸入端口,或者C輸入端口,或者兩個(gè)都用。

當(dāng)信號(hào)從A輸入端口輸入時(shí),就意味著使用ADC A和ADC B通道對(duì)輸入的模擬信號(hào)進(jìn)行采樣,雙通道組態(tài)內(nèi)部時(shí)鐘電路(Clock Circuit)為ADC A通道提供內(nèi)部采樣時(shí)鐘,該時(shí)鐘反轉(zhuǎn)180°為ADC B通道提供采樣時(shí)鐘。這兩個(gè)時(shí)鐘的關(guān)系是由同一個(gè)外部時(shí)鐘源產(chǎn)生時(shí)鐘,因此時(shí)鐘頻率一致,但是相位完全相反。

當(dāng)外部信號(hào)從C輸入端口輸入時(shí),分析方法一致。

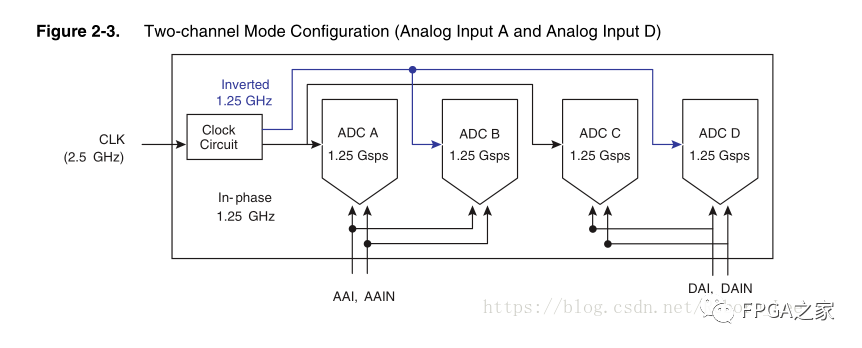

上圖和圖2-2是類(lèi)似的,都是雙通道模式的構(gòu)造,不同的僅僅是模擬輸入端口變成了A和D;

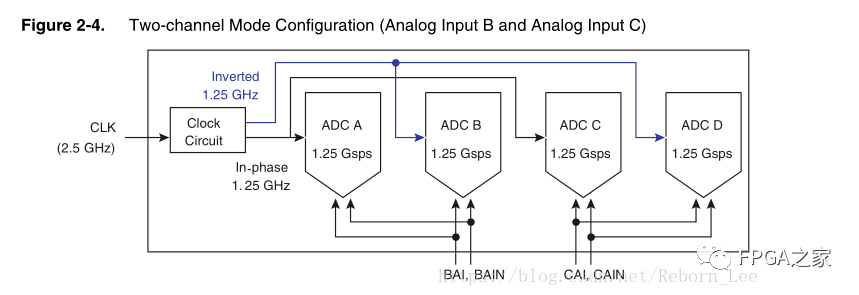

同理,見(jiàn)下圖:

模擬輸入端口分別為B和C;

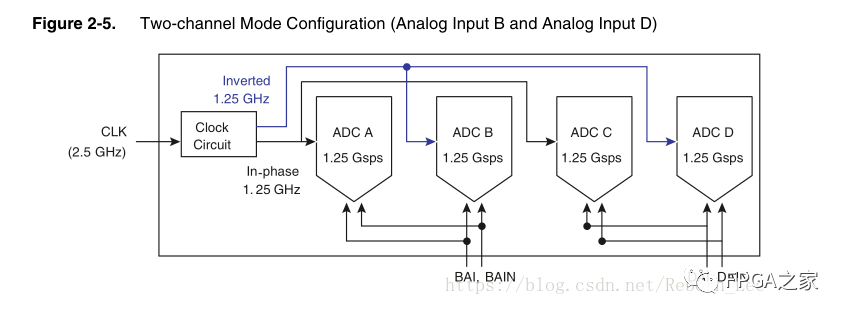

還有:

模擬輸入端口為B和D;

好了,雙通道模式框架就這些。

接下來(lái)的問(wèn)題是信號(hào)是如何采樣的?以及采樣后的信號(hào)是如何同步的?

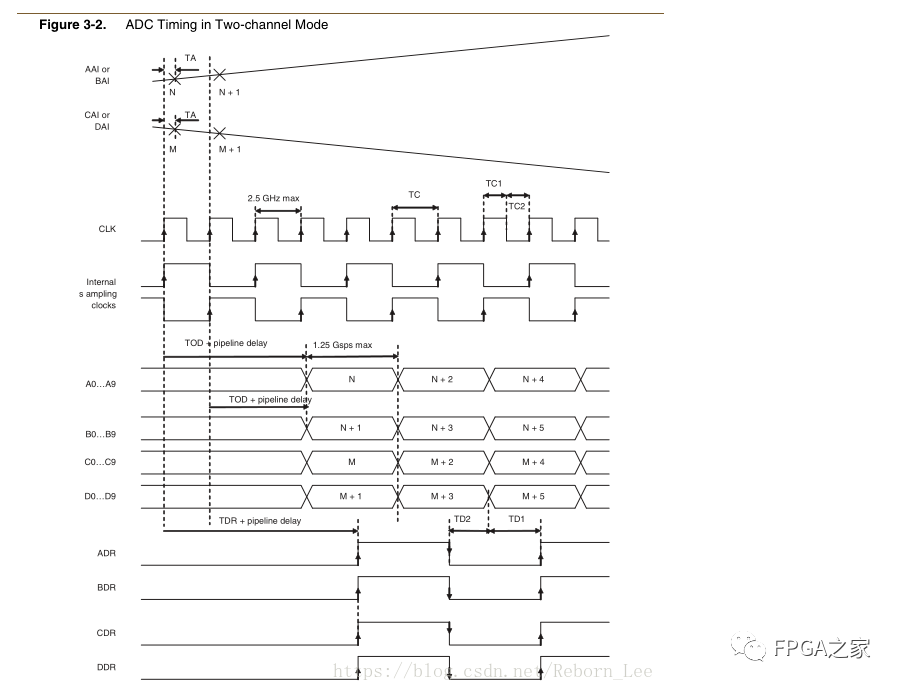

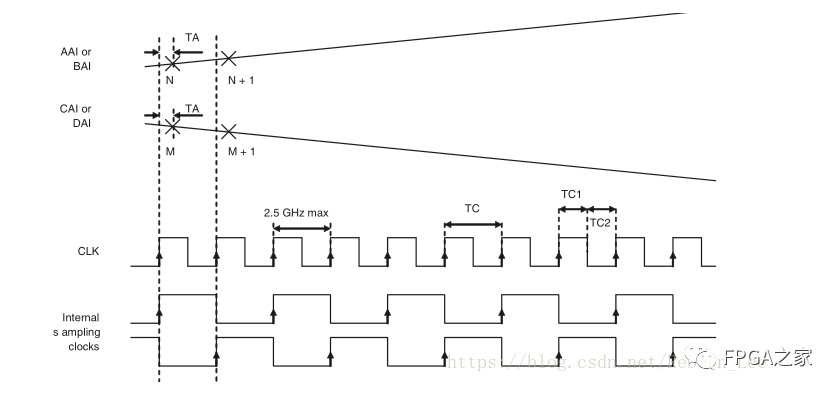

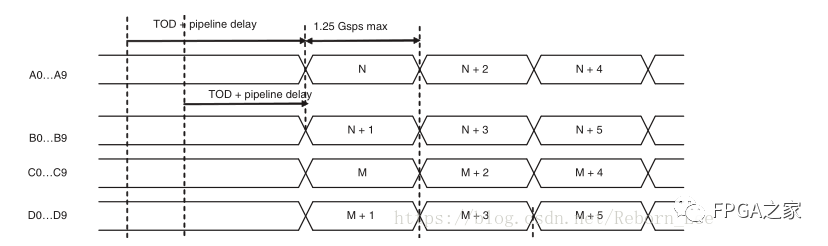

見(jiàn)下圖:

雙通道模式的ADC時(shí)序圖

(作為一個(gè)對(duì)硬件一竅不通的萌新小白,以前看到這種圖基本上都是略過(guò),我不知道它畫(huà)的是什么,也就是不能從圖中得到需要的信息,這里不得不感謝我的師兄,他耐心地教會(huì)了我很多有關(guān)硬件的東西,讓我的知識(shí)從此處的空白變得不在蒼白,我想我會(huì)觸類(lèi)旁通,通過(guò)這次機(jī)會(huì)學(xué)會(huì)更多的東西。也要感謝我的導(dǎo)師,他給了我機(jī)會(huì),平臺(tái)去接觸這方面的知識(shí)。說(shuō)實(shí)話(huà),真的很感謝這些幫助過(guò)我的人,我覺(jué)得自己很幸運(yùn),我會(huì)珍惜。也許有時(shí)候說(shuō)話(huà)的方式不對(duì),還請(qǐng)見(jiàn)諒!還有已經(jīng)畢業(yè)的師兄,你給我提出了很多真誠(chéng)的問(wèn)題,讓我認(rèn)識(shí)到時(shí)間的緊迫性以及自身的差距!)

我將詳細(xì)地將我知道的把這張圖分解開(kāi)來(lái)認(rèn)識(shí):

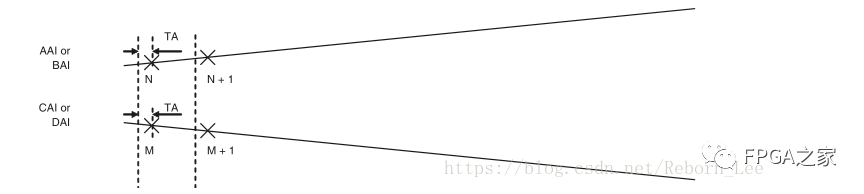

首先是這兩條斜線,代表模擬輸入的信號(hào),很容易地可以知道上方的模擬輸入是從A或者B輸入端口輸入的模擬信號(hào),下面的斜線代表C或D端口輸入的模擬信號(hào);

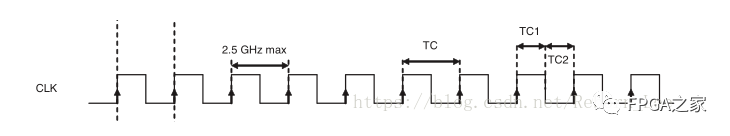

接著便是基準(zhǔn)時(shí)鐘CLK:

該時(shí)鐘最大的頻率為2.5GHz;

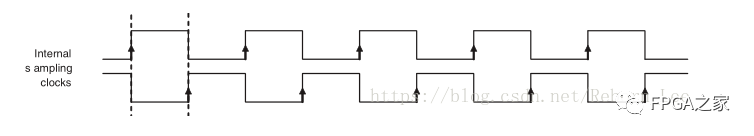

該時(shí)鐘經(jīng)過(guò)二分頻,得到如下兩個(gè)時(shí)鐘,稱(chēng)為內(nèi)部采樣時(shí)鐘,這樣內(nèi)部采樣時(shí)鐘的頻率變?yōu)樽畲?.25GHz:

這兩個(gè)時(shí)鐘頻率相等,相位相反;

時(shí)鐘上升沿到達(dá)時(shí)采樣;

這兩個(gè)內(nèi)部采樣時(shí)鐘的上升沿采樣,合起來(lái)最大采樣頻率相當(dāng)于2.5GHz了。

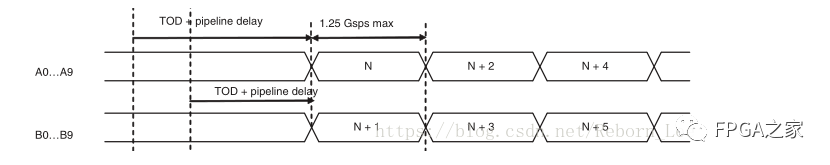

再整個(gè)看下面這幅圖:

假如模擬信號(hào)是從A或B端口輸入的,內(nèi)部采樣時(shí)鐘上升沿到達(dá)時(shí),對(duì)模擬信號(hào)進(jìn)行采樣,第一個(gè)上升沿到達(dá)時(shí)采樣數(shù)據(jù)為N,第二個(gè)上升沿到達(dá)時(shí),采樣數(shù)據(jù)為N+1,以此類(lèi)推即可。

假如模擬信號(hào)是從C或D端口輸入的,采樣原理同上,采樣數(shù)據(jù)表示為M,M+1等。

不如將內(nèi)部時(shí)鐘標(biāo)記為clk1和clk2(上下),clk1的第一個(gè)上升沿到達(dá)時(shí),采樣數(shù)據(jù)為上圖的N,clk2的第一個(gè)上升沿到達(dá)時(shí),采樣數(shù)據(jù)為N+1,clk1的第二個(gè)上升沿到達(dá)時(shí),采樣數(shù)據(jù)為N+2,clk2的第二個(gè)上升沿到達(dá)時(shí),采樣數(shù)據(jù)為N+3,以此類(lèi)推!

好像這樣描述會(huì)更加的詳細(xì)!

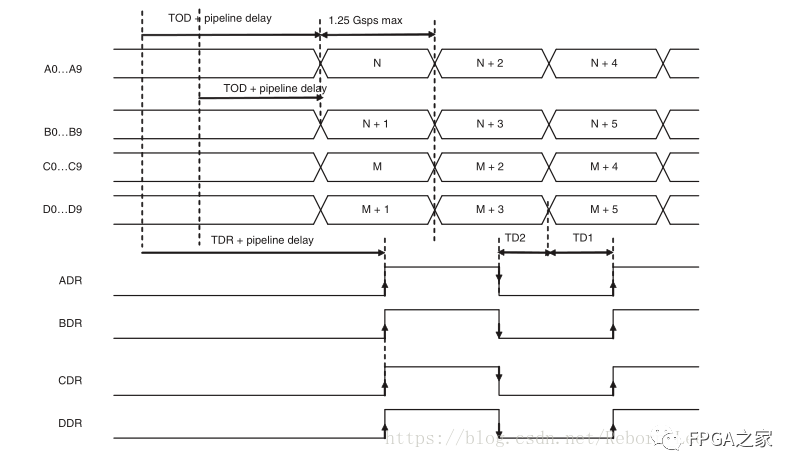

ADC采樣芯片采取流水線模式,當(dāng)采樣到信號(hào)時(shí),芯片內(nèi)部發(fā)出一個(gè)同步使能信號(hào),表示有了采樣數(shù)據(jù),該同步了數(shù)據(jù)了,數(shù)據(jù)同步到哪里呢?例如可以同步到FPGA內(nèi)部,以供測(cè)量或處理!

所謂的流水線結(jié)構(gòu),就是邊采樣邊同步,這樣可以加快處理速度,提高效率!

同步時(shí)鐘有效時(shí),進(jìn)行數(shù)據(jù)同步:

從這幅圖也可以看出,同步時(shí)鐘是內(nèi)部采樣時(shí)鐘頻率的1/2,也就是外面基準(zhǔn)時(shí)鐘頻率的1/4,可以認(rèn)為這個(gè)時(shí)鐘是基準(zhǔn)時(shí)鐘4分頻得到的。

若采用的是A或者B輸入端口輸入,假設(shè)是A端口輸入,則上面同步時(shí)鐘有效(ADR/BDR),理想情況下ADR與BDR是一樣的,數(shù)據(jù)同步上升沿和下降沿都有效,即上升沿到來(lái)時(shí)同步一個(gè)數(shù)據(jù),下降沿到來(lái)時(shí)同步一個(gè)數(shù)據(jù),具體的過(guò)程是這樣的,ADR的上升沿到來(lái)時(shí),同步數(shù)據(jù)N,BDR的上升沿到達(dá)時(shí),同步數(shù)據(jù)N+1,ADR的下降沿到達(dá)時(shí),同步數(shù)據(jù)N+2,BDR的下降沿到達(dá)時(shí),同步數(shù)據(jù)N+3,如此繼續(xù)下去。

雖然自己做的工程,沒(méi)有涉及單通道、以及四通道,但是我想還是有必要去寫(xiě)一下這方面的理解,看看能不能觸類(lèi)旁通,還有想法把單通道以及四通道的部分模塊Verilog HDL代碼寫(xiě)一下。

為了方便大家看到原汁原味的英文數(shù)據(jù)手冊(cè),這里貼出來(lái)吧,想了解更多的可以直接看數(shù)據(jù)手冊(cè)!數(shù)據(jù)手冊(cè)

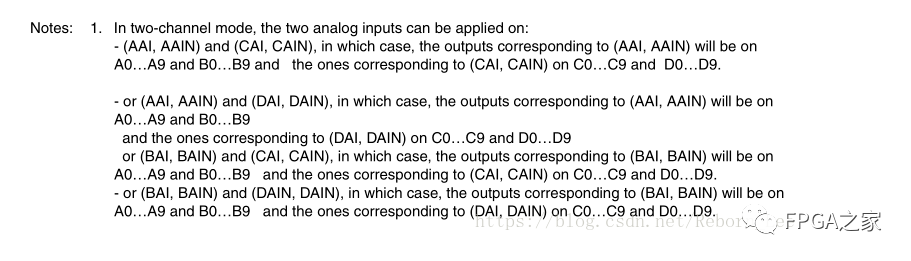

實(shí)際上,數(shù)據(jù)手冊(cè)中也說(shuō)了:

簡(jiǎn)單地解讀一下就是,雙通道模式中,兩個(gè)模擬輸入可以是以下這幾種情況:

(AAI,AAIN)和(CAI和CAIN),在這種情況下,相對(duì)于輸入(AAI,AAIN)端口的采樣輸出是(A0...A9)和(B0...B9),在根據(jù)上圖:

從中可以看出,(A0...A9)和(B0...B9)不就是N,N+1,...嗎?只不過(guò)每一個(gè)采樣數(shù)據(jù)用10位二進(jìn)制數(shù)來(lái)表示罷了。

第二、第三、第四中情況我就不多說(shuō)了,幾乎一模一樣!

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421786 -

adc

+關(guān)注

關(guān)注

98文章

6430瀏覽量

544078 -

二進(jìn)制

+關(guān)注

關(guān)注

2文章

793瀏覽量

41597

原文標(biāo)題:解讀ADC采樣芯片(EV10AQ190A)的采樣(工作)模式(雙通道模式)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

解讀ADC采樣芯片(EV10AQ190A)的工作模式(四通道模式)

EV10AQ190AVTPY 模擬多路復(fù)用器現(xiàn)貨

解讀ADC采樣芯片(EV10AQ190A)的工作模式(單通道模式)

ADC10模塊的寄存器及其工作模式

請(qǐng)問(wèn)CH582的ADC DMA多通道采樣如何配置?

重復(fù)采樣模式,單次采樣模式,自動(dòng)模式與觸發(fā)模式

高速adc四路光纖

EV12AQ600/EV12AQ605數(shù)模轉(zhuǎn)換器介紹

單通道 / 雙通道、14 位 250Msps ADC 系列提供高 SFDR 欠采樣性能

STM32F4時(shí)鐘觸發(fā)ADC雙通道采樣DMA傳輸進(jìn)行FFT+測(cè)頻率+采樣頻率可變+顯示波形(詳細(xì)解讀)...

STM32的ADC多通道采樣

STM8單片機(jī)ADC連續(xù)采樣模式

解讀ADC采樣芯片(EV10AQ190A)的采樣(工作)模式(雙通道模式)

解讀ADC采樣芯片(EV10AQ190A)的采樣(工作)模式(雙通道模式)

評(píng)論