在過去的幾十年里,電子通信行業一直是 FPGA 市場增長背后的重要推動力,并將繼續保持下去。這背后的一個主要原因是 FPGA 中內置了許多不同的高速接口,以支持各種通信標準/協議。實現這些標準所涉及的底層輸入-輸出 PHY 技術是串行器-解串器 (SerDes) 技術。FPGA 作為一項技術從一開始就很復雜且具有挑戰性,甚至在考慮高速接口之前也是如此。

SerDes PHY 設計本身就很復雜且具有挑戰性。當這兩者結合在一起時,實施會變得更加棘手,這通常是將最先進的 SerDes 設計整合到 FPGA 中的原因。但如果現狀可以改變呢?這是 Alphawave IP 和 Achronix 之間合作努力的目標,其結果于 10 月在臺積電 OIP 論壇上公布。

將高端 SerDes 集成到 FPGA 中的挑戰

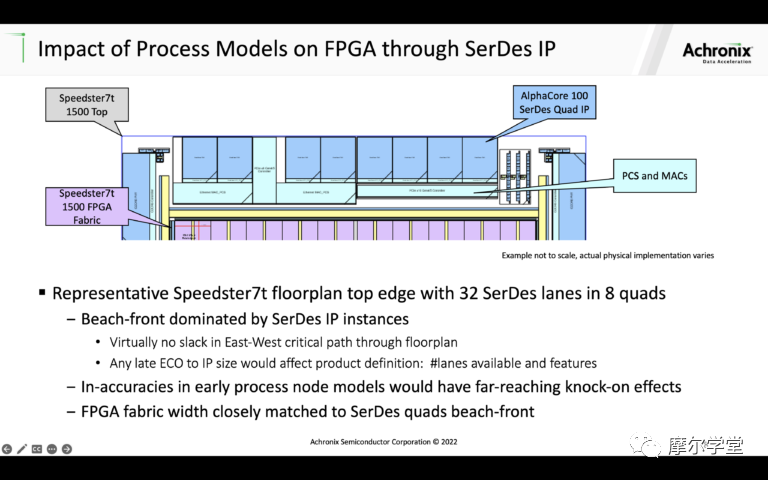

SerDes 和 FPGA 結構之間的相互依賴性可能會給集成芯片帶來布局規劃挑戰。除了布局挑戰之外,即使結構和 SerDes 之間金屬堆疊選擇的微小差異也可能對這些組件中的任何一個的功率、性能和面積 (PPA) 產生不利影響。

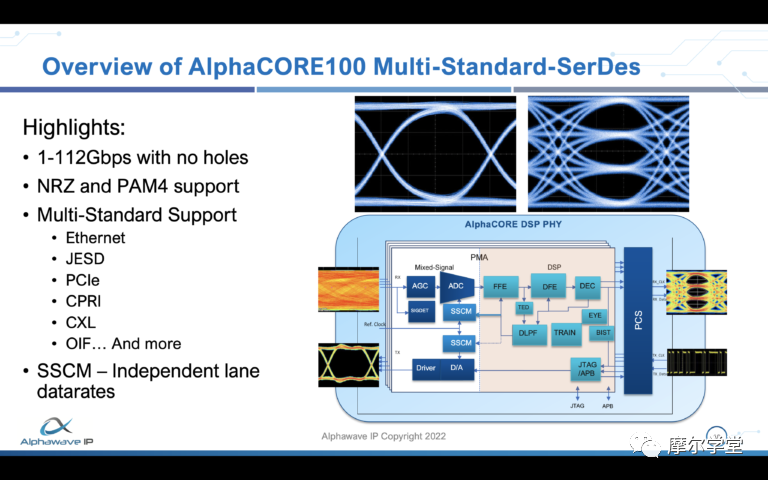

FPGA 必須支持大量線路速率和協議以及具有不同電氣通道要求的協議變體。線路速率范圍從 1Gbps 到 112Gbps,使用 NRZ 或 PAM4 信號方案來提供速度性能。這種組合要求給用于模擬的建模帶來了沉重的負擔。每個線路速率/協議組合都需要根據高精度模型在硅前和硅后進行驗證。

成功集成的要求

無論是 SerDes 還是 FPGA 結構,都會進行架構增強,這將影響 SerDes 與 FPGA 結構的集成。為避免在集成時出現意外,需要盡早討論架構并達成一致,以便可以開發適當的模擬模型進行驗證。過于樂觀的模型會迫使架構發生根本變化,而悲觀的模型會提供 PPA 無競爭力的解決方案。這兩種情況都不可取。

SerDes IP 供應商和 FPGA 集成商之間的密切合作需要盡早開發準確的模型。還需要密切合作以確保最佳布局規劃、電源規劃、凸點圖規劃、時序等。

Alphawave IP 和 Achronix 合作的范圍

Achronix 的高端 FPGA 支持 1GbE 到 400GbE、PCIe Gen5 等多標準協議,包括支持非標準速度(例如 82Gbps)的自定義協議。SerDes 112 Gbps 使用與 56Gbps SerDes 不同的架構,并使用 PAM4 信令方案。該設計使用數字 ADC,并且是圍繞基于 DSP 的架構構建的。

合作的目標是實現 Alphawave IP 的 AlphaCORE100 多標準 SerDes 與 Achronix 的 Speedster7t FPGA 結構的成功集成。

測試芯片

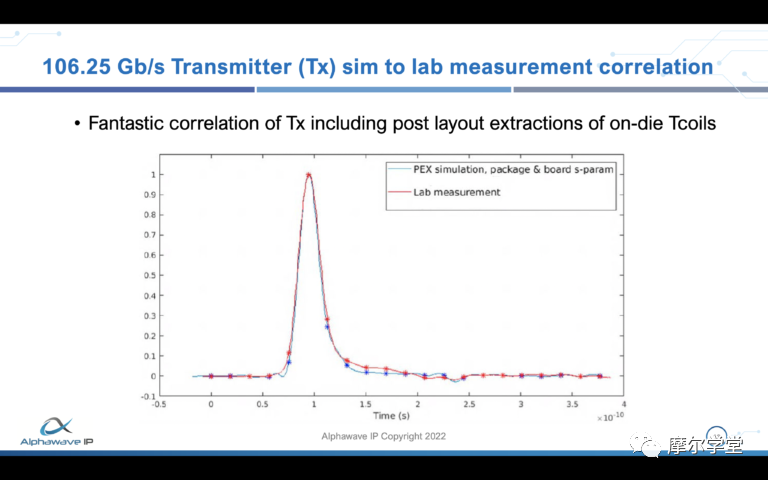

構建了一個測試芯片來驗證早期的 sim 模型。測試芯片采用 TSMC 的 N7 工藝實現,包括四個數據通道、完整的 AFE、數字 PLL 和 DLL、BIST 以及用于表征的附加測試電路。

成功的結果

如下圖所示,基于通過協作開發的早期模型的仿真結果與實驗室中的測試芯片測量結果非常相關。高精度模型使 Achronix 能夠使用 Alphawave IP 的 AlphaCore100 SerDes IP 生產一次成功的 Speedster7t FPGA,以支持 PCIe Gen5x16 和 Gen5x8 以及 400GbE。

完整仿真的結果也與實驗室針對各種信道損耗條件的 BER 測量結果密切相關。

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601850 -

解串器

+關注

關注

1文章

104瀏覽量

13225 -

SerDes

+關注

關注

6文章

197瀏覽量

34854 -

PAM

+關注

關注

2文章

52瀏覽量

13290

原文標題:高端 SerDes集成到FPGA中的挑戰!

文章出處:【微信號:moorexuetang,微信公眾號:摩爾學堂】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于京微雅格低功耗FPGA的8b/10b SERDES的接口設計

高端SerDes集成到FPGA中的挑戰

ASP4644在FPGA SERDES供電中的應用

FPGA SERDES接口電路怎么實現?

SerDes是怎么工作的

SERDES在數字系統中高效時鐘設計方案

教你如何進行Xilinx SerDes調試

基于FPGA芯片的SERDES接口電路設計

FPGA與IOT的快速發展 SerDes接口技術大顯身手

基于FPGA芯片的SERDES接口電路設計

淺析高端SerDes集成到FPGA中的挑戰

淺析高端SerDes集成到FPGA中的挑戰

評論