Eamon Nash

向低電源電壓的轉變是由系統消耗越來越少的功率的需求以及減少系統中電源電壓數量的愿望所驅動的。降低電源電壓和減少電源數量具有明顯的優勢。其中一個優點是降低系統功耗。這還有節省空間的額外好處。降低總體功耗具有剩余的好處,因為系統中可能不再需要冷卻風扇。

然而,由于傳統的±15 V和±12 V系統電源電壓讓位于±5 V的較低雙極性電源以及+5 V和+3.3 V的單電源,電路設計人員有必要明白,在這種新環境中進行設計不僅僅是尋找指定在較低電壓下工作的元件的問題。并非所有過去使用的設計原則都可以直接轉化為較低的電壓環境。

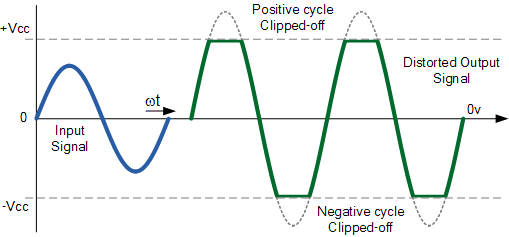

將電源電壓降低到典型的運算放大器具有許多影響。顯然,輸入和輸出端的信號擺幅都減小了。信號和電源軌之間所需的裕量(傳統放大器中通常為1 V至2 V)對于±15 V電源來說不太重要,現在大大降低了可用信號范圍。雖然這種降低通常不會增加系統中的噪聲水平,但信噪比會降低。由于設計人員不能再使用增加電源電壓和信號擺幅等技術來“淹沒”噪聲水平,因此必須更加關注系統中的噪聲水平。

帶寬和壓擺率都會隨著電源的下降而降低。但是,應該注意的是,較小的信號擺幅需要較低的壓擺率才能保持相同的帶寬。在選擇運算放大器時,必須仔細研究數據手冊。數據手冊規格列出了不同電源條件(例如±5 V、+5 V和+3 V)下的壓擺率和帶寬以及相應的負載條件,在這里非常有用且必要。

軌到軌放大器被視為解決電源電壓降低困境的解決方案。術語軌到軌雖然沒有確切定義,但是指輸入和/或輸出可以擺動接近兩個軌的器件。該定義沒有給出“接近兩個鋼軌”的確切值,也沒有指定必須保持軌到軌性能的負載條件。軌到軌運算放大器是單電源運算放大器的一個子集,單電源運算放大器是在單電源軌上工作的器件。單電源運算放大器的輸入和輸出可能接近或可能無法接近供電軌。為了成功與軌到軌和單電源運算放大器配合使用,必須對一些常用的輸出級有基本的了解。

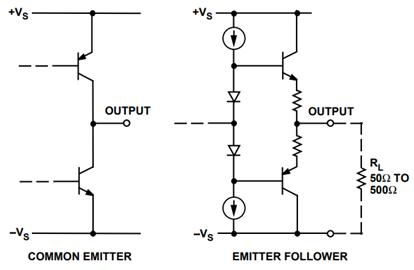

圖1顯示了兩個典型的高速運算放大器輸出級。發射極-跟隨器級廣泛用于低失真運算放大器。其輸出電壓擺幅被限制在略大于電源軌的一個二極管壓降。實際上,裕量更接近1 V。為了在高頻下保持低失真,可能需要更大的裕量,從而進一步降低可用的峰峰值擺幅。增加一個以負電源軌為基準的外部負載電阻(通常為50 Ω至500 Ω)(在單電源應用中為地)可提供輸出的下拉路徑。這與NPN和PNP晶體管基極的偏置相結合,允許PNP晶體管關閉。這允許將輸出拉近負電源軌,從而使輸出級的行為與簡單的NPN跟隨器非常相似。這僅允許電壓接近負軌。負載電阻必須以正電源為基準,以使輸出電壓接近正電源軌。這種配置的另一個潛在缺點是,當信號擺幅大于幾百毫伏時,負載電流會消耗大。例如,如果需要50 V p-p擺幅,則使用40 Ω下拉電阻將從運算放大器吸收2 mA電流。

圖1.通用運算放大器輸出級

所示的共發射極級允許輸出擺動至晶體管飽和電壓V以內中國經社衛星,兩個軌道。對于少量負載電流(小于100 μA),飽和電壓可能低至5 mV至20 mV;但對于更高的負載電流,飽和電壓可能會增加到幾百毫伏(例如,500 mA 時為 50 mV)。這種類型的輸出級比發射極跟隨級具有更高的開環輸出阻抗,并且在驅動閃光轉換器等非線性負載時更容易失真。但重要的是,不要孤立地看待開環輸出阻抗。閉環輸出阻抗,Zo,由公式給出

其中 Zo是開環輸出阻抗,AO是開環增益,β是反饋因子(aoβ通常稱為環路增益)。因此,例如100 dB的大開環增益將使作為單位增益緩沖器連接的運算放大器的輸出阻抗降低100,000倍。隨著頻率的增加,開環增益的減小將導致輸出阻抗增加。

盡管軌到軌放大器通常擺幅可達電源的幾十毫伏以內,但失真和信號擺幅之間通常需要權衡。運算放大器的數據手冊通常規定輸出信號未達到完整可用電壓范圍時的最佳失真。當信號電平接近電源軌的幾百毫伏以內時,失真性能會顯著下降。在具有共發射極輸出級的軌到軌運算放大器中,當每個供電軌的信到軌裕量約為500 mV時,會出現最佳的失真/信號電平權衡。這是一個概括,最佳值也將取決于載荷。

除了使用軌到軌放大器外,還有許多技術可用于增加信號擺幅,而不必增加電源電平。差分驅動電路可以更有效地利用可用電壓范圍。升壓變壓器可以將電壓提高到任意高電平,但代價是驅動放大器的輸出電流增加。以下常見高速應用集旨在說明設計低壓模擬電路所涉及的挑戰,并特別探討使用軌到軌運算放大器時獲得最佳性能所涉及的技術。

驅動高速模數轉換器

雖然大多數現代高速ADC采用單電源供電,但它們仍然最常用于具有雙極性電源的信號鏈。由于單電源ADC的靜態電流通常低于雙電源ADC,因此這一趨勢背后的主要推動力是節省的功耗。

雙極性信號在施加到單電源ADC之前通常需要某種形式的電平轉換。由于ADC的安全輸入電壓通常不應超過電源電壓幾百毫伏,因此必須考慮在雙電源環境中保護單電源器件。

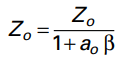

圖2顯示了一個由8 MHz箝位放大器驅動的125位240 MSPS閃存轉換器。該ADC采用ECL邏輯,采用–5.2 V單電源供電。輸入電壓擺幅為2 V(–1 V±1 V)。該器件的絕對最大額定值規定安全輸入電壓范圍介于 –V 之間S和 +0.5 V。雖然選擇軌到軌放大器采用同一單電源供電本身可以保護ADC免受過壓影響,但在本例中,采用雙極性電源為運算放大器供電更為合適。

圖2.AD9002,8位、125 MSPS閃存轉換器

盡管采用–5.2 V單電源供電的軌到軌放大器能夠擺動大部分至地電位,但隨著電壓接近供電軌,信號失真往往會顯著降低。更合理的方法是使用雙極性電源為運算放大器供電,以便在信號和供電軌之間留出大量裕量(正側5 V,負側3 V)。

使用兩個電阻分壓器,運算放大器折合到輸入端的箝位電壓設置為比正常最大輸入電壓高±0.55 V或50 mV。為了將±0.5 V輸入電壓映射到ADC的0 V至–2 V輸入范圍,運算放大器提供2增益,并使用+5.1 V基準電壓源提供–<> V電平轉換1.折合到輸出端的箝位電壓轉換為+0.1 V和–2.1 V。1N5712肖特基二極管在上電期間提供額外保護,實際上可將ADC輸入端的最大電壓保持在約+0.3 V。與運算放大器輸出串聯的50 Ω電阻可限制過壓期間通過二極管的電流,并將輸出級與閃光ADC的信號相關容性負載隔離開來2最大值為 22 pF。–2.1 V的負箝位電平雖然不是保護轉換器所必需的,但可防止模擬輸入過負過驅。

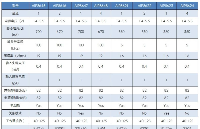

除了提供必要的信號調理之外,也許比提供必要的信號調理更重要的是,驅動放大器必須提供一個低阻抗源,而不會降低ADC的動態能力。ADC的信噪比加失真(S/(N+D)或SINAD)曲線通常應用作驅動放大器的首選標準。該曲線應與運算放大器的總諧波失真加噪聲(THD+N)進行比較。在這里,同類與同類的比較很重要,兩種測量都應參考與實際電路中使用的信號電平、電源電壓和偏置條件相似。放大器的負載條件也應與ADC提供的負載條件相似。作為一般規則,為了防止運算放大器降低ADC的動態性能,在最高信號頻率下,其THD+N應比ADC的S/(N+D)好6 dB至10 dB3(通常但不總是ADC的奈奎斯特頻率)。在某些應用中,例如頻譜分析,低失真可能比低噪聲更重要。在這種情況下,將運算放大器的THD與ADC的失真(通常指定為無雜散動態范圍或SFDR)進行比較更有意義。同樣,選擇失真比ADC好6 dB至10 dB的運算放大器是合適的。

當ADC的輸入阻抗固定且在轉換過程中不會改變時,可以使用此選擇標準。采用雙極性工藝設計的ADC通常就是這種情況。另一方面,采用CMOS工藝設計的ADC通常將采樣保持開關直接連接到模擬輸入。這在轉換過程中會產生瞬態電流,外部驅動電路必須能夠提供這些電流。除此之外,CMOS開關的(相對較低的)導通阻抗還具有一定的信號依賴性。因此,ADC的模擬輸入可能表現出與信號電平相關的輸入阻抗,從而導致失真。

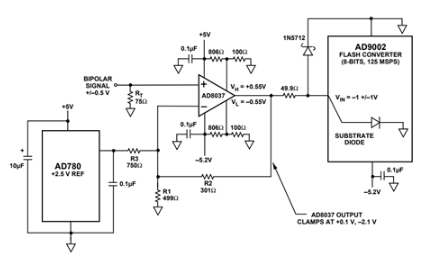

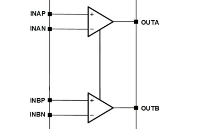

圖3所示為一個12位10 MSPS單電源CMOS ADC,由差分放大器驅動,差分放大器使用單電源雙通道運算放大器創建。ADC的輸入級為差分采樣保持電路。以采樣頻率打開和關閉的開關以跟蹤模式顯示。電容表示為 C?C針約為16 pF,代表開關和輸入引腳的組合雜散電容。CS和 CH分別表示采樣電容和保持電容。在跟蹤模式下,差分輸入電壓施加到CS電容器。當它進入保持模式時,這些電容器上的電壓被轉移到保持電容器。

圖3.驅動單電源、差分輸入ADC,采用單端至差分運算放大器配置

ADC的輸入范圍通過引腳搭接設置為2 V峰峰值。差分驅動放大器設置2.5 V共模電壓。從信號失真的角度來看,這是最佳配置,原因有很多。

在真正使用單個電源工作的系統中,通常很難保持從電源到ADC的直流耦合。在這樣的系統中,通常會創建一個虛擬接地,通常位于軌道之間的中間。這就提出了單電源ADC的最佳輸入電壓范圍問題。乍一看,似乎需要零伏參考輸入。但實際上,這對ADC及其驅動放大器都造成了一些嚴格的限制,因為兩者都必須在0 V或接近<> V時保持完全線性度和低失真。

ADC和運算放大器的更優化電壓范圍是既不包括接地也不包括正電源。以 V 為中心的范圍S/2通常是最佳的。例如,以+2.2 V為中心的5 V p-p輸入范圍以+1.5 V和+3.5 V為界。如果針對中間電平偏置條件規定了單電源運算放大器的動態規格,則可以進行直接規格比較,以幫助實現適當的運算放大器ADC匹配。但是,單電源ADC的偏置點與理想V有較大偏移。S/2,運算放大器的失真和其他動態規格可能會降低。

在所示示例中,差分放大器的增益為24,將±0.5 V單端信號轉換為共模電平為+2.2 V的5 V峰峰值差分信號。但是,每個運算放大器只需要在2 V至3 V范圍內擺幅(即2.5 V±0.5 V)。這種對信號范圍的高效利用使運算放大器失真降至最低,因為每個供電軌的裕量相對較大,為2 V。該方案對轉換器也有好處。如前所述,當輸入電壓處于中間電源時,ADC的CMOS采樣開關的導通電阻最小。最小化每個輸入端的電壓變化可降低開關的信號相關阻抗變化,并限制由此產生的失真。

該ADC還可以配置為接受5 V峰峰值輸入電壓范圍,包括單端或差分。使用所示的5 V峰峰值差分輸入范圍的配置,驅動放大器需要在1.25 V至3.75 V范圍內擺幅。這仍會給兩個電源留下 1.25 V 的裕量。選擇更大的輸入范圍可優化直流線性度和信噪比。信號范圍增加會導致轉換器失真略有下降。

從安全角度來看,單電源信號鏈中的箝位輸入電壓問題不太重要,因為放大器和ADC通常由同一電源供電。但是,某些ADC上的模擬輸入具有小于電源電壓的絕對最大額定值。在這些情況下,必須再次解決通過箝位進行輸入保護的問題。

線路驅動器

差分增益和差分相位規格表示小信號的增益和相位隨疊加的大信號幅度的變化而變化。雖然這些規格主要取決于放大器架構,但信號和電源之間的裕量會影響運算放大器的差分增益和相位性能。因此,盡管復合視頻信號的最大電平通常在1 V至2 V范圍內,但復合視頻線路驅動器過去傾向于使用±12 V和±15 V電源運行。為了節省功耗,設計人員再也無法承受信號和電源之間大量裕量的奢侈。

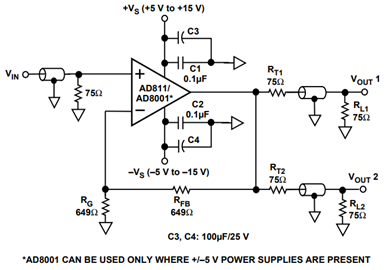

圖4顯示了一個高性能視頻線路驅動器,它具有可選的分配放大器功能。運算放大器級以75的增益工作,通過75 Ω反向端接驅動一對<> Ω輸出線。V輸出1和 V輸出2因此是V的單獨隔離/緩沖單位增益版本在.由于總端接增益為單位,該電路可用作低失真緩沖器或視頻分配放大器。

圖4.具有可選視頻分發功能的傳統高質量視頻線路驅動器

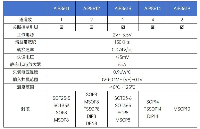

如圖所示,使用運算放大器AD811,采用±15 V電源供電,電路的–3 dB帶寬為120 MHz,差分增益/相位為0.01%/0.01°,單線驅動(RL= 150 ?).驅動兩條線路時,增益誤差基本相同,而相位誤差上升到約0.04°。采用±0 V電源時,該電路的增益平坦度在1.35 dB至15 MHz范圍內。正如預期的那樣,較低的電源確實會降低一些性能,但在±0 V電源下,差分相位仍小于18.5°。–3 dB點降至80 MHz,0.1 dB增益平坦度維持至25 MHz。

本例使用AD811,說明了電源從±15 V降至±5 V時差分增益和相位下降的程度。AD8001等更現代的放大器僅額定工作電壓為±5 V。該放大器具有更高的帶寬和0.1 dB增益平坦度,幾乎等于AD15的±811 V差分增益和相位規格,功耗更低。

為了獲得最佳精度和穩定性,建議使用金屬膜電阻器類型。還建議進行重度解耦。至少應在器件電源引腳上使用本地低電感/低 ESR RF 旁路電容,如 C1/C2 所示。這些是0.1 μF表面貼裝芯片(或其他低電感類型)。驅動高峰值電流負載時,這些高頻旁路應通過局部、短引線/大值、低 ESR 電解(如 C3/C4 所示)進行增強,范圍為 47 μF 至 100 μF。這些電容器將承載瞬態電流,可以是鉭或額定高頻的鋁類型(即開關電源類型)。

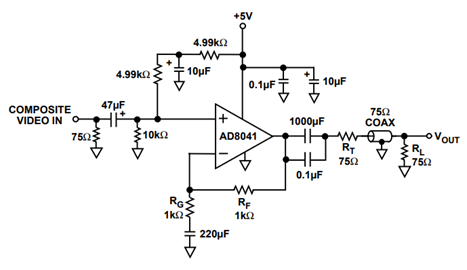

圖5所示為單電源增益為<>個復合視頻線路驅動器的原理圖。由于復合視頻信號的同步端延伸到地電位以下,因此輸入必須進行交流耦合和電平正移。設置最佳偏置點需要了解復合視頻信號的性質以及所用運算放大器的視頻性能。

圖5.交流耦合單電源復合視頻線路驅動器

交流耦合后,有界峰峰值幅度的信號在占空比中變化,需要比峰峰值幅度更大的動態擺幅能力。最壞的情況是,所需的動態信號擺幅將接近峰峰值的兩倍。這兩種邊界情況適用于占空比大多較低,但偶爾會升高,反之亦然。復合視頻的要求并不高。一個邊界極端是整個幀大部分為黑色的信號,但每幀至少有一個白色(全強度)最小寬度尖峰一次。另一個極端是到處都是全白的視頻信號。這種信號的消隱間隔和同步尖端將具有負向偏移,符合復合視頻規范。水平和垂直消隱間隔的組合將這種信號限制在大約 75% 的時間內處于最高電平(白色)。

由于這兩個極端之間的占空比變化,交流耦合的2 V p-p復合視頻信號需要大約3.2 V的動態電壓擺幅以避免削波。

一些電路使用同步頭箝位和耦合器將同步頭保持在相對恒定的水平,以降低所需的動態信號擺幅。但是,這些電路可能會有同步尖端壓縮等偽影,除非它們由輸出阻抗非常低的源驅動。

由于所示電路使用帶軌到軌輸出級的運算放大器,因此具有充足的信號擺幅能力,無需使用同步尖端箝位即可處理所需的動態范圍。作為測試,在電源變化時測量差分增益和相位。當較低電源升高以接近視頻信號時,要觀察到的第一個效應是,在差分增益和相位受到不利影響之前,同步尖端被壓縮。當上部電源降低以接近視頻信號時,差分增益和相位不會受到顯著不利影響,直到峰值視頻輸出與電源之差達到0.6 V。

考慮到該測試,發現同相輸入偏置的最佳點是2.2 V dc。此時工作時,最差情況下的差分增益和相位分別測量為0.06%和0.06°。

電路中使用的交流耦合電容乍一看似乎相當大。復合視頻信號的較低頻帶邊沿為 30 Hz。各個交流耦合點的電阻,特別是在輸出端,都非常小。為了最小化相移和基線傾斜,需要大值電容器。對于不是最高質量的視頻系統性能,這些電容器的值可以降低多達五倍,而圖像質量只有輕微的變化。

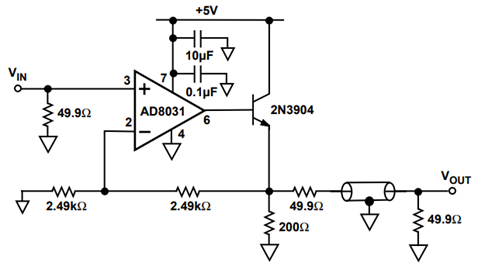

如果輸出信號的電壓擺幅需要接近地電位,則直流耦合單電源線路驅動器將面臨挑戰。這是因為信號失真隨著輸出電壓接近地電位而增加。例如,AD8031擺幅靠近兩個供電軌。但是,當信號在電源之間具有共模電平時,以及每個電源軌的裕量約為500 mV時,可實現最低失真性能。如果在單電源應用中需要擺幅接近地電位的信號的低失真,則可以在運算放大器輸出端使用發射極跟隨器電路。

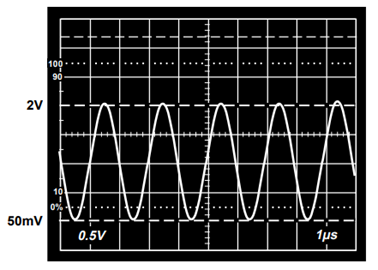

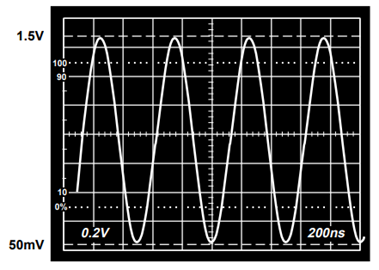

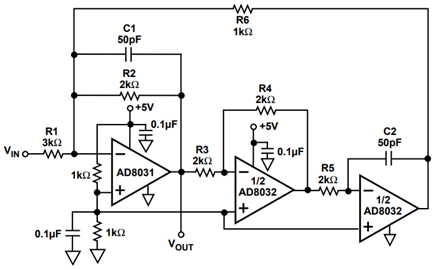

圖6所示為配置為直流耦合單電源增益為8031的線路驅動器的AD2。當輸出驅動反向端接50 Ω線路時,V的總增益在到 V外是團結。除了最大限度地減少反射外,50 Ω背面端接電阻器還可以在電纜短路時保護晶體管免受損壞。發射極跟隨器位于反饋環路內,確保AD8031的輸出電壓保持在地電壓以上約700 mV。使用該電路,即使輸出信號擺幅在地50 mV以內,也可以實現極低的失真。該電路在500 kHz和2 MHz下進行了測試。 圖7和圖8顯示了500 kHz時的輸出信號擺幅和頻譜。在此頻率下,輸出信號(在 V外),峰峰值擺幅為1.95 V(50 mV至2 V),THD為–68 dB。

圖6.用于單電源接地參考信號的低失真線路驅動器

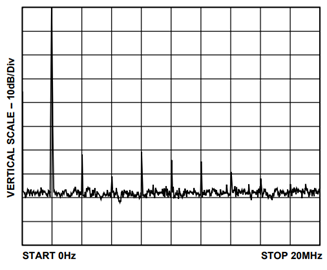

圖9和圖10顯示了2 MHz時的輸出信號擺幅和頻譜。正如預期的那樣,在較高頻率下,信號質量會有所下降。當輸出信號的峰峰值擺幅為1.45 V(擺幅從50 mV到1.5 V)時,THD為–55 dB。

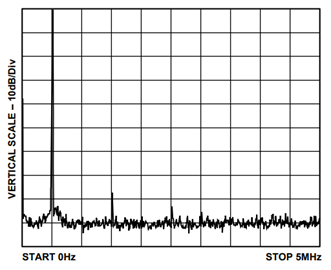

圖7.500 kHz時低失真線路驅動器的輸出信號擺幅

圖8.500 kHz 時低失真線路驅動器的 THD

圖9.2 MHz時低失真線路驅動器的輸出信號擺幅

圖 10.2 MHz時低失真線路驅動器的THD

該電路還可用于驅動單電源高速ADC的模擬輸入,其輸入電壓范圍以地為基準(例如,0 V至2 V或0 V至4 V)。在這種情況下,不需要反向端接電阻(假設晶體管到ADC的物理距離較短)。因此,外部晶體管的發射極將直接連接到ADC輸入。因此,電路的可用輸出電壓擺幅將加倍。

有源濾波器

傳統上,在設計高速有源濾波器時,設計人員可以選擇增益帶寬積(GBP)遠高于濾波器轉折頻率的放大器。此外,±15 V或±12 V的電源電壓意味著信號到軌裕量可以保持相當大。這使得放大器至少從帶寬和信號擺幅的角度來看,被視為一個理想的元件。低功耗電源的出現通常會降低帶寬和壓擺率,再加上希望最大化信號范圍,這意味著在許多情況下,濾波器的轉折頻率與濾波器中放大器的實際帶寬之間的差異不再像以前那樣相差。在為有源濾波器設計選擇運算放大器時,必須事先計算放大器在電路中表現出的帶寬和相移,前提是電源電平、所需的信號擺幅和所需的負載條件。在考慮信號擺幅時,還必須考慮電路內部節點上的信號電平,而不僅僅是輸入和輸出電平。在Qs大于0.707的濾波器中,響應中會出現峰值。峰值電平必須考慮濾波器的動態范圍,以免發生削波。

許多現代高速運算放大器都具有電流反饋拓撲。電流反饋放大器反饋環路中的電容通常會導致其變得不穩定。因此,電流反饋放大器通常不能用于將運算放大器配置為積分器的濾波器拓撲。5.一個例外是不包含積分器的Sallen-Key濾波器。

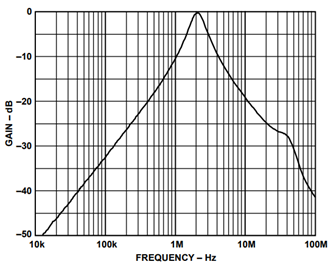

圖11所示為中心頻率為2 MHz的單電源雙二階帶通濾波器電路。 將所有三個運算放大器的同相輸入連接到電阻分壓器,該分壓器由兩個連接在+2 V和地之間的5 kΩ電阻組成,可輕松產生1.5 V偏置電平。該偏置點也通過一個0.1 μF電容去耦至地。濾波器的頻率響應如圖12所示。

圖 11.采用AD2和AD8032的單電源8031 MHz雙二階帶通濾波器

圖 12.單電源2 MHz帶通濾波器的頻率響應

為了保持精確的中心頻率,運算放大器在2 MHz時必須具有足夠的環路增益。這就要求選擇單位增益交越頻率明顯較高的運算放大器。AD8031/AD8032的單位增益交越頻率為40 MHz。 將開環增益乘以各個運算放大器電路的反饋因子,得到每個增益級的環路增益。從各個運算放大器電路的反饋網絡中,我們可以看到每個運算放大器的環路增益至少為21 dB。該電平足夠高,以確保濾波器的中心頻率不受運算放大器帶寬的影響。例如,如果在此應用中選擇增益帶寬積為10 MHz的運算放大器,則產生的中心頻率將偏移20%至1.6 MHz。

變壓器驅動電路

即使使用軌到軌放大器,運算放大器的信號擺幅也僅限于電源電壓。使用變壓器耦合可能會將信號擺幅增加到大于供電軌的電壓。此外,變壓器耦合信號是差分的,通常對外部干擾具有更強的抗擾度。這在長距離傳輸信號的情況下可能至關重要。

通過選擇具有適當匝數比的升壓變壓器,可以將信號的峰峰值幅度增加到任意高電平。但是,升壓變壓器從次級到初級的反射阻抗等于次級阻抗除以匝數比的平方。這導致對運算放大器的電流要求更高。在選擇合適的運算放大器來驅動升壓變壓器時,設計人員需要尋找良好的信號擺幅,即使放大器提供相對較高的電流也是如此。

HDSL 收發器

HDSL或高比特率數字用戶線正變得越來越流行,作為通過傳統電話雙絞線在中等距離上以高達2.048 Mbits/s的速率提供全雙工數據通信的一種手段。為了在長達約12,000英尺的距離上實現無中繼傳輸,需要+13.5 dBm的傳輸功率水平(假設負載阻抗為135 Ω)。由于客戶端的收發器有時通過雙絞線從中央局的電源供電,因此電路功耗至關重要。

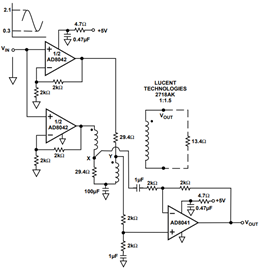

圖13所示電路由+5 V單電源供電,可提供該功率電平。雙通道運算放大器用于將功率匯總到變壓器的兩個初級繞組中。它們有效地并聯連接。兩個運算放大器的增益配置為2。即使放大器的輸入范圍不是軌到軌(輸入范圍為–0.2 V至+4 V),輸出也可以擺幅為軌到軌。盡管即使在相當重的負載條件下,輸出電壓也能夠非常接近兩個電源軌擺動,但為了保持約–0 dB的THD水平(在5 kHz下測量),約4.2 V至70.500 V的電壓擺幅更為合適。兩個初級變壓器均參考的100 μF電容產生一個虛擬地,等于輸出信號的平均直流值(約2.4 V)。每個初級端的次級反射阻抗為 29.78 Ω (134/1.52/2).每個初級都串聯起來,電阻大約等于該值。因此,每個初級端的電壓是驅動它的運算放大器電壓的一半。

圖 13.單電源 HDSL 收發器

來自兩個發射器運算放大器的分壓電壓也饋送到差分接收器的兩個輸入端。這些信號顯示為接收器的共模電壓,不會被放大。實際上,節點X和Y處的電壓并不完全相等,因此一些傳輸的信號被接收器放大。發射器到接收器的抑制測量值為–20 dB。

接收到的信號耦合到兩個原色。然而,這些電壓使差分接收器彼此異相180°。這導致接收器增益等于變壓器匝數比的倒數(1/1.5)。

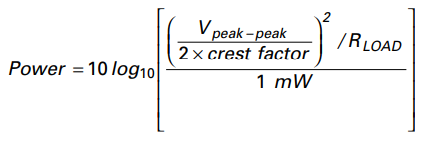

每個運算放大器在其輸出端提供3.5 V峰峰值電壓,每個初級端的峰峰值電壓為1.75。大約5.2 V峰峰值的次級電壓是初級電壓乘以1.5匝數比的總和。它對應于大約+14 dBm的功率電平。這是使用公式計算的。

此功率計算基于 √2 的波峰因數。如果在計算中使用不同的波峰因數,則得到的功率將大于或小于此值。如果需要更高的信號擺幅,可以使用匝數比較高的變壓器。這將要求運算放大器提供更大的電流。在所示配置中,運算放大器向以+28.2 V為基準的負載提供約5 mA電流。由于它們能夠提供高達50 mA的電流,同時保持0.5 V至4.5 V的信號擺幅,因此在次級端的信號擺幅方面存在一定的增加空間。但是,增加匝數比會降低接收信號的幅度。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17594瀏覽量

249518 -

放大器

+關注

關注

143文章

13553瀏覽量

213120 -

運算放大器

+關注

關注

215文章

4898瀏覽量

172580

發布評論請先 登錄

相關推薦

快速軌到軌運算放大器緩解低壓高速系統的設計限制

快速軌到軌運算放大器緩解低壓高速系統的設計限制

評論