交錯(cuò)多個(gè)模數(shù)轉(zhuǎn)換器(ADC)通常是為了提高轉(zhuǎn)換器的有效采樣速率,特別是當(dāng)沒有或只有少數(shù)現(xiàn)成的ADC可以滿足此類應(yīng)用所需的采樣、線性度和交流要求時(shí)。然而,時(shí)間交錯(cuò)數(shù)據(jù)轉(zhuǎn)換器并非易事,因?yàn)榧词故褂猛耆€性的元件,增益/失調(diào)失配和時(shí)序誤差也會(huì)導(dǎo)致輸出頻譜中出現(xiàn)不希望的雜散。以下文章提供了有關(guān)時(shí)間交錯(cuò)模數(shù)轉(zhuǎn)換器的理論方法以及設(shè)計(jì)人員在構(gòu)建時(shí)間交錯(cuò)系統(tǒng)時(shí)通常遇到的障礙類型(以及如何補(bǔ)償這些障礙)的寶貴見解。

當(dāng)今數(shù)據(jù)采集系統(tǒng)的快速變化正在推動(dòng)半導(dǎo)體數(shù)據(jù)轉(zhuǎn)換器制造商提供更高水平的分辨率、時(shí)鐘速度和動(dòng)態(tài)性能。由于這些要求并不總是通過單個(gè)芯片來滿足,因此它們需要系統(tǒng)設(shè)計(jì)人員的創(chuàng)造力。

對(duì)現(xiàn)有的一組高速ADC進(jìn)行時(shí)間交錯(cuò)可以使系統(tǒng)的采樣速度成倍增加,但在更高的采樣速度下,這將成為一件棘手而復(fù)雜的苦差事。以下討論有助于深入了解這種技術(shù),涵蓋此類設(shè)計(jì)的積極和消極方面,并為高速數(shù)據(jù)采集系統(tǒng)中多個(gè)ADC的成功交錯(cuò)提供了有價(jià)值的理論。

什么是時(shí)間交錯(cuò)?

對(duì)于超高速應(yīng)用,時(shí)間交錯(cuò)通過并行操作兩個(gè)或多個(gè)數(shù)據(jù)轉(zhuǎn)換器來提高系統(tǒng)的整體采樣速度。這聽起來合理而直接,但實(shí)際上需要付出更多的努力,而不僅僅是并聯(lián)兩個(gè)ADC。在詳細(xì)討論這種安排之前,請(qǐng)比較時(shí)間交錯(cuò)系統(tǒng)的采樣速率與單個(gè)轉(zhuǎn)換器的采樣速率。根據(jù)經(jīng)驗(yàn),并行操作N個(gè)ADC會(huì)使系統(tǒng)的采樣速率提高約N倍。因此,承載N ADC的交錯(cuò)系統(tǒng)的采樣(時(shí)鐘)頻率1;可以描述如下:

圖1中的簡化框圖顯示了一個(gè)單通道、時(shí)間交錯(cuò)式DAQ系統(tǒng),其中兩個(gè)ADC使系統(tǒng)的采樣速率加倍。這個(gè)比率(fSYSTEM_CLK) 是速率為 f 的兩倍的時(shí)鐘信號(hào)CLK1= fCLK2.因?yàn)?fCLK1相對(duì)于 f 延遲CLK2到 f 的周期SYSTEM_CLK,兩個(gè)ADC交替對(duì)模擬輸入信號(hào)進(jìn)行采樣,產(chǎn)生等于fSYSTEM_CLK.每個(gè)轉(zhuǎn)換器的工作采樣頻率只有采樣頻率的一半。

圖1.該簡化框圖描述了一個(gè)用于高速數(shù)據(jù)采集的兩步、時(shí)間交錯(cuò)式ADC系統(tǒng)。

時(shí)間交錯(cuò)如何工作?

典型的時(shí)間交錯(cuò)系統(tǒng)可以通過分析N位兩步閃存轉(zhuǎn)換器的操作來解釋。時(shí)鐘速度大于幾百兆赫茲的ADC通常具有多步2時(shí)間交錯(cuò)架構(gòu),而不是單步直接轉(zhuǎn)換(純閃存)架構(gòu)(有關(guān)閃存轉(zhuǎn)換的討論,請(qǐng)參閱附錄)。

為了提高比較器已經(jīng)以最大速度運(yùn)行的ADC的采樣速率,必須擴(kuò)展上(粗)和下(細(xì))量化器模塊的數(shù)量。這可以通過實(shí)施一個(gè) N 位粗 ADC 和兩個(gè)時(shí)間交錯(cuò)的 N 位精細(xì) ADC 來實(shí)現(xiàn)(圖 2)。粗量化器 CQ 確定數(shù)字輸出的上位 (MSB),精細(xì)量化器 FQ1 和 FQ2 設(shè)置數(shù)字輸出的下位 (LSB)。

圖2.時(shí)間交錯(cuò)兩步閃光燈轉(zhuǎn)換器的原理。

CQ和FQ1模塊在第一個(gè)采樣步驟中都連接到輸入端子,但當(dāng)時(shí)只有粗量化器采樣和數(shù)字化。在第二步中,F(xiàn)Q1 和 FQ2 使用來自粗量化器的信息來生成參考水平,使它們能夠執(zhí)行精細(xì)量化。LSB在采樣和使用粗量化器執(zhí)行轉(zhuǎn)換期間進(jìn)行數(shù)字化,并在第二次采樣時(shí)發(fā)生交錯(cuò)。

當(dāng)?shù)谝粋€(gè)采樣和轉(zhuǎn)換過程完成后,輸入由CQ和FQ2進(jìn)行采樣和數(shù)字化。FQ2 正在處理第二個(gè)樣本,而 CQ 正在處理第三次采樣。第二個(gè)樣品量化完成后,第三個(gè)樣品由FQ1轉(zhuǎn)換。粗量化器始終進(jìn)行采樣和轉(zhuǎn)換,但精細(xì)量化器(FQ1 和 FQ2)以交替的周期進(jìn)行采樣和數(shù)字化。一遍又一遍地重復(fù),此過程大約使兩步ADC系統(tǒng)的整體采樣速度翻倍。

時(shí)間交錯(cuò)時(shí)應(yīng)考慮什么?

突破交錯(cuò)式ADC的工作極限可能非常有吸引力,但在將該方法轉(zhuǎn)化為成功的實(shí)驗(yàn)之前,必須考慮各種限制和考慮因素。

帶寬限制:

要求更高采樣速度的應(yīng)用通常處理更高頻率的輸入音,因此輸入帶寬為采樣速度一半的數(shù)據(jù)轉(zhuǎn)換器不適合交錯(cuò)。幸運(yùn)的是,大多數(shù)高速數(shù)據(jù)轉(zhuǎn)換器都包括采樣/保持(T/H)放大器,其全功率和小信號(hào)帶寬明顯高于奈奎斯特(f樣本/2)標(biāo)準(zhǔn)。

失調(diào)和增益誤差:

不同ADC中失調(diào)和增益的通道間匹配不會(huì)進(jìn)行修整,因此ADC之間的增益和失調(diào)失配是時(shí)間交錯(cuò)系統(tǒng)中值得關(guān)注的參數(shù)。如果一個(gè)ADC顯示失調(diào),另一個(gè)ADC顯示增益誤差,則數(shù)字化信號(hào)不僅表示原始輸入信號(hào),還表示數(shù)字域中的不需要的錯(cuò)誤。失調(diào)差異會(huì)導(dǎo)致數(shù)字化信號(hào)中的信號(hào)相移,增益失配表現(xiàn)為信號(hào)幅度的差異。因此,對(duì)于交錯(cuò)設(shè)計(jì),應(yīng)選擇具有集成增益和失調(diào)校正功能的ADC,或包括允許校正這些失配的外部電路。

非線性:

積分非線性(INL)被描述為實(shí)際傳遞函數(shù)與直線的偏差,以LSB或滿量程范圍的百分比(%FSR)為單位。對(duì)于單個(gè)ADC,±1LSB的INL誤差很常見,但在交錯(cuò)系統(tǒng)中,這種誤差很容易加倍,導(dǎo)致輸出代碼誤差類似于上述失調(diào)和增益問題。非線性的出現(xiàn)會(huì)給系統(tǒng)帶來失真,從而降低動(dòng)態(tài)參數(shù),如信噪比和失真比(SINAD)和有效位數(shù)(ENOB)。

時(shí)鐘相位抖動(dòng)和噪聲:

用作系統(tǒng)時(shí)鐘的信號(hào)應(yīng)具有盡可能低的相位噪聲。

采用二分頻配置的 D 型觸發(fā)器可降低對(duì)精確 50% 占空比的嚴(yán)格要求。應(yīng)選擇與信號(hào)源的頻率范圍、幅度和壓擺率相稱的時(shí)鐘電路。數(shù)字化信號(hào)的低壓擺率放寬了時(shí)鐘的抖動(dòng)要求。但是,如果此壓擺率較大,則必須將時(shí)鐘抖動(dòng)降至最低。對(duì)于滿量程幅度正弦輸入信號(hào),僅由時(shí)鐘抖動(dòng)引起的最大建議信噪比 (SNR) 為

上述大多數(shù)誤差都可以通過時(shí)域校準(zhǔn)程序、仔細(xì)的電路設(shè)計(jì)和布局、合適的數(shù)據(jù)轉(zhuǎn)換器選擇和數(shù)字后處理來克服。不幸的是,這種方法很復(fù)雜,需要額外的成本、冗長的校準(zhǔn)和數(shù)學(xué)分析。

應(yīng)用

通過評(píng)估和分析實(shí)際電路的性能,我們可以確認(rèn)這里提出的理論方法。例如,圖3所示的測(cè)試設(shè)置基于使用兩塊MAX1444評(píng)估板3來自模擬。MAX1444提供Analog新型40位+10.3V單電源高速數(shù)據(jù)轉(zhuǎn)換器系列中最低速度等級(jí)(3Msps)。由于兩個(gè)現(xiàn)成的測(cè)試板極不可能精確匹配,因此在將信號(hào)源(時(shí)鐘和模擬輸入信號(hào)發(fā)生器)連接到電路板時(shí)要小心:

模擬和時(shí)鐘輸入必須按照評(píng)估套件的規(guī)定進(jìn)行阻抗匹配。

為避免進(jìn)一步不匹配,從信號(hào)源到電路板的電纜長度必須相同。

端接電阻應(yīng)緊密匹配以避免反射。

時(shí)鐘和模擬輸入信號(hào)源發(fā)生器必須鎖相才能正常工作。

圖3.可以設(shè)置測(cè)試兩個(gè)MAX1444評(píng)估板是否適合用于時(shí)間交錯(cuò)系統(tǒng)。

附錄

閃光轉(zhuǎn)換

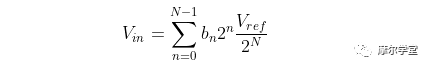

基于直接變頻或閃存架構(gòu)的ADC速度極快,可直接執(zhí)行多位轉(zhuǎn)換。然而,為了管理所需的大量比較器和基準(zhǔn)電壓,需要密集的模擬設(shè)計(jì)。具有N位分辨率的純閃存轉(zhuǎn)換器具有2N-1個(gè)并聯(lián)的比較器。這些比較器的基準(zhǔn)電壓由電阻網(wǎng)絡(luò)設(shè)置,間隔為1LSB = V司 司長/2N分開,其中 V司 司長表示轉(zhuǎn)換器的滿量程輸入范圍及其分辨率。

輸入電壓的變化通常會(huì)在多個(gè)比較器輸出中產(chǎn)生狀態(tài)變化。這些輸出變化組合在一個(gè)編碼器邏輯單元 (2N-1-to-N 編碼器),從轉(zhuǎn)換器產(chǎn)生并行 N 位輸出。盡管閃存轉(zhuǎn)換器是最快的類型,但它們的分辨率4通常受芯片尺寸、輸入電容和大量內(nèi)部高速比較器引入的功耗的限制。此外,閃存轉(zhuǎn)換器的重復(fù)結(jié)構(gòu)要求并聯(lián)比較器部分之間精確匹配,因?yàn)槿魏尾黄ヅ涠伎赡軐?dǎo)致靜態(tài)誤差(例如,輸入失調(diào)電壓增加)。

閃存ADC也容易產(chǎn)生零星和不穩(wěn)定的輸出,稱為“閃光碼”。閃光碼有兩個(gè)主要來源:亞穩(wěn)態(tài)在 2N-1 個(gè)比較器和“溫度計(jì)代碼氣泡”。不匹配的比較器延遲可能會(huì)將邏輯 1 變?yōu)?0(反之亦然),導(dǎo)致在其他正常溫度計(jì)代碼中出現(xiàn)“氣泡”。由于ADC的編碼器單元無法檢測(cè)到此錯(cuò)誤,因此它會(huì)生成一個(gè)亂序代碼,顯示為“閃光”輸出。然而,大多數(shù)新的數(shù)據(jù)轉(zhuǎn)換器設(shè)計(jì)通過支持比較器陣列和帶有附加鎖存器的編碼邏輯來最大限度地減少或完全消除這些問題。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8507瀏覽量

145995 -

adc

+關(guān)注

關(guān)注

97文章

6300瀏覽量

542466 -

比較器

+關(guān)注

關(guān)注

14文章

1614瀏覽量

106836

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于LabVIEW的數(shù)據(jù)采集中德采樣率、每通道的采樣數(shù)和采樣數(shù)據(jù)所用時(shí)間是什么關(guān)系

兩個(gè)通道同時(shí)使用時(shí)DSOX3102A的采樣率會(huì)有交錯(cuò)嗎?

怎樣進(jìn)行音頻采樣率的轉(zhuǎn)換?

用于實(shí)現(xiàn)12.8GSPS采樣率的交錯(cuò)射頻采樣模數(shù)轉(zhuǎn)換器的實(shí)用示例

ADS5485 采樣率200MSPS 16位單通道模數(shù)轉(zhuǎn)換器

AD1896:192 KHz立體聲異步采樣率轉(zhuǎn)換器數(shù)據(jù)表

基于ADSP-2136x SHARC?處理器的EE-268異步采樣率轉(zhuǎn)換器編程

淺談模數(shù)轉(zhuǎn)換器(ADC)的時(shí)間交錯(cuò)

用于實(shí)現(xiàn)12.8GSPS采樣率的交錯(cuò)射頻采樣模數(shù)轉(zhuǎn)換器示例

解密模數(shù)轉(zhuǎn)換器的分辨率和采樣率

什么叫采樣率 數(shù)字信號(hào)處理時(shí)鐘與采樣率的關(guān)系

使用時(shí)間交錯(cuò)數(shù)據(jù)轉(zhuǎn)換器倍增采樣率

使用時(shí)間交錯(cuò)數(shù)據(jù)轉(zhuǎn)換器倍增采樣率

評(píng)論