逐次逼近寄存器(SAR)模數(shù)轉(zhuǎn)換器(ADC)代表了中高分辨率ADC的大部分ADC市場。SAR ADC 提供高達 5Msps 的采樣速率,分辨率為 8 至 18 位。SAR架構(gòu)允許高性能、低功耗ADC采用小尺寸封裝,以滿足當(dāng)今要求苛刻的應(yīng)用。

本文將解釋SAR ADC如何通過使用二進制搜索算法收斂輸入信號來工作。它還解釋了SAR ADC、容性DAC和高速比較器的核心。最后,本文將SAR架構(gòu)與流水線、閃存和Σ-Δ型ADC進行對比。

介紹

逐次逼近寄存器 (SAR) 模數(shù)轉(zhuǎn)換器 (ADC) 通常是采樣速率低于每秒 5 兆采樣 (Msps) 的中高分辨率應(yīng)用的首選架構(gòu)。SAR ADC的分辨率通常為8至16位,具有低功耗和小尺寸。這些特性的組合使這些ADC成為各種應(yīng)用的理想選擇,例如便攜式/電池供電儀器、筆式數(shù)字化儀、工業(yè)控制和數(shù)據(jù)/信號采集。

顧名思義,SAR ADC基本上實現(xiàn)了二進制搜索算法。因此,雖然內(nèi)部電路可能以幾兆赫茲(MHz)運行,但由于逐次逼近算法,ADC采樣速率只是該數(shù)字的一小部分。

SAR ADC 架構(gòu)

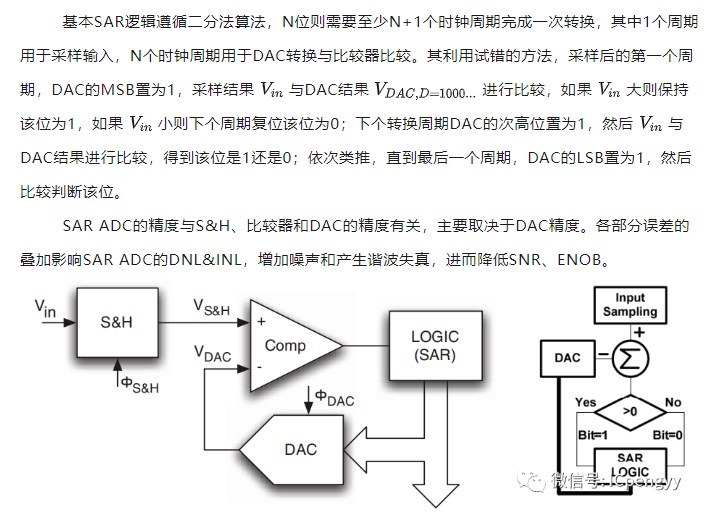

雖然SAR ADC的實現(xiàn)方式多種多樣,但基本架構(gòu)非常簡單(見圖1)。模擬輸入電壓(V在) 保持在軌道/保持上。為了實現(xiàn)二叉搜索算法,首先將N位寄存器設(shè)置為中間電平(即100... .00,其中MSB設(shè)置為1)。這會強制 DAC 輸出 (V代數(shù)轉(zhuǎn)換器) 為 V裁判/2,其中 V裁判是提供給ADC的基準電壓。然后進行比較以確定是否 V在小于或大于 V代數(shù)轉(zhuǎn)換器.如果 V在大于 V代數(shù)轉(zhuǎn)換器,比較器輸出為邏輯高電平或1,N位寄存器的MSB保持在1。相反,如果 V在小于 V代數(shù)轉(zhuǎn)換器,比較器輸出為邏輯低電平,寄存器的MSB清零至邏輯0。然后,SAR 控制邏輯向下移動到下一個位,將該位強制為高電平,并進行另一次比較。序列一直持續(xù)到LSB。完成此操作后,轉(zhuǎn)換完成,寄存器中提供N位數(shù)字字。

圖1.簡化的N位SAR ADC架構(gòu)。

圖 2 顯示了一個 4 位轉(zhuǎn)換示例。y軸(和圖中的粗線)表示DAC輸出電壓。在示例中,第一次比較顯示 V在< V代數(shù)轉(zhuǎn)換器.因此,位 3 設(shè)置為 0。然后,DAC 設(shè)置為 01002并執(zhí)行第二次比較。作為 V在> V代數(shù)轉(zhuǎn)換器,位 2 保持在 1。然后將 DAC 設(shè)置為 01102,然后執(zhí)行第三次比較。位 1 設(shè)置為 0,然后 DAC 設(shè)置為 01012進行最終比較。最后,位 0 保持在 1,因為 V在> V代數(shù)轉(zhuǎn)換器.

圖2.SAR 操作(4 位 ADC 示例)。

請注意,4位ADC需要四個比較周期。一般而言,N位SAR ADC需要N個比較周期,并且在當(dāng)前轉(zhuǎn)換完成之前不會為下一次轉(zhuǎn)換做好準備。這就解釋了為什么這些ADC具有功耗和空間效率,但在14至16位的速度和分辨率組合中很少見于超過每秒幾兆采樣(Msps)的運算。市場上一些最小的ADC基于SAR架構(gòu)。MAX1115/MAX1116和MAX1117/MAX1118 8位ADC及其更高分辨率的MAX1086和MAX1286(分別為10 位和12位)采用尺寸為23mm x 3mm的微型SOT3封裝。12位MAX11102采用3mm x 3mm TDFN封裝或3mm x 5mm μMAX?封裝。

SAR ADC還有另一個顯著特點:功耗與采樣速率成比例。這與閃存或流水線ADC形成鮮明對比,后者通常具有恒定的功耗與采樣速率的關(guān)系。這種縮放功耗在低功耗應(yīng)用或數(shù)據(jù)采集不連續(xù)的應(yīng)用(例如PDA數(shù)字化儀)中特別有用。

深入的SAR分析

SAR ADC的兩個關(guān)鍵元件是比較器和DAC。正如我們稍后將看到的,圖1所示的采樣/保持可以嵌入DAC中,因此可能不是顯式電路。

SAR ADC 的速度受以下因素限制:

DAC的建立時間,必須建立到整個轉(zhuǎn)換器的分辨率范圍內(nèi),例如1/2 LSB

比較器,必須解析V中的微小差異在和 V代數(shù)轉(zhuǎn)換器在指定時間內(nèi)

邏輯開銷

發(fā)援會

DAC的最長建立時間通常由其MSB建立時間決定。這僅僅是因為MSB轉(zhuǎn)換代表了DAC輸出的最大偏移。此外,整個ADC的線性度受DAC線性度的限制。因此,由于固有的元件匹配限制,分辨率超過12位的SAR ADC通常需要某種形式的調(diào)整或校準才能實現(xiàn)必要的線性度。雖然它在某種程度上取決于工藝和設(shè)計,但在實際DAC設(shè)計中,元件匹配將線性度限制在約12位。

許多SAR ADC使用容性DAC,提供固有的采樣/保持功能。容性DAC采用電荷再分配原理來產(chǎn)生模擬輸出電壓。由于這些類型的DAC在SAR ADC中很普遍,因此討論其工作原理是有益的。

容性DAC由具有二進制加權(quán)值的N個電容陣列和一個“虛擬LSB”電容組成。圖3所示為連接到比較器的16位容性DAC示例。在采集階段,陣列的公共端子(所有電容共用連接的端子,見圖3)接地,所有自由端子連接到輸入信號(模擬輸入或V在).采集后,公共端子與地斷開,自由端子與V斷開在,從而有效地捕獲與電容器陣列上的輸入電壓成比例的電荷。然后將所有電容器的自由端子接地,將公共端子負極驅(qū)動至等于-V的電壓在.

圖3.容性DAC的16位示例。

作為二叉搜索算法的第一步,MSB電容器的底板與地斷開并連接到V裁判.這將公共端子沿正方向驅(qū)動等于 1/2V 的量裁判.

因此,VCOMMON = -VIN + ? × VREF

如果VCOMMON<0,則比較器輸出產(chǎn)生邏輯1(即VIN>1/2×VREF)。如果 VIN < VREF 為 1/2 ×,則比較器輸出產(chǎn)生邏輯 0。

如果比較器輸出為邏輯1,則MSB電容的底板保持與VREF連接。否則,MSB電容器的底板將重新接地。

然后將下一個較小電容器的底板連接到VREF,并將新的VCOMMON電壓與地進行比較。

這一直持續(xù)到確定所有位為止。

通常,VCOMMON = -VIN + BN-1 × VREF/2 + BN-2 × VREF/4 + BN-1 × VREF/8 + ... + B0 × VREF/2N-1(B_比較器輸出/ADC輸出位)。。

數(shù)字轉(zhuǎn)換器校準

在理想的DAC中,與數(shù)據(jù)位相關(guān)的每個電容的值恰好是下一個較小電容值的兩倍。在高分辨率ADC(例如16位)中,這會導(dǎo)致值范圍太寬,無法以經(jīng)濟可行的尺寸實現(xiàn)。MAX16等195位SAR ADC使用電容陣列,該電容陣列實際上由兩個容性耦合陣列組成,以降低LSB陣列的有效值。MSB陣列中的電容器經(jīng)過生產(chǎn)調(diào)整以減少誤差。LSB電容的微小變化對16位結(jié)果的誤差微不足道。遺憾的是,僅靠修整并不能產(chǎn)生16位性能,也無法補償由于溫度、電源電壓和其他參數(shù)變化而導(dǎo)致的性能變化。為此,MAX195為MSB陣列中的每個電容提供一個校準DAC。這些DAC電容耦合到主DAC輸出,并根據(jù)其數(shù)字輸入上的值偏移主DAC的輸出。

在校準期間,確定并存儲正確的數(shù)字代碼,以補償每個MSB電容器中的誤差。此后,只要主DAC中的相應(yīng)位為高電平,存儲的代碼就會提供給相應(yīng)的校準DAC。這樣可以補償相關(guān)電容器中的誤差。校準通常由用戶啟動或在上電時自動完成。為了降低噪聲的影響,每個校準實驗都要進行多次(MAX14中約為000,195個時鐘周期),并對結(jié)果進行平均。當(dāng)電源電壓穩(wěn)定時,最好進行校準。每當(dāng)電源電壓、溫度、基準電壓或時鐘特性發(fā)生顯著變化時,都應(yīng)重新校準高分辨率ADC,因為這些參數(shù)會影響直流失調(diào)。如果線性是唯一的問題,則可以容忍這些參數(shù)的更大變化。由于校準數(shù)據(jù)以數(shù)字方式存儲,因此無需頻繁轉(zhuǎn)換以保持準確性。

比較器

比較器的要求是速度和精度。比較器失調(diào)不會影響整體線性度,因為它在整體傳輸特性中顯示為失調(diào)。此外,通常采用失調(diào)消除技術(shù)來減少比較器失調(diào)。然而,噪聲是一個問題,比較器通常設(shè)計為折合到輸入端的噪聲小于1 LSB。此外,比較器需要在整個系統(tǒng)的精度范圍內(nèi)解析電壓。它需要與整個系統(tǒng)一樣準確。

SAR ADC 與其他 ADC 架構(gòu)的比較

與流水線型ADC的比較

流水線ADC采用并聯(lián)結(jié)構(gòu),其中每級同時處理1到幾位(連續(xù)采樣)。這種固有的并行性提高了吞吐量,但代價是功耗和延遲。在這種情況下,延遲定義為ADC采集模擬樣本的時間與輸出端提供數(shù)字數(shù)據(jù)的時間之差。例如,五級流水線ADC將至少有五個時鐘周期的延遲,而SAR只有一個時鐘周期的延遲。請注意,延遲定義僅適用于ADC的吞吐量,不適用于SAR的內(nèi)部時鐘,SAR的運行頻率是吞吐量頻率的許多倍。流水線ADC通常具有數(shù)字糾錯邏輯,以降低每個流水線級中閃存ADC(即比較器)的精度要求。但是,SAR ADC要求比較器與整個系統(tǒng)一樣精確。流水線ADC通常需要比等效SAR大得多的硅面積。與SAR一樣,精度超過12位的流水線ADC通常需要某種形式的調(diào)整或校準。

與閃存 ADC 的比較

閃存ADC由一大組比較器組成,每個比較器由寬帶、低增益前置放大器和一個鎖存器組成。前置放大器必須僅提供增益,但不需要線性或精確。這意味著只有比較器的跳變點必須準確。因此,閃存ADC是目前最快的架構(gòu)。

閃存ADC速度之間的主要權(quán)衡是SAR ADC的功耗顯著降低,外形尺寸更小。雖然存在采樣速率高達8.1Gsps的極快5位閃存ADC(或其折疊/插值變體)(例如MAX104、MAX106和MAX108),但要找到10位閃存ADC要困難得多。此外,12位(及以上)閃存ADC不是商業(yè)上可行的產(chǎn)品。這僅僅是因為閃存ADC中的比較器數(shù)量每增加一位分辨率,就會增加兩倍。同時,每個比較器的精度必須提高一倍。然而,在SAR ADC中,更高的分辨率需要更精確的元件,但復(fù)雜性不會呈指數(shù)級增長。當(dāng)然,SAR ADC無法達到閃存ADC的速度。

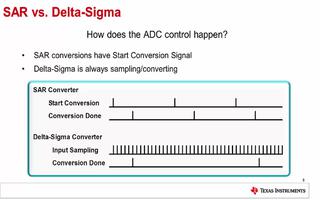

與Σ-Δ轉(zhuǎn)換器的比較

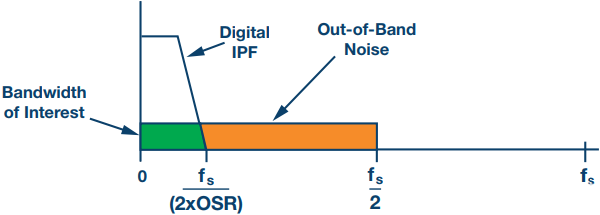

數(shù)字音頻應(yīng)用中使用的傳統(tǒng)過采樣/Σ-Δ轉(zhuǎn)換器的帶寬有限,約為22kHz。最近,一些高帶寬Σ-Δ轉(zhuǎn)換器的帶寬達到1MHz至2MHz,分辨率為12至16位。這些通常是非常高階Σ-Δ調(diào)制器(例如,四階或更高),集成了多位ADC和多位反饋DAC。與SAR ADC相比,Σ-Δ轉(zhuǎn)換器具有先天優(yōu)勢:它們不需要特殊的調(diào)整或校準,甚至不需要達到4至16位的分辨率。由于它們的采樣速率遠高于有效帶寬,因此它們也不需要在模擬輸入端具有陡峭滾降的抗混疊濾波器。后端數(shù)字濾波器負責(zé)處理此問題。Σ-Δ轉(zhuǎn)換器的過采樣特性也傾向于“平均”模擬輸入端的任何系統(tǒng)噪聲。

Σ-Δ轉(zhuǎn)換器以速度換取分辨率。為了產(chǎn)生一個最終采樣,需要多次采樣(至少16次,通常更多次),這就決定了Σ-Δ調(diào)制器中的內(nèi)部模擬元件的運行速度要比最終數(shù)據(jù)速率快得多。數(shù)字抽取濾波器的設(shè)計也是一個挑戰(zhàn),并且消耗相當(dāng)大的硅面積。最快的高分辨率Σ-Δ轉(zhuǎn)換器預(yù)計在不久的將來不會具有明顯高于幾MHz的帶寬。

結(jié)論

總之,SAR ADC的主要優(yōu)點是低功耗、高分辨率和高精度以及小尺寸。由于這些優(yōu)點,SAR ADC通常可以與其他更大的功能集成。SAR架構(gòu)的主要限制是較低的采樣速率,以及要求構(gòu)建模塊(DAC和比較器)與整個系統(tǒng)一樣精確。

審核編輯:郭婷

發(fā)布評論請先 登錄

相關(guān)推薦

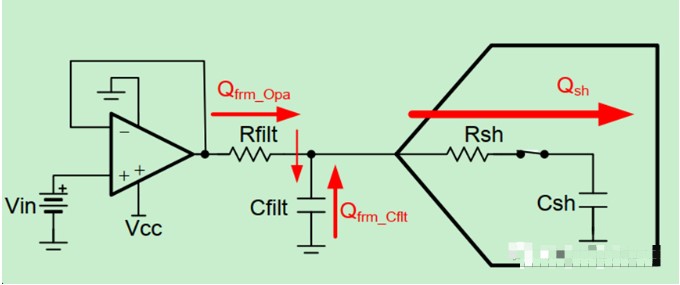

SAR型ADC的驅(qū)動電路設(shè)計

AD數(shù)據(jù)轉(zhuǎn)換-SAR ADC介紹

SAR與ADC不同輸入類型

SAR ADC輸入類型間的性能比較-第一部分

不同的SAR ADC模擬輸入架構(gòu)研究

SAR ADC模擬輸入架構(gòu)

探索不同的SAR ADC 模擬輸入架構(gòu)

SAR ADC之間的性能比較和輸入注意事項

SAR ADC的原理以及SAR ADC驅(qū)動電路設(shè)計要點

使用過采樣增加SAR ADC的動態(tài)范圍

SAR ADC是什么 SAR ADC應(yīng)用優(yōu)勢

簡單的ADC比較矩陣

了解SAR ADC:其架構(gòu)及其與其他ADC的比較

了解SAR ADC:其架構(gòu)及其與其他ADC的比較

評論