在設計中使用超快速數據轉換器的高速應用通常需要非常干凈的時鐘信號,以確保外部時鐘源不會對系統的整體動態性能產生不需要的噪聲。因此,選擇合適的系統組件至關重要,這有助于產生低相位抖動時鐘。以下應用筆記可作為選擇合適的元件的寶貴指南,以設計適用于超快速數據轉換器的基于PLL的低相位噪聲時鐘發生器。

介紹

許多現代、高速、高性能集成電路,如MAX104和MAX106模數轉換器(ADC),都需要工作在GHz范圍內的低相位噪聲(低抖動)時鐘。傳統的晶體振蕩器可以提供低抖動時鐘信號,但通常不能在120MHz以上的振蕩頻率中使用。

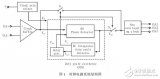

圖1顯示了典型高速數據轉換器系統的簡化框圖。該系統由帶通濾波器、ADC、高頻時鐘、高速存儲設備和后處理單元組成。除MAX104外,高頻時鐘在決定高速數據轉換器的精度方面起著重要作用。這種高頻、低相位噪聲時鐘是高頻壓控振蕩器(U1)、鎖相環(U2)和晶體振蕩器(U3)的組合,如圖2所示。

圖1.典型的高速數據轉換器系統,采用MAX104 ADC和基于PLL的低抖動時鐘。

圖2.高速、低相位噪聲時鐘是確保高速ADC最佳動態性能的最關鍵元件之一。

MAX2620壓控振蕩器(VCO)能夠產生高達1GHz的振蕩器頻率,同時提供足夠的噪聲性能。由于固有的頻率漂移,通常需要鎖相環(PLL)通過將VCO輸出與晶體振蕩器頻率進行比較,將VCO輸出鎖定到所需頻率。

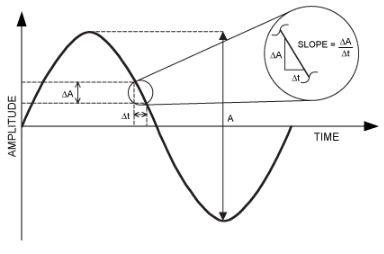

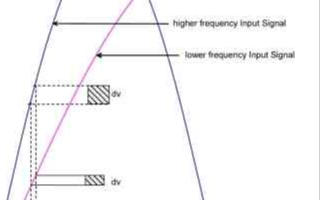

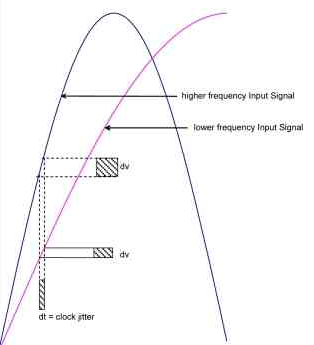

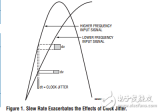

為高速數據轉換器系統選擇合適的VCO并不像找到具有正確振蕩器頻率的VCO那么簡單。必須考慮的一個關鍵參數是時鐘抖動。抖動通常定義為數字信號的重要時刻從其理想時間位置的短期、非累積變化。圖3顯示了包含抖動的采樣時鐘信號。時鐘產生的抖動是由各種內部噪聲源引起的,例如熱噪聲、相位噪聲和雜散噪聲。對于數據轉換器,抖動會影響數據轉換器的信噪比(SNR)性能。

圖3.時鐘信號抖動會降低ADC信噪比。

時鐘抖動如何降低ADC的信噪比(SNR)

時鐘源產生的抖動可能導致ADC的內部電路錯誤觸發采樣時間。如圖4所示,采樣時間Δt的不確定性等同于幅度ΔA的不確定性。這會導致模擬輸入幅度的錯誤采樣,從而降低ADC的SNR。通過以下等式,可以計算出給定時鐘抖動量的數據轉換器的最大SNR:

圖4.使用采樣時間不確定性獲得的信噪比模型。

當項 cos(ωt) = 1 時,斜率達到最大值。因此,EQ.2可以重新排列為:根據定義,A/(ΔA)是信噪比,Δt是抖動的均方根(RMS)值。等式3可以改寫為: 例如,如果模擬輸入信號為250MHz,并且要達到50dB SNR,則最大RMS抖動(σ

例如,如果模擬輸入信號為250MHz,并且要達到50dB SNR,則最大RMS抖動(σRMS)必須小于2ps。

噪聲源如何引起抖動

熱噪聲、調頻 (FM)、幅度調制 (AM)、相位調制 (PM) 和雜散分量都會產生導致時鐘信號抖動的噪聲。由于難以區分由FM、AM和PM引起的噪聲,因此所有三種類型的噪聲都歸為一個通用術語,稱為相位噪聲。為了明確相位噪聲的計算,本文以使用MAX2620 VCO和PLL的高頻電路為例。

熱噪聲對抖動的貢獻

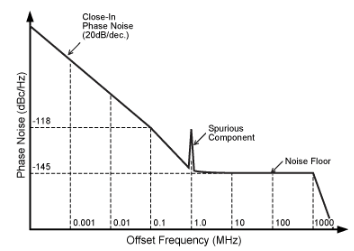

圖5顯示了VCO相位噪聲曲線的簡化圖。MAX2620的輸出放大器具有大約-147dBm/Hz的熱本底噪聲。這種噪聲是帶寬有限的白色高斯噪聲。雖然有效帶寬尚未表征,但可以近似為工作頻率的兩倍。將MAX2620正確調諧至所需輸出頻率后,本底噪聲對抖動的貢獻可通過下式計算:

圖5.簡化MAX2620 VCO的相位噪聲曲線與失調頻率的關系

= 邊沿到邊抖動方差(以 s2 為單位)

ωo = 2πfo = 角時鐘振蕩(中心)頻率(以 rad/s 為單位)

fo = 振蕩器(中心)頻率(赫茲)

f = 偏離中心頻率的頻率(以 Hz 為單位)

τ = 1/2fo = 周期的一半(以 s 為單位)

L(f) = 偏移頻率 f 時的相位噪聲(單位為 dBc/Hz)。

為了進一步改善噪聲性能,通常在VCO輸出端應用頻率響應類似于帶通濾波器的功率匹配網絡(L2和C6)。這會衰減目標帶寬之外的不需要的噪聲。通過這樣做,可以通過從0Hz偏移到f的積分極限來估計最差的噪聲0.超出這些限值的噪聲會大大衰減,可以忽略不計。因為本底噪聲對于 0Hz 到 f 的偏移頻率是均勻的0,L(f) 可以被認為是常數。等式5可以簡化為:

本底噪聲引起的邊沿到邊序抖動為:由于熱噪聲不相關,因此抖動不累積。周期間抖動與邊沿到邊抖動相同。

等式8也可以顯示為:

其中信噪比OSC是本底噪聲引起的振蕩器的信噪比。

相位噪聲對抖動的貢獻

相位噪聲的特征是失調頻率下的噪聲功率與時鐘(載波)信號的功率電平之比。該比率通常歸一化為 1Hz 帶寬,從而產生 dBc/Hz 單位。例如,圖100中5kHz失調時的相位噪聲為-118dBc。這意味著1000.1MHz的噪聲功率比118Hz帶寬中1000MHz的載波功率水平低1dB。

MAX2620的自由運行相位噪聲從20MHz轉折失調頻率到時鐘頻率約為1dB/十倍頻程。使用EQ. 11時,相位噪聲引起的周期間抖動可以計算如下:

其中f是時鐘頻率的失調頻率,它必須位于相位噪聲每十倍頻程降低20dB的區域。相位噪聲L(f)取自MAX2620在f = 100kHz失調頻率下的特性。當f = 10kHz時,產生的抖動不會改變。

雜散元件對抖動的貢獻

基于 PLL 的時鐘信號會產生雜散。如果不抑制這些雜散,它們可能會降低抖動性能。圖6顯示了使用頻譜分析儀采集的1GHz時鐘信號的頻譜圖。圖中所示的兩對對稱雜散分別比載波低約75dBc和85dBc。這些雜散與載波以及彼此之間的分離由鎖相環中使用的比較頻率決定。在這種情況下,比較頻率為1MHz;因此,載波旁邊的兩個雜散距離載波和后續對正好1MHz。此外,還有另一對由晶體振蕩器引起的75MHz偏移的-20dBc雜散(未顯示)。以下等式將這些雜散轉換為抖動:

圖6.顯示帶有雜散元件的1GHz時鐘。

其中 fm是相位噪聲雜散分量出現的失調頻率。m = 1 時,周期間抖動計算為 4.38x10-6對于使用ADC的實際應用,例如MAX104,該電平的雜散噪聲引起的抖動可以忽略不計。

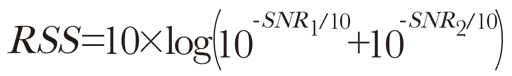

總抖動

總周期間抖動是抖動平方和的平方根的函數,可以按如下方式計算:

鎖相環

由于溫度、電源、負載等原因引起的頻率漂移,自由運行的VCO很少單獨使用。通常引入鎖相環以幫助將VCO輸出鎖定到所需頻率。如果設計得當,鎖相環有助于降低相位噪聲。環路帶寬內的相位噪聲低于自由運行的VCO的相位噪聲。因此,相位噪聲引起的實際抖動小于EQ.11。

圖7顯示了MB15E07在整數N分頻PLL系統中的功能圖。它由一個鑒相器(或比較器)、一個輸出電荷泵、一個雙模量預標量、一個N計數器和一個R計數器組成。N 計數器由一個主 (M) 計數器和一個燕子或輔助 (A) 計數器組成。

然后,N 計數器與雙模預標量 (P) 配合使用。

圖7.典型PLL系統的簡化框圖,由PLL、晶體振蕩器、環路濾波器和VCO組成。

在上電期間(假設PLL已預編程),VCO將以所需頻率加上一些偏移振蕩。該頻率首先除以整數N,然后與參考晶體振蕩器頻率進行比較,其頻率也除以整數R。如果兩個頻率之間存在相位差,則PLL輸出端的電壓會相應變化。例如,如果VCO頻率低于基準頻率,則電荷泵將對環路濾波電容充電以增加電壓。如果VCO頻率高于基準,電荷泵將對環路濾波電容放電以降低電壓。電壓的增加導致頻率的增加,反之亦然。因此,PLL用作反饋環路,將VCO輸出頻率鎖定在所需頻率。VCO 頻率是 N、R 和 f 的函數裁判計算方法如下:

例如,如果 P = 32、M = 31 和 A = 8,則使用 EQ. 14,N 計數器計算為 1000。如果參考振蕩器頻率為20MHz,R計數器設置為20,則使用EQ.15,則VCO頻率鎖定在1000MHz。

設計參數

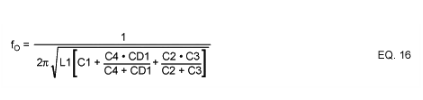

需要仔細設計和實現時鐘電路,以確保最佳性能。這可以通過選擇合適的組件和提供精心設計的高頻 PC 板來實現。表1顯示了兩種不同工作頻率的推薦元件值。這些值可確保VCO以所需頻率振蕩和鎖相,同時提供適當的輸出功率電平。MAX2620的輸出頻率由外部諧振電路設置,諧振電路由L1、C1、C2、C3、C4和D1組成。L1、C1、C2、C3 和 C4 設置自由運行的振蕩頻率。變容二極管D1將輸出頻率微調至所需頻率。D1 采用反向偏置,電容隨 PLL 輸出產生的偏置電壓而變化。D1電容的變化允許對輸出頻率進行微調。

振蕩頻率可以用以下公式計算:

為了適應元件容差、PCB、電源電壓和溫度變化,應選擇D1的電容,使調諧范圍約為標稱頻率的±5%至±10%。C4是將變容二極管耦合到調諧池的電容器。增加 C4 可以增加調諧范圍。C2 和 C3 是振蕩器正常工作所必需的反饋電容。通常,C2 = 2.7pF和C3 = 1.0pF。對于 1.0GHz,選擇 L1 = 5.6nH、C4 = 4.7pF 和 C1 = 1.0pF。 VCO輸出和ADC時鐘輸入必須匹配至50Ω。VCO輸出端使用LC網絡(L2和C6),以確保向ADC時鐘輸入端提供最佳功率傳輸。匹配網絡具有類似帶通濾波器的頻率響應,可進一步降低本底熱噪聲。

表 1.時鐘發生器的建議組件值

| 指定 | 描述 | ||||

| f外= 600兆赫 | f外= 1000兆赫 | ||||

| R1 | 240Ω | 390Ω | |||

| R2 | 240Ω | 390Ω | |||

| C1 | 1.0pF | 1.0pF | |||

| C2 | 2.7pF | 2.7pF | |||

| C3 | 1.0pF | 1.0pF | |||

| C4 | 9.0pF | 3.3pF | |||

| C5 | 9.0pF | 2.2pF | |||

| C6 | 3.0pF | 1.5pF | |||

| C7 | 12nF | 3.9pF | |||

| C8 | 120nF | 39nF | |||

| C9 | 12nF | 3.9nF | |||

| L1 | 12nH (±2%) | 5.6nH (±2%) | |||

| L2 | 18nH | 10nH | |||

| D1 | SMV1233-001 (Alpha Industries) | SMV1233-001 (Alpha Industries) | |||

PLL脈沖的電荷泵輸出,相位比較頻率由R和外部晶體振蕩器確定。采用環路濾波器將這些脈沖濾波為VCO的恒定直流控制電壓。三階環路濾波器(圖2)由C7、C8、C9、R1和R2組成。使用簡化的公式 17 到 23 計算組件值。 N = 等式的計數器值 14

N = 等式 14 中的計數器值

ξ = 阻尼系數,通常為 0.707

ICP= 電荷泵電流,MB15E07為10mA

KVCO= VCO調諧增益或靈敏度

VCO 調諧增益,KVCO,取決于 VCO 油箱中使用的元件值。本設計示例中的VCO調諧增益約為35MHz/V。

MB15E07通過SPI?兼容接口進行編程。表2給出了600MHz (MAX106)和1000MHz (MAX104)工作的寄存器/計數器設置:

表 2.建議注冊 帶15MHz晶體振蕩器的MB07E20的設置

| 600MHz | 1000MHz | ||||

| fCOMPARISON | 500kHz | 1000kHz | |||

| Loop Bandwidth | 25kHz | 50kHz | |||

| R Counter | 40 | 20 | |||

| P Counter | 32 | 32 | |||

| M Counter | 37 | 31 | |||

| A Counter | 16 | 8 | |||

| SW bit | HIGH | HIGH | |||

| FC bit | HIGH | HIGH | |||

為確保良好的高頻 PC 板布局,請記住以下建議:

保持所有印刷電路板走線長度盡可能短。采用受控阻抗走線設計。

盡可能選擇最小的元件尺寸,最好是0603或0402型。

使用高質量因數 (Q) 元件將 VCO 相位噪聲降至最低,并最大限度地提高輸出功率傳輸。Q 因子為 40 或更高就足夠了。

諧振電路的所有元件盡可能靠近MAX2620。

將去耦電容放置在VCO附近,并直接連接到接地層。全部 V抄送連接應有自己的去耦電容。

在VCO輸出和ADC時鐘輸入之間保持50Ω連接。

使用表 1 中的組件值建議作為起點。可能的寄生效應可能需要對某些組件值進行微調,以確保最佳性能。

實驗結果

為了演示所建議的時鐘電路的性能,根據建議的公式和技術設計,圖2中的電路使用MAX104評估板進行設計和測試。圖6顯示了使用頻譜分析儀測量的擬議高頻、低抖動時鐘的輸出。振蕩頻率鎖相在1GHz,輸出電平為-2dBm。圖8所示為MAX104 ADC在模擬輸入頻率范圍內的信噪比。用 f樣本= 1.0GHz 和 f在在-1dBFS下,對于47MHz至1GHz的模擬頻率,SNR分別為45.5dB至10.1dB。與已知的低抖動信號發生器(HP8662A)相比,使用建議的時鐘測得的SNR僅低~0.4dB。

圖8.采用PLL時鐘時MAX104的SNR比采用HP0A時低約4.8662dB。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8628瀏覽量

146876 -

pll

+關注

關注

6文章

775瀏覽量

135052 -

數據轉換器

+關注

關注

1文章

358瀏覽量

27986

發布評論請先 登錄

相關推薦

為高速A/D轉換器設計時鐘

用于高速AD的低抖動時鐘穩定電路

模數轉換器的性能及時鐘抖動對其造成的影響分析

高速模數轉換器的性能分析及時鐘抖動會對其造成什么影響

AN-1221: 使用ADF4002 PLL產生高速模數轉換器所需的極低抖動編碼(采樣)時鐘

為高速數據轉換器設計低抖動時鐘

為高速數據轉換器設計低抖動時鐘

評論