以下文章介紹了小信號和大信號輸入與數據轉換器的噪聲+失真性能之間的關系及其對數字接收器系統靈敏度和交流性能的影響。

介紹

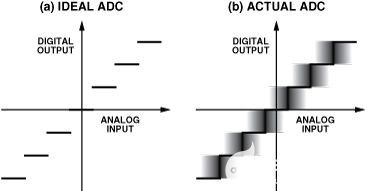

在采樣或子采樣接收器設計中使用高性能奈奎斯特模數轉換器(ADC)時,RF設計人員需要了解ADC在小信號和大信號輸入下的噪聲性能。接收器必須滿足這兩個信號電平極端下的靈敏度和阻塞(高電平干擾)要求,ADC針對每個電平產生不同的噪聲量,可以用其有效噪聲系數來表示。在確定ADC的交流要求時,用戶必須了解接收器陣容中ADC噪聲貢獻的量。對于下面的討論,假設噪聲在轉換器的奈奎斯特頻帶上是平坦的。

確定有效噪聲系數

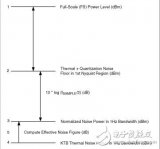

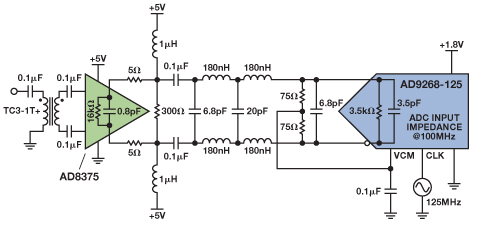

對于小模擬輸入信號(大約-35dBFS),熱+量化噪聲功率主導ADC本底噪聲,用于近似ADC的有效噪聲系數(NF)。一旦知道ADC的噪聲系數,就可以使用級聯噪聲系數方程1來確定接收器輸入端的總接收器噪聲系數。小信號輸入的ADC噪聲貢獻水平用于接近和略高于接收器靈敏度的信號。請參考圖1,并按照以下步驟估算小信號模擬輸入電平的ADC有效噪聲系數:

計算ADC的滿量程電平(單位:dBm)。此步驟是必要的,因為熱+量化噪聲功率通常以dBFS為單位給出,噪聲系數是相對于dBm計算的。

根據元件供應商的數據手冊或通過測量(對于-35dBFS量級的小信號輸入電平)確定熱+量化本底噪聲電平(以dBm為單位)。

通過減去 1 × 對數 (f ) 計算 10Hz 帶寬中的歸一化本底噪聲電平樣本/2) 其中 f樣本以赫茲為單位。

確定1Hz帶寬內的熱噪聲功率;

KTB = 4.002 × 10-21瓦特(或對數形式 = -174dBm),其中

K = 玻爾茲曼常數 = 1.381 × 10-23室溫

下 W/Hz/K,

T = 290 K B = 1Hz 的歸一化帶寬

通過從步驟 4 中計算的結果中減去步驟 3 的結果來計算有效噪聲系數。

在實踐中,一旦知道ADC的有效噪聲系數,并確定模擬電路(RF和IF)的級聯噪聲系數;選擇ADC之前的最小功率增益,以滿足所需的接收器噪聲系數。功率增益量對最大阻塞信號或接收器可以容忍的最高干擾水平設置了上限。對于蜂窩基站應用,如果不實施一定量的自動增益控制(AGC),ADC通常沒有足夠的動態范圍來滿足噪聲系數要求(接收器靈敏度)和最大阻塞器要求。AGC 可以包含在 RF 或 IF 級(或兩者)中。當使用更高分辨率的轉換器時,熱+量化噪聲較低,從而降低了ADC的有效噪聲系數。因此,接收器陣容中需要較少的增益來實現接收器噪聲系數,從而在存在更高電平阻塞信號時減少對AGC電路的需求。

圖1.確定ADC對小信號輸入的有效噪聲系數,以滿足接收器靈敏度要求。

對于中間信號電平輸入,轉換器的差分非線性(DNL)噪聲隨著跨越主要子范圍邊界而增加。中間信號電平可以定義為大于-35dBFS的信號電平,但仍低于時鐘抖動顯著增加ADC噪聲功率的輸入電平。中間信號電平不是本應用筆記的重點,因為它們介于靈敏度和阻塞信號電平極端之間。

對于大電平模擬輸入信號(接近滿量程),ADC本底噪聲電平增加,主要是由于時鐘抖動。信號與噪聲電平的比值定義為信噪比(SNR)。在任何特定應用中,ADC噪聲功率的可接受水平是在同時向接收器端子施加阻塞信號和較小信號的情況下計算的。在任何應用中,SNR都可以針對任何帶寬指定,但通常以第一奈奎斯特區(采樣速率的一半)或所需的信號帶寬指定。因此,用戶密切關注整個計算過程中使用的帶寬非常重要。

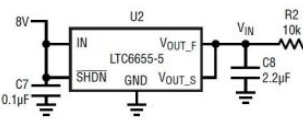

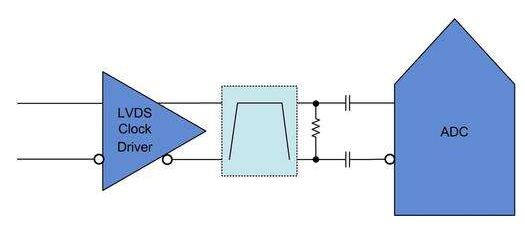

請參考圖2,并按照以下步驟估算ADC在大模擬輸入信號下的有效噪聲系數:

確定轉換器的滿量程電平(以dBm為單位),知道最大允許V值P-P和輸入端接電阻,R在.

注意制造商數據手冊中指定或用戶測量的SNR水平(在圖2中顯示為X dB)。

在已知SNR的情況下,計算轉換器在第一奈奎斯特區域的噪聲功率(以dBm為單位)。

使用采樣率計算 10 × 日志 (f樣本/2) 其中 f樣本以赫茲為單位。

通過從(1)中的結果中減去(4)中得到的結果來確定轉換器在3Hz帶寬內的噪聲功率。

計算 B = 1Hz 的 KTB(在室溫下等于 -174dBm)。

通過從(6)中獲得的結果中減去(5)的結果來計算有效噪聲系數。

圖2.確定大信號輸入的ADC有效噪聲系數,以滿足接收器阻塞器要求。

使用MAX1428的數值示例

MAX1428具有以下初步規格(見表1):

| 參數 | 條件 | 象征 | 典型值 | 單位 |

| 分辨率 | N | 15 | 位 | |

| 模擬輸入范圍 | 維德 | 2.56 | 副總裁-p | |

| 差分輸入電阻 | 凜 | 1000 | 歐姆 | |

| 模擬帶寬,全功率 | BW1 | 260 | 兆赫 | |

| 交流規格 | 樣本= 80毫秒 | |||

| 熱+量化本底噪聲 | 模擬輸入 < -35dBFS | NF | -78.3 | dBFS |

| 信噪比 |

模擬輸入為 -2dBFS, IN= 70MHz |

信 噪 比 | 73.7 | 分貝 |

| 信噪比和失真比 |

模擬輸入為 -2dBFS, IN= 70MHz |

西納德 |

72.5 | 分貝 |

MAX1428 ADC噪聲貢獻

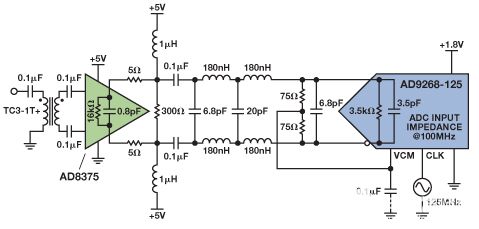

假設MAX1428差分輸入引腳上的端接電阻產生200Ω的總差分電阻。滿量程輸入電平計算得出約為等于+6 dBm (2.5VP-P跨200Ω)。對于80Msps的時鐘速率,第一奈奎斯特區域的熱+量化本底噪聲功率等于-78.3dBFS或-72.3dBm。當70MHz模擬輸入電平增加到-35dBFS以上,但不接近滿量程時,轉換器DNL噪聲會使轉換器總本底噪聲增加1.3dB至-71dBm。隨著輸入電平進一步增加并接近滿量程,由于ADC時鐘抖動至-1.3dBm值,本底噪聲額外增加69.7dB,從而產生28.3dB的有效噪聲系數(根據圖2中概述的程序)。

圖3.MAX1428 ADC噪聲貢獻圖示于第一奈奎斯特區。

接收器靈敏度的阻塞器不存在情況

假設ADC前面的所有模擬電路的級聯噪聲系數均為3.5dB。假設目標是使ADC將接收器總噪聲系數降低不超過0.2dB,以滿足CDMA基站接收器中的某些目標靈敏度。該噪聲系數值應為空口要求提供足夠的裕量,這也取決于最終探測器的Eb/No(位能量與噪聲功率譜密度比)要求。如果使用表1428中的MAX1熱+量化本底噪聲值,當器件時鐘為25Msps時,可以計算出7.1dB的等效噪聲系數(按照圖80所示的程序)。由于實現了處理增益,1.23MHz CDMA通道帶寬中的ADC噪聲比第一奈奎斯特區域中的噪聲低15.1dB。除非另有說明,否則圖4中的所有噪聲功率均以通道帶寬計算。計算總增益為35dB,以實現所需的3.7dB典型噪聲系數值。

圖4.阻止程序不存在的情況。

阻止程序當前方案

當增益領先于ADC35dB時,天線端子上高于-29dBm的最大單音阻塞電平將超過ADC滿量程輸入。cdma2000?蜂窩基站標準規定天線端子上允許的最大阻塞電平為-30dBm。在任何實際應用中,當考慮接收器增益容差時,設計中都需要包括達到此最大阻塞電平的裕量。在本例中,6dB增益降低用于增加施加到ADC的最大允許阻塞信號。這種增益降低量導致天線的最大阻塞電平為-25dBm,ADC輸入端的最大阻塞電平為+4dBm(-2dBFS)。當存在單音阻塞器時,cdma2000空中接口標準允許整體(噪聲+失真)相對于參考靈敏度下降3dB。(噪聲+失真)元件的分配由設計人員決定,用于任何特定的接收器配置。例如,假設當施加0dB的AGC時,設計人員允許RF前端級聯噪聲系數從標稱5.3dB降低5.6dB。ADC前面只有29dB的增益和28.3dB的有效噪聲系數,在“阻塞條件”下,級聯接收器噪聲系數為5.3dB,與根據接收器靈敏度計算的1.6dB噪聲系數相比下降了3.7dB。這比cdma1標準中允許的4dB降級(噪聲+失真)低3.2000dB。

圖5.阻止程序當前方案。

模數轉換器噪聲和失真 (SINAD)

如果使用ADC的SINAD值72.5dB而不是SNR(考慮到ADC的噪聲和失真成分),則由于RF前端噪聲系數和ADC(噪聲+失真)引起的噪聲系數總體下降將為2.1dB,仍低于為該測量分配的3dB。因此,如果需要,仍會為接收器模擬前端的(噪聲+失真)性能分配0.9dB降級。

結論

本應用筆記說明,ADC根據信號輸入電平產生不同水平的噪聲功率,并且ADC噪聲會影響小信號和大信號電平極端情況下的整體接收器響應。如果在接收器設計中未正確考慮ADC噪聲(和失真)功率的級聯貢獻,則轉換器可能超出或低于任何特定應用的規定。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8509瀏覽量

146011 -

接收器

+關注

關注

14文章

2441瀏覽量

71539 -

adc

+關注

關注

97文章

6302瀏覽量

542488

發布評論請先 登錄

相關推薦

ADC如何在存在大信號情況下同時處理小信號?

了解ADC噪聲用于接收機的小和大信號輸入

了解接收器應用中小信號輸入和大信號輸入的ADC噪聲

了解接收器應用中小信號輸入和大信號輸入的ADC噪聲

評論