在過去幾十年里,微控制器的內部外設發(fā)生了巨大的變化。最初許多微控制器只包含RAM、ROM,也許還有基本的定時器。隨著微控制器的發(fā)展,更多的外設被基礎到這種單價不超過一美元的器件中。定時器/計數(shù)器、PWM和包括UART、SPI和I2C在內的標準串行接口常用于這些廉價的微控制器。另一個重大變化是32位CPU正在取代同一價格范圍的8位器件。

但是即便有如此豐富的特性,對于廉價微控制器而言,隨時都存在微控制器廠商不能迅速支持的項目專用硬件接口或新的第三方接口。往往這要求設計人員使用外部硬件或是通過位拆裂在固件中實現(xiàn)接口。位拆裂使用固件觸發(fā)IO端口,一般可用于實現(xiàn)串行接口。如果要監(jiān)測端口以解碼串行數(shù)據(jù)的時候,也可以使用這種方法。無論是使用外部硬件還是位拆裂來實現(xiàn)接口,都會產生額外的設計成本。雖然增加外部硬件帶來的成本是明顯的,但使用軟件實現(xiàn)串行接口可能也會要求使用速度更快因而也更加昂貴的CPU。

大多數(shù)通用微控制器今天都支持SPI、UART和I2C接口,但仍然有很多時候,某些內部用戶可編程邏輯會非常有用。Atmel、賽普拉斯、Microchip和NXP等多家公司已經把部分用戶可定義邏輯添加到自己的部件上,用于修復部分此類問題。這些器件主要是帶附加邏輯的微控制器。CPU仍然是主要的處理器件,附加邏輯的作用是提高CPU的工作效率。這類器件常見于成本敏感性產品中,但也在低級任務中用作小型協(xié)處理器,以減輕主處理器的負擔,從而提升效率。

另一方面FPGA也正在朝著類似的目標前進,雖然是從另一個方向。賽靈思和Altera多年來一直在添加軟硬核處理器以創(chuàng)建片上系統(tǒng)。FPGA方法一般成本較高,但如果項目需要大量定制邏輯,這就是一種高成本效益的方法。這些器件對于構建ASIC、小批量產品的原型而言極具價值。這類應用的上市時間至關重要,而較大型產品需要持續(xù)的硬件靈活性。

微控制器搭配邏輯與FPGA搭配CPU,這兩種器件類型都能為現(xiàn)場提供硬件靈活性。一旦基于閃存的器件成為常規(guī),現(xiàn)場升級就會成為標準。最早設計人員只能夠升級固件,但現(xiàn)在硬件(邏輯)和固件都能夠在現(xiàn)場輕松實現(xiàn)升級。從計算機鼠標到高速網絡路由器等設備均能夠重新編寫設備的固件和硬件,從而進行現(xiàn)場升級。

上文提及的四家公司(Atmel、賽普拉斯、Microchip和NXP)均可提供“膠連”邏輯,幫助減輕主處理器的負荷,或是無需使用外部邏輯。就提供的邏輯模塊類型和這些邏輯模塊彼此互聯(lián)的方式以及與定時器、UART和IO引腳等板載模塊互聯(lián)的方式而言,每家公司都采取了不同的方法。

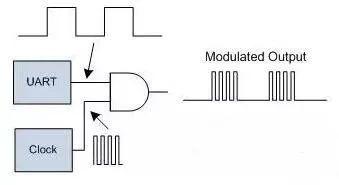

因此有必要了解這些廠家各自是如何實現(xiàn)內部可編程邏輯的,以便為選擇最適合自己項目的解決方案做出最佳決策。只要一個簡單的內部AND或者OR門控就足以避免使用外部組件,或是改善CPU性能。所有四種方法都支持用定制邏輯門控輸入和輸出信號。這類方法可借助時鐘門控輸入,以便使用計數(shù)器測量外部時鐘頻率。這四類邏輯模塊均支持的一個簡單例子是一種調制UART輸出,使之用于IR通信的方法。在此例中,不僅有下圖所示的內部AND門控,還能夠將來自時鐘或計數(shù)器的信號及UARTTX輸出路由到AND門控。

簡單調制的UART

簡單調制的UART

AtmelXMEGA定制邏輯(XCL)

AtmelXCL模塊內置兩個LUT(查找表)模塊,配套兩個8位定時器/計數(shù)器模塊。這兩個LUT不必連接到定時器/計數(shù)器模塊,而是與UART、EVENT模塊或IO引腳互聯(lián)。這兩個LUT可用作兩個獨立的2輸入單元或一個單獨的3輸入單元。該邏輯模塊可配置為組合邏輯,如AND、NAND、OR、NOR、XOR、XNOR、NOT或MUX功能。它們也可配置為順序邏輯功能,例如D觸發(fā)器、D鎖存器或RS鎖存器。由于能夠與其它邏輯模塊和IO引腳互聯(lián),這些簡單的LUT模塊能夠方便地讓設計人員避免使用某些外部邏輯,或者節(jié)省CPU周期。例如AtmelXCL模塊應用手冊(AT01084)解釋了如何配置XCL模塊,以避免在產生額外CPU開銷或使用外部邏輯的情況下,為UART輸出提供曼徹斯特編碼。AVRXMEGAE器件內置一個XCL模塊。

Atmel的XMEGA定制邏輯(XCL)

Microchip可配置邏輯單元(CLC)

MicrochipCLC允許用戶從八路輸入中選擇最多四個信號。這些輸入可以是兩個IO引腳、內部時鐘、外設或寄存器位的組合。這四個信號隨后路由到可編程邏輯模塊中。該邏輯模塊可編程為AND-OR、OR-XOR、4輸入AND、S-R鎖存器的8種組合之一,也可配置為4種其它觸發(fā)器組合之一。Microchip在其《可配置邏輯單元提示與技巧》應用手冊中給出了部分實例。其中的實例之一演示了如何配置這些模塊以解碼正交信號。在不使用這些額外的邏輯模塊情況下,CPU需要以高得多的速率采樣信號,才能避免正處于轉換階段的信號發(fā)生偽旋轉,讓CPU只被有效轉換中斷。MicrochipPIC10(L)F320/322器件每個都包含一個CLC模塊,而每個CLC模塊都包含四個下圖所示的模塊。

Microchip的可配置邏輯單元

NXP模式匹配引擎

NXP提供的用戶可配置邏輯被稱為模式匹配引擎。該邏輯模塊的輸入可選擇最大八個GPIO輸入。這八個輸入可為復雜的布爾表達生成乘積項。這些輸出可用于觸發(fā)中斷,驅動特殊IO引腳,或是路由到下一個邏輯模塊或slice。其它特性則支持上升或下降信號以及反相信號的邊緣檢測。該附加硬件經配置后,只有發(fā)生復雜(或簡單)事件組合時才中斷CPU。NXPLPC81x器件內置一個模式匹配引擎。

NXP引腳中斷/模式匹配引擎

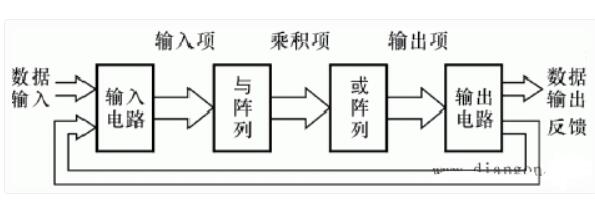

賽普拉斯PSoC通用數(shù)字模塊(UDB)

賽普拉斯通過使用通用數(shù)字模塊或UDB,采用更先進的方法在上文介紹的其他三個廠商的方法和FPGA之間獨樹一幟。一個UDB由兩個12C4PLD和一個數(shù)據(jù)通路構成。PLD可用于控制數(shù)據(jù)通路的操作和數(shù)據(jù)流,也可用作通用邏輯和狀態(tài)機。數(shù)據(jù)通路是一種能提供8位功能(AND、OR、ADD、SUB、INC、DEC、XOR)、移位功能(左和右)以及供數(shù)據(jù)排隊的兩個4字節(jié)FIFO的定制模塊。這些模塊也可以結合在一起提供16位、24位或32位功能。

UDB的輸入和輸出可路由到任何GPIO、外設/組件IO、中斷等。UDB、固定功能模擬和數(shù)字模塊以及GPIO之間的互聯(lián)都使用數(shù)字信號接口(DSI)處理。UDB經編程可實現(xiàn)為任何功能,包括從簡單的邏輯門到計數(shù)器和PWM以及UART和I2C外設等通用串行接口。

就利用UDB實現(xiàn)設計而言,用戶可以選擇多種選項。既可把簡單的邏輯門布局在原理圖中,也可在Verilog中實現(xiàn)設計。還可提供定制圖形界面,無需使用Verilog即可實現(xiàn)設計。PSoC3、PSoC4和PSoC5系列微控制器可包含4個到24個此類邏輯模塊(UDB)。

定制接口實例

最近我注意到Worldsemi生產的一些RGBLED很有意思。部件編號分別為WS2811、WS2812和WS2812B,但它們工作方式一致。只需要一個GPIO引腳,您就可以驅動1,000個或者更多的此類部件。這相當令人感興趣,因為我能夠用一個GPIO引腳控制如此大數(shù)量的RGBLED。連接這些LED的接口不是SPI、UART或I2C,而是定制接口。通信信號采用異步信號,每一位開始于上升沿。數(shù)據(jù)為1或0由下圖所示的高脈沖長度決定。

WS2811/12數(shù)據(jù)0/1時序

每個部件需要24位數(shù)據(jù),每一種顏色(紅、綠、藍)為下列格式的8位。

WS2811/12數(shù)據(jù)格式

WS2811/12部件采用DIN(數(shù)據(jù)輸入)和DOUT(數(shù)據(jù)輸出)信號,以便簡單地進行串行連接。每個部件都保留其看到的頭24位數(shù)據(jù),然后把剩余數(shù)據(jù)從DOUT引腳輸出,參見下圖。

連接多個WS2811/12部件

當數(shù)據(jù)流啟動后,每個部件將看到持續(xù)的數(shù)據(jù)流。如果數(shù)據(jù)信號的上升沿不超過50微秒,部件會鎖存數(shù)據(jù),將緊鄰的24位數(shù)據(jù)視為自己的數(shù)據(jù),并將其余數(shù)據(jù)重新發(fā)送出去。

正如您所看到的,其原理并不復雜,但它并不能輕松地適配到標準的微控制器硬件上。我確實發(fā)現(xiàn)有人使用SPI接口來維持時序,但這要求每個真實的數(shù)據(jù)位使用至少三個SPI數(shù)據(jù)位,對于通過位拆裂獲得CPU性能而言優(yōu)勢不大。由于時序并不嚴格,如果您在固件中實現(xiàn)接口(位拆裂),CPU將專門用于翻轉驅動信號直至LED全部更新。這意味著您需要禁用所有中斷,在整個過程中不對任何其它輸入做出響應。如果您有1,000個LED,則更新時間為(0.40微秒+0.85)24位1,000個LED=30,000微秒或30毫秒。這可能并不是什么問題,但如果您要以30Hz的頻率更新LED,將幾乎占用100%的CPU!

在編寫代碼時,我習慣于在不得不較長時間禁用中斷的地方避免阻塞代碼或條件,特別在系統(tǒng)中有用戶接口或是需要與其它處理器通信的情況下尤為如此。我的目的是盡量減輕CPU的負擔,讓硬件完成大部分工作,就如同今天常見的內部UART或SPI模塊所做的工作一樣。賽普拉斯PSoCUDB有幾項特性能讓這項工作變得非常簡便。每個UDB在數(shù)據(jù)通路中有兩個4字節(jié)FIFO和一個移位器。在實現(xiàn)UART時,您可將一個FIFO用作TX緩存,另一個用作RX緩存。對于WS2811/12,我只需要一個輸出FIFO和移位器。我決定配置硬件,為每個器件每次生成一次中斷。中斷處理器將加載24位(3字節(jié))數(shù)據(jù),直到FIFO為空時返回。采用這種方法,可以每30微秒中斷一次,而不必以150毫微秒或更短間隔禁用全部中斷和位拆裂。我決定使用的微控制器是賽普拉斯PSoCCY8C4245AXI。該微控制器大批量采購價格約為一美元,有四個UDB,運行頻率為48MHz,足以滿足此項工作所需的速度和硬件要求。

設計使用了PSoC提供的四個UDB中的兩個。一個用于使用FIFO緩沖數(shù)據(jù)和移位數(shù)據(jù),這樣每個器件的全部24位(3字節(jié))可一次性寫入。第二個UDB可使用兩個比較輸出創(chuàng)建PWM。一個比較輸出用于創(chuàng)建邏輯0,另一個用于創(chuàng)建邏輯1。該串行數(shù)據(jù)可用于控制數(shù)字多路復用器,選擇波形1或0。敬請參見下圖的方框圖。

WS2811/12接口使用PSoCUDB的方框圖

UDB中四個PLD(每個UDB有2個)的大多數(shù)乘積項可用于控制數(shù)據(jù)通路,生成中斷,提供狀態(tài)和控制功能,但這也使用了這種低成本微控制器中一半的UDB資源。

接下來的工作是明確這一附加硬件能為設計節(jié)省多少CPU開銷。以1,000個LED組成的陣列為例,其刷新頻率為30Hz。如果設計使用固件對接口進行位拆裂操作,會差不多占用100%的CPU資源。使用PSoC器件中的可編程硬件仍然可以做到每30微秒中斷一次,雖然這也是較重的負荷,但運行在48MHz的ARMCortex-M0足以應付。為測試CPU開銷,我創(chuàng)建了一個簡單的環(huán)路,以大約30Hz的頻率刷新顯示器。

在主環(huán)路中,我觸發(fā)了一個引腳,然后使用示波器計算40毫秒內的觸發(fā)數(shù)量。然后我禁用中斷,再次運行項目,并比較結果。與使用固件中的位拆裂造成的幾乎100%的CPU占用相比,持續(xù)顯示刷新只占用大約12%的CPU資源。這樣另外88%的CPU周期可用于外部通信和用戶界面。如果為設計添加DMA,該開銷可能會從12%下降到2%或更低。我使用的最廉價PSoC(約1美元)只包含UDB但未包含DMA,不過一些較大型的部件確實內置有DMA。

隨后我實際制作了一個由60x16個LED(960個LED)網格組成的真正RGBLED板,用于測試該組件。該組件的運行符合預期,可用作顯示基本的直線、矩形、圓圈以及文本的圖形界面。

0個RGBLED制作的廣告牌

無論是大型LED板還是簡單的定制界面,部分內部可編程硬件會給設計性能造成重大影響。不是每一種定制界面都需要多字節(jié)FIFO或全硬件狀態(tài)機,但擁有這種靈活性能為您提供更多設計選擇、提高性能,或是讓現(xiàn)有設計迅速適合產品需求。

審核編輯:劉清

-

微控制器

+關注

關注

48文章

7496瀏覽量

151085 -

mcu

+關注

關注

146文章

17019瀏覽量

350373 -

ROM

+關注

關注

4文章

562瀏覽量

85679 -

RAM

+關注

關注

8文章

1367瀏覽量

114541 -

可編程邏輯

+關注

關注

7文章

514瀏覽量

44074

發(fā)布評論請先 登錄

相關推薦

什么是可編程邏輯

可編程邏輯器件

可編程邏輯器件基礎及應用實驗指導書

什么是PLD(可編程邏輯器件)

可編程陣列邏輯構造_可編程邏輯器材的運用

可編程邏輯在MCU中起哪些關鍵作用?

可編程邏輯在MCU中起哪些關鍵作用?

評論