達(dá)拉斯半導(dǎo)體DS89C430超高速微控制器是一款每機(jī)器周期1時(shí)鐘的器件。DS89C430可直接替代舊的8051架構(gòu)設(shè)計(jì)。但是,必須評(píng)估內(nèi)存接口時(shí)序。本應(yīng)用筆記介紹了使用DS89C430微控制器時(shí)支持的五種總線模式。

介紹

超高速閃存微控制器系列,包括DS89C430和DS89C450,集成了獨(dú)特的每機(jī)器1時(shí)鐘周期內(nèi)核以及不同數(shù)量的閃存和內(nèi)部MOVX SRAM。雖然這使得設(shè)計(jì)一個(gè)沒有外部存儲(chǔ)器組件的完整系統(tǒng)成為可能,但某些應(yīng)用可能需要通過高速外部存儲(chǔ)器總線訪問額外的程序和/或數(shù)據(jù)存儲(chǔ)器。該系列中的器件支持多種內(nèi)存訪問模式,允許使用最慢(因此最便宜)的內(nèi)存器件以最快的速度運(yùn)行。

任何內(nèi)存系統(tǒng)的設(shè)計(jì)都依賴于任意數(shù)量的常識(shí)規(guī)則。始終保持高速地址線短,以盡量減少傳輸線效應(yīng)。通過最小化加載次數(shù)和/或使用緩沖區(qū),使任何內(nèi)存信號(hào)保持低負(fù)載。始終在微控制器、解復(fù)用鎖存器和存儲(chǔ)設(shè)備上使用足夠的去耦;在使用超高速微控制器進(jìn)行設(shè)計(jì)時(shí),這一點(diǎn)尤其重要。

這些規(guī)格假設(shè)指定信號(hào)的容性負(fù)載大致相等。但是,如果任何信號(hào)連接到額外的負(fù)載,則應(yīng)在關(guān)鍵路徑分析中使用額外的裕量,并選擇適當(dāng)?shù)拇鎯?chǔ)器速度。對(duì)于其他非常規(guī)器件,在設(shè)計(jì)評(píng)估中確認(rèn)其他重要的時(shí)序參數(shù)(例如寫入激活前的數(shù)據(jù)設(shè)置)可能是明智的。緩沖器可用于最大程度地減少總線負(fù)載過重的影響。

本應(yīng)用筆記有助于系統(tǒng)架構(gòu)師選擇正確的存儲(chǔ)器類型和速度,以滿足其設(shè)計(jì)標(biāo)準(zhǔn)。本文討論了各種外部存儲(chǔ)器尋址模式的設(shè)計(jì)建議和時(shí)序考慮因素。本應(yīng)用筆記中的計(jì)算基于編寫時(shí)的最佳數(shù)據(jù)。請(qǐng)查看相應(yīng)的數(shù)據(jù)手冊(cè),了解任何器件的最新信息。

總線模式

當(dāng)與外部存儲(chǔ)器接口時(shí),架構(gòu)師必須選擇五種支持的總線模式之一,每種模式都會(huì)對(duì)外部存儲(chǔ)器時(shí)序產(chǎn)生重大影響。每種總線模式使用連接到P0和P2的內(nèi)存信號(hào)的不同配置。各種新模式(頁面模式)允許外部存儲(chǔ)器接口以不同的速度運(yùn)行,幾乎所有模式都比標(biāo)準(zhǔn)8051存儲(chǔ)器接口方案更快。速度改進(jìn)主要是通過重新排列微控制器的外部總線結(jié)構(gòu)來實(shí)現(xiàn)的,使得地址LSB和數(shù)據(jù)總線與存儲(chǔ)器器件具有直接(即,不通過鎖存器)連接。這意味著,保存在 '373 鎖存器中的地址 MSB 僅在地址跨 256 字節(jié)邊界轉(zhuǎn)換時(shí)才需要更新。一旦 MSB 被鎖定,內(nèi)存訪問將以最快的速度(頁面點(diǎn)擊)執(zhí)行。在邊界交叉(頁面未命中)期間更新地址鎖存器時(shí),尋呼模式會(huì)產(chǎn)生 2 個(gè)周期的損失,但在其他方面比傳統(tǒng)的 8051 架構(gòu)運(yùn)行得更快。

大多數(shù)應(yīng)用程序?qū)⑹褂梅琼撁婺J剑榱伺c傳統(tǒng) 8051 兼容)或頁面模式 1,1 周期(為了盡可能快的速度)。這些總線通常在完成的應(yīng)用程序中硬連線,不會(huì)動(dòng)態(tài)變化。總線模式如下:

非頁面模式

頁面模式 1(1 周期)

頁面模式 1(2 周期)

頁面模式 1(4 周期)

頁面模式 2

請(qǐng)注意,頁面模式操作是通過軟件啟用的。這意味著為了利用任何頁面模式,必須首先從內(nèi)部閃存開始執(zhí)行并啟用頁面模式操作。這是因?yàn)槲⒖刂破髟谌魏沃刂煤竽J(rèn)為非頁面模式。

非頁面模式

圖 1 顯示了傳統(tǒng)的 8051 內(nèi)存接口方案,也稱為非頁面模式。微控制器的端口 2 顯示地址的 A15-A8,而端口 0 顯示 A7-0 或數(shù)據(jù) D7-D0,具體取決于正在執(zhí)行內(nèi)存周期的哪個(gè)部分。這是微控制器復(fù)位后的默認(rèn)模式。在本例中,程序中和數(shù)據(jù)存儲(chǔ)器設(shè)備都包含在系統(tǒng)中。該系列的成員通過多路復(fù)用總線與外部存儲(chǔ)器接口,以減少引腳數(shù)。因此,需要具有最小傳播延遲的外部鎖存器(如74ACQ373或74ACQ573)來解復(fù)用存儲(chǔ)器的地址和/或數(shù)據(jù)信號(hào)。鎖存器的內(nèi)容在每個(gè)存儲(chǔ)器周期都會(huì)發(fā)生變化,因此必須仔細(xì)選擇類型和邏輯系列,因?yàn)槠鋫鞑パ舆t位于外部存儲(chǔ)器接口的關(guān)鍵時(shí)序路徑中。

圖1.非頁面模式內(nèi)存接口。

該模式下的外部存儲(chǔ)器時(shí)序幾乎與DS4C87的每機(jī)器周期520時(shí)鐘相同。在此模式下,沒有頁面遺漏或點(diǎn)擊。無論拉伸周期設(shè)置如何,內(nèi)部閃存或SRAM訪問都需要一個(gè)系統(tǒng)時(shí)鐘周期,外部MOVC或代碼提取需要四個(gè)系統(tǒng)時(shí)鐘周期。外部 MOVX 操作至少需要四個(gè)系統(tǒng)時(shí)鐘周期。

頁面模式 1(1 周期)

這是最快的外部尋址模式。在這種模式下,內(nèi)部代碼獲取只需一個(gè)時(shí)鐘周期。由于地址MSB被鎖存,允許數(shù)據(jù)和地址LSB直接連接到存儲(chǔ)設(shè)備,因此可以提高速度。在頁面未命中期間插入一個(gè)額外的周期,以便有時(shí)間使用新地址 MSB 更新閂鎖。此模式的 2 周期和 4 周期版本類似于頁面模式 1(1 周期),不同之處在于擴(kuò)展了外部存儲(chǔ)器操作以適應(yīng)速度較慢的設(shè)備。本文檔中有關(guān)選擇程序和數(shù)據(jù)存儲(chǔ)器訪問速度的部分假定頁面命中周期,因?yàn)樗软撁嫖疵兄芷诟烨腋P(guān)鍵。頁面命中次數(shù)的計(jì)時(shí)計(jì)算也適用于頁面未命中。

圖2.頁面模式 1 內(nèi)存接口。

頁面模式 2

這種外部尋址模式將地址MSB和數(shù)據(jù)多路復(fù)用在P2上,并將地址的LSB放在P0上。此總線配置僅提高外部代碼獲取的速度,因此外部 MOVX 訪問的時(shí)間與非頁面模式相同。

圖3.頁面模式 2 內(nèi)存接口。

選擇程序存儲(chǔ)器訪問速度

該微控制器設(shè)計(jì)用于連接典型的程序存儲(chǔ)器技術(shù),如EPROM、閃存或SRAM。在選擇存儲(chǔ)器件時(shí),必須考慮下面討論的幾個(gè)關(guān)鍵的交流時(shí)序特性。特定器件的選擇通常是一個(gè)迭代過程,需要兼顧成本、可用性和存儲(chǔ)器的時(shí)序參數(shù),這些參數(shù)由微控制器的工作頻率決定。下表將存儲(chǔ)設(shè)備時(shí)序規(guī)格與其微控制器對(duì)應(yīng)項(xiàng)相關(guān)聯(lián)。表中使用的系統(tǒng)時(shí)鐘頻率是外部時(shí)鐘頻率乘以任何晶體乘法因子,即啟用10倍乘法器的2MHz外部時(shí)鐘頻率將具有20MHz的系統(tǒng)時(shí)鐘頻率。所有時(shí)序都是常見頻率的示例;其他頻率的精確值可以使用數(shù)據(jù)手冊(cè)中給出的公式計(jì)算。頁面模式的計(jì)時(shí)假定頁面命中,這是時(shí)間最關(guān)鍵的序列。通常,存儲(chǔ)器時(shí)序參數(shù)必須小于相應(yīng)的微控制器值才合適。

1. 從有效地址訪問內(nèi)存的時(shí)間。在微控制器中,這通常是阿維夫,在存儲(chǔ)設(shè)備中它是行政協(xié)調(diào)會(huì)或 t機(jī) 管 局.此參數(shù)表示存儲(chǔ)設(shè)備解碼 16 位地址并將數(shù)據(jù)放在數(shù)據(jù)總線上所需的時(shí)間。根據(jù)模式的不同,關(guān)鍵時(shí)序取決于端口 0 或端口 2。對(duì)于非尋頁模式,D7-0和A7-0在端口0上的多路復(fù)用意味著必須將鎖存器的傳播延遲添加到公式中。這要求存儲(chǔ)器比相應(yīng)的微控制器時(shí)序規(guī)格略快。

表 1.t阿維夫計(jì)時(shí)

|

System Clock (MHz) |

tCLCL (ns) |

Non-Page tAVIV* |

Page Mode 1 (1-cycle) tAVIV2 |

Page Mode 1 (2-cycle) tAVIV2 |

tAVIV2 |

Page Mode 2 tAVIV2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 68.91 | 10.30 | 25.45 | 55.76 | 23.45 |

| 25 | 40.00 | 98.00 | 20.00 | 40.00 | 80.00 | 38.00 |

| 11.0592 | 90.42 | 249.27 | 70.42 | 115.63 | 206.06 | 113.63 |

| 5 | 200.00 | 578.00 | 180.00 | 280.00 | 480.00 | 278.00 |

*減去地址鎖存器的傳播延遲以獲得準(zhǔn)確的t行政協(xié)調(diào)會(huì)對(duì)于內(nèi)存設(shè)備。

2. 從輸出啟用內(nèi)存的訪問時(shí)間有效。在微控制器中,這通常是普利夫,在存儲(chǔ)設(shè)備中它是OE.此參數(shù)表示芯片從禁用狀態(tài)激活其輸出所需的時(shí)間。在大多數(shù)存儲(chǔ)器配置中,/PSEN信號(hào)用作外部程序存儲(chǔ)器器件的輸出使能信號(hào)。在芯片使能激活之前,必須存在有效地址,此參數(shù)才有效。

表 2.t普利夫計(jì)時(shí)

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 40.61 | 10.30 | 10.30 | 40.61 | 10.30 |

| 25 | 40.00 | 60.00 | 20.00 | 20.00 | 60.00 | 20.00 |

| 11.0592 | 90.42 | 160.84 | 70.42 | 72.42 | 160.84 | 70.42 |

| 5 | 200.00 | 380.00 | 180.00 | 180.00 | 380.00 | 180.00 |

3. 數(shù)據(jù)浮點(diǎn)(總線釋放)時(shí)間。此參數(shù)表示輸出使能信號(hào)取消置位后內(nèi)存設(shè)備繼續(xù)驅(qū)動(dòng)總線的時(shí)間量。此參數(shù)在非尋呼模式和尋呼模式 2 中很重要,因?yàn)樵诿總€(gè)周期內(nèi),總線必須在數(shù)據(jù)和地址之間切換。這可能是高系統(tǒng)時(shí)鐘速度下的關(guān)鍵參數(shù),設(shè)計(jì)人員應(yīng)確保東風(fēng)始終小于微控制器參數(shù) tPXIZ.

表 3.tPXIZ計(jì)時(shí)

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 25.30 | N/A | N/A | N/A | 25.30 |

| 25 | 40.00 | 35.00 | N/A | N/A | N/A | 35.00 |

| 11.0592 | 90.42 | 85.42 | N/A | N/A | N/A | 85.42 |

| 5 | 200.00 | 195.00 | N/A | N/A | N/A | 195.00 |

存儲(chǔ)設(shè)備的信號(hào)時(shí)序因設(shè)備類型而異。內(nèi)存器件時(shí)序的典型采樣如下所示。

表 4.對(duì)各種內(nèi)存技術(shù)的關(guān)鍵內(nèi)存時(shí)序參數(shù)進(jìn)行采樣

| K6R1008C1C (SRAM) | -10 | -15 | -20 |

| tACC | 10 | 15 | 20 |

| tOE | 5 | 7 | 9 |

| tOHZ / tDF | 5 | 7 | 9 |

| M27C1001-35 (EPROM) | -35 | -45 | -60 |

| tACC | 35 | 45 | 60 |

| tOE | 25 | 25 | 30 |

| tOHZ / tDF | 25 | 25 | 30 |

| AM29F010B-45(閃存) | -45 | -70 | -90 |

| tACC | 45 | 70 | 90 |

| tOE | 25 | 30 | 35 |

| tOHZ / tDF | 10 | 15 | 20 |

將這些設(shè)備與上面顯示的時(shí)間進(jìn)行比較,可以選擇合適的存儲(chǔ)設(shè)備。作為一般經(jīng)驗(yàn)法則,來自有效地址的訪問時(shí)間通常是關(guān)鍵時(shí)序參數(shù),但建議系統(tǒng)設(shè)計(jì)人員驗(yàn)證所有存儲(chǔ)器時(shí)序參數(shù)。下圖顯示了存儲(chǔ)設(shè)備的相對(duì)訪問速度。一般來說,SRAM需要以33MHz的頻率運(yùn)行外部代碼,但低于25MHz的EPROM或閃存技術(shù)就可以了。

圖4.內(nèi)存類型的訪問時(shí)間的表示。

使用總線模式提高系統(tǒng)性能

盡管尋呼模式 1, 1 周期是最快的外部尋址模式,但在某些情況下,利用其他尋呼模式之一可以提高整體系統(tǒng)速度。這些情況涉及在同一設(shè)計(jì)中使用內(nèi)部和外部程序存儲(chǔ)器。假設(shè)系統(tǒng)設(shè)計(jì)人員希望使用頁面模式 1、1 周期總線以最大速度運(yùn)行微控制器,但使用非易失性(閃存 EPROM)存儲(chǔ)器。一項(xiàng)調(diào)查將顯示,EPROM的最快訪問時(shí)間為35ns,這將限制最大系統(tǒng)時(shí)鐘速度為25MHz。

另一種方法是對(duì)軟件進(jìn)行分段,并將最需要時(shí)間的部分降級(jí)到內(nèi)部存儲(chǔ)器中。然后使用較慢的總線模式之一(如頁面模式 1、2 周期或 4 周期)連接到外部存儲(chǔ)器。然后,微控制器可以以其最大系統(tǒng)時(shí)鐘頻率運(yùn)行;內(nèi)部代碼執(zhí)行將全速進(jìn)行,不經(jīng)常發(fā)生的外部訪問將以稍慢的速度執(zhí)行。這允許系統(tǒng)同時(shí)以最快的速度運(yùn)行內(nèi)部和外部代碼。

選擇數(shù)據(jù)存儲(chǔ)器訪問速度

數(shù)據(jù)存儲(chǔ)器接口類似于程序存儲(chǔ)器接口,不同之處在于使用/RD和/WR信號(hào)。下表將存儲(chǔ)設(shè)備時(shí)序規(guī)格與其微控制器對(duì)應(yīng)項(xiàng)相關(guān)聯(lián)。表中使用的系統(tǒng)時(shí)鐘頻率是外部時(shí)鐘頻率乘以任何晶體乘法器因子,例如,啟用10倍乘法器的2MHz外部時(shí)鐘頻率將具有20MHz的系統(tǒng)時(shí)鐘頻率。所有時(shí)序都是常見頻率的示例;其他頻率的精確值可以使用數(shù)據(jù)手冊(cè)中給出的公式計(jì)算。

拉伸周期功能允許微控制器自動(dòng)延長(zhǎng)或拉伸外部數(shù)據(jù)存儲(chǔ)器 (MOVX) 訪問,以適應(yīng)較慢的外部存儲(chǔ)器和外設(shè)。當(dāng)微控制器用于升級(jí)速度較慢的傳統(tǒng)基于 8051 的系統(tǒng)時(shí),這一點(diǎn)尤其重要。此外,還有各種存儲(chǔ)器映射外設(shè),如LCD顯示器或UART,它們的速度不夠快,無法跟上微控制器的步伐。無論拉伸周期設(shè)置如何,內(nèi)部 MOVX 和 MOVC 操作始終以 1 時(shí)鐘周期執(zhí)行。

此設(shè)備系列的所有成員默認(rèn)對(duì) MOVX 指令使用一個(gè)拉伸循環(huán)。為了獲得最大速度,應(yīng)用軟件可以寫入某些特殊功能寄存器 (SFR) 位,并使 MOVX 指令以零拉伸周期運(yùn)行。拉伸周期在相應(yīng)的數(shù)據(jù)手冊(cè)和超高速閃存微控制器用戶指南中有更詳細(xì)的介紹。下表假定拉伸值為零,允許外部數(shù)據(jù)存儲(chǔ)器以最快的速度運(yùn)行。

1. 從有效地址訪問內(nèi)存的MOVX時(shí)間。在微控制器中,這通常是tAVDV,而在存儲(chǔ)設(shè)備中,它通常是行政協(xié)調(diào)會(huì).此參數(shù)表示存儲(chǔ)設(shè)備解碼 16 位地址并將數(shù)據(jù)放在數(shù)據(jù)總線上所需的有限時(shí)間。根據(jù)模式的不同,關(guān)鍵時(shí)序取決于端口 0 或端口 2。對(duì)于非尋頁模式,D7-0和A7-0在端口0上的多路復(fù)用意味著必須將鎖存器的傳播延遲添加到公式中。這要求 tAVDV 略小于 t行政協(xié)調(diào)會(huì).

表 6.tAVDVx計(jì)時(shí)

|

System Clock (MHz) |

tCLCL (ns) |

Non-Page tAVDV* |

Page Mode 1 (1-cycle) tAVDV2 |

Page Mode 1 (2-cycle) tAVDV2 |

Page Mode 1 (4-cycle) tAVDV2 |

Page Mode 2 tAVDV0 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 70.91 | 10.30 | 25.45 | 86.06 | 70.91 |

| 25 | 40.00 | 100.00 | 20.00 | 40.00 | 120.00 | 100.00 |

| 11.0592 | 90.42 | 251.27 | 70.42 | 115.63 | 296.48 | 251.27 |

| 5 | 200.00 | 580.00 | 180.00 | 280.00 | 680.00 | 580.00 |

*減去地址鎖存器的傳播延遲以獲得準(zhǔn)確的t行政協(xié)調(diào)會(huì)對(duì)于內(nèi)存設(shè)備。

2. 從輸出啟用內(nèi)存的訪問時(shí)間有效。在微控制器中,這通常是RLDV,在存儲(chǔ)設(shè)備中它是OE.此參數(shù)表示存儲(chǔ)設(shè)備從禁用狀態(tài)激活其輸出所需的時(shí)間。在MOVX操作中,/RD信號(hào)用作外部程序存儲(chǔ)器器件的輸出使能信號(hào)。在芯片使能激活之前,必須存在有效地址,此參數(shù)才有效。

表 7.tRLDV計(jì)時(shí)

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 42.61 | 12.30 | 12.30 | 42.61 | 42.61 |

| 25 | 40.00 | 62.00 | 22.00 | 22.00 | 62.00 | 62.00 |

| 11.0592 | 90.42 | 162.84 | 72.42 | 72.42 | 162.84 | 162.84 |

| 5 | 200.00 | 382.00 | 182.00 | 182.00 | 382.00 | 382.00 |

3. /RD和/WR脈沖寬度。此參數(shù)表示置位/RD和/WR選通的時(shí)間量。在微控制器中,這通常是RLRH或 t哇??.此參數(shù)很重要,因?yàn)镾RAM對(duì)這些參數(shù)具有最低規(guī)格,必須在高速下保證。

表 8.tRLRH/ 噸哇??計(jì)時(shí)

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 55.61 | 25.30 | 25.30 | 55.61 | 55.61 |

| 25 | 40.00 | 75.00 | 35.00 | 35.00 | 75.00 | 75.00 |

| 11.0592 | 90.42 | 175.84 | 85.42 | 85.42 | 175.84 | 175.84 |

| 5 | 200.00 | 395.00 | 195.00 | 195.00 | 395.00 | 395.00 |

4.數(shù)據(jù)浮動(dòng)(總線釋放)時(shí)間。此參數(shù)表示輸出使能信號(hào)取消置位后內(nèi)存設(shè)備繼續(xù)驅(qū)動(dòng)總線的時(shí)間量。此參數(shù)在非尋呼模式和尋呼模式 2 中很重要,因?yàn)樵诿總€(gè)周期內(nèi),總線必須在數(shù)據(jù)和地址之間切換。這可能是高系統(tǒng)時(shí)鐘速度下的關(guān)鍵參數(shù),設(shè)計(jì)人員應(yīng)確保東風(fēng)始終小于微控制器參數(shù) tPXIZ.

表 9.t熱療計(jì)時(shí)

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 25.30 | N/A | N/A | N/A | 25.30 |

| 25 | 40.00 | 35.00 | N/A | N/A | N/A | 35.00 |

| 11.0592 | 90.42 | 85.42 | N/A | N/A | N/A | 85.42 |

| 5 | 200.00 | 195.00 | N/A | N/A | N/A | 195.00 |

由于程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器訪問具有相似的時(shí)序(未選擇拉伸周期時(shí)),因此表5提供了頁面模式(1周期)和常見微控制器頻率的非頁面模式的各種系統(tǒng)時(shí)鐘頻率所需的MOVX存儲(chǔ)器訪問時(shí)序的便捷摘要。這是選擇數(shù)據(jù)存儲(chǔ)設(shè)備的良好起點(diǎn)。

-

微控制器

+關(guān)注

關(guān)注

48文章

7489瀏覽量

151047 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163605 -

總線

+關(guān)注

關(guān)注

10文章

2867瀏覽量

87987

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DS89C450問題。

DS89C430, DS89C440, DS89C450中文

DS89C430-DS89C450.pdf

DS89C430/S89C450 pdf datasheet

從高速微控制器系列向超高速閃存微控制器的升級(jí)

使用DS89C450作為靜態(tài)LCD顯示屏控制器

使用免費(fèi)的SDCC C編譯器開發(fā)DS89C430/450系列

Keil C編譯器的使用與DS89C430/450

DS89C430/DS89C450超高速閃存微控制器存儲(chǔ)器接

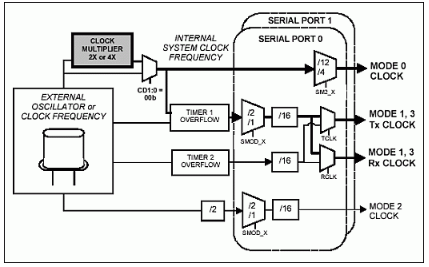

超高速微控制器硬件串口能力增強(qiáng)-Ultra High Spe

超高速閃存微控制器軟件SPI

將Keil μVision調(diào)試器與DS89C4x0配合使用

使用超高速閃存微控制器實(shí)現(xiàn)快速內(nèi)存?zhèn)鬏?/a>

使用DS89C450作為靜態(tài)LCD顯示控制器

超高速微控制器硬件增強(qiáng)串口功能

DS89C430/DS89C450超高速閃存微控制器存儲(chǔ)器接口時(shí)序

DS89C430/DS89C450超高速閃存微控制器存儲(chǔ)器接口時(shí)序

評(píng)論